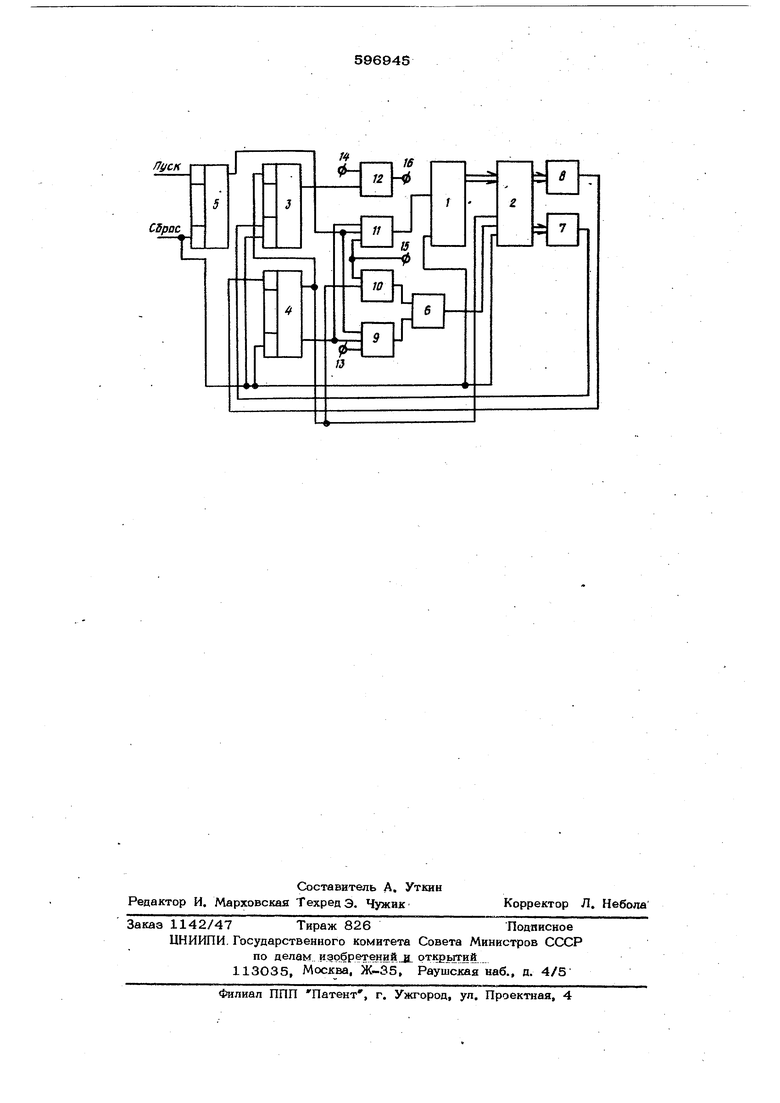

Изобретение относится к автоматике и вьгаислительной технике и может использоваться для деления двух частотных сигналов. Известны частотные делительные устрой ства, содержащие схему пересчета, распределитель, блок хранения результата, схему перезаписи, счетчик, элементы И, ИЛИ, триггер, пересчетную декаду и генератор тактовых импульсов ij. Известно .также устройство, содержащее два счетчика: триггеры, элементы И, ИЛИ, группы элементов И, причем единичный выход перво1 о и второго триггеров соединены соответственно с первьгми входами первого второго и третьего элементов И, первая управляющая шина соединена с единичным входом первого триггера, а вторая управляющая шина - с нулевыми входами первого, второго и третьего триггеров, с первь ми входами первого и второго счетчиков. Целью изобретения является упрощение устройства. Для этого в устройстве единичный вход второго триггера соединен с единичным выходом третьего триггера, второй вход первого элемента И соединен с первой шиной, а выход является вьгходом устройства, (второй вход второго элемента И соединен с нулевым выходом третьего триггера и вторым входом третьего элемента И, вторая входная шина устройства соединена с третьим и первым входами второго и четвертого элементов И, второй вход четвертого элемента И соединен с нулевым выходом третьего триггера, третья входная шина соединена с третьим входом третьего элемента IJ, выход которого соединен с первь1м входом элемента ИЛИ, второй вход которого соединен с выходом четвертого элемента И, второй вход первого счетчика соединен с выходом второго элементе И, а выход - с информационным входом второго счетчика, второй вход которого соединен с вьпсодом элемента ИЛИ, а третий - с единичным выходом третьего триггера, первая группа информационных выходов второго счетчика соединена со входами элементов И первой группы, а вторая группа информационных выходов - со входами элементов И второй группы, выходьт элементов И первой и второй группы соецинены соответственно с ециничньм и нулевыч-: входом третьего и второго триггеро fi.-i чертеже показана структурная схема предлагаемого устройства. Устройство содержит счетчики 1 и 2, триггеры 3-5, элемент МЛ И 6, группы элементов И 7, 8, элементы И 9-12. Исходное состяние устройства определяе ря подачей импульсов Сброс, при этом счетчики 1 и 2 устанавливаются в нулевое состояние, триггер 3 подает запрещающий потенциал на элемент И 12, триггер 5 запрещает прохождение сигналов на вьтход элементов И 9 и 11. С приходом импульса Пуск триггер 5 устанавливается в положение, при котором импульсы опорного сиг нала частоты f2 через элемент И 11 поступают на счетный вход счетчика 1, а импульсы сигнала частоты -f, через элемент И , 9 и элемент ИЛИ 6 подаются на счетный Вход счетчика 2. Оба счетчика ра ботают на сложение. При установлении в счетчике 2 некоторого заданного числа N на вьгходе группы элементов И S появляется потенциал, который устанавливает три гер 4 в состояние. При этом состоянии триггер 4 подает запрещающий сигнал на элементы И 9, 11, производит запись обратного счетчика 1 в счетчик 2, подает разрешающий потенциал на элемент И 1О, устанавливает триггер 3 в другое состояни Триггер 3 разрешает прохождение сигналов частоты .f на выход элемента И 12. Дл счатчика 1 при этом справедливо равенств , U) где NJ- число импульсов, находящихся в счетчике 1; t - время поступления импульсов в счетчик. Для счетчика 2 ,можно записать выражениеN .(2) После этого на счетный вход счетчика через элемент И 10 и элемент ИЛИ 6 поступают импульсы частоты |, а на выход элемента И 12 импульсы частоты . При переполнении счетчика 2 группа элементов И 7 вырабатывает потенциал, устанавливающий триггер 3 в другое состояние при этом он подает запрещающий сигнал на элемент И 12. Для счетчика 2 справедливо равенство (1). На выход же устройства поступает число импульсов, равное .С5) Учитывая уравнения (1) и (2), выражение (3) можно записать следующим образом Jfi Nii Так как К является постоянной величиной, то число импульсов, поступающих на устройства, прямо пропорционально частному от деления сигнала частоты fj на сигнал частот f. , которое поступает последовательно во времени. Формула изобретения Частотное делительное устройство, содержащее два счетчика, Триггеры, элементы И, ИЛИ, группы элементов И, причем единичный выход первого и второго триггеров соединены соответственно с первьми входами первого, второго и третьего элементов И, первая управляющая шина соединена с единичным входом первого триггера, а вторая управляющая шина - с нулевыми входами первого, второго и третьего триггеров, е первыми входами первого и второго счетчиков, отличающееся тем, что, с целью упрощения устуойства, Б нем единичньгй вход второго триггера соединен с единичным выходом третьего триггера, второй вход первого элемента И соединен с первой входной шиной, а выход является выходом устройства, второй вход второго элемента И соединен с нулевым выходом третьего триггера и вторым входом третьего элемента И, вторая входная, шина устройства соединена с третьим к первым входами второго и нетвертого элементов И, второй вход четвертого элемента И соединен с нулевым выходом третьего триггера, третья входная шина соединена с третьим входом третьего элемента И, выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с вь1ходом четвертого элемента И, второй вход первого счетчика соединен с выходом второго элемента И, выход - с информационным входом второго счетчика, второй вход которого соединен с вьгходом элемента ИЛИ, а третий - с единичным выходом третьего триггера, первая группа информационньк выходов второго счетчика соединена со входами элементов И первой группы, а вторая группа информационных выходов - со входами элементов И второй группы, выходы элементов И первой и второй группы соединены соответственно с единичным и нулевьпу входом третьего и второго триггеров. Источники информации, принятые во внимание при экспертизе: 1.Авторское свидетельство СССР № 474005, кл. ОгОб F 7/52, 1975. 2.Авторское свидетельство СССР № 363О96, кл. G-06 G-7/16, 197О.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство задержки сигналов | 1983 |

|

SU1091306A2 |

| Многоканальное устройство для контроля параметров | 1987 |

|

SU1444714A1 |

| Преобразователь частоты в код | 1988 |

|

SU1797159A1 |

| Цифровой дискриминатор средней частоты | 1985 |

|

SU1293835A1 |

| Устройство для определения первой разности частотно-импульсного сигнала | 1982 |

|

SU1043675A1 |

| Устройство для измерения частоты и периода | 1991 |

|

SU1824592A1 |

| Измерительный прибор | 1989 |

|

SU1661653A1 |

| Способ измерения среднеквадратических значений переменных сигналов | 1990 |

|

SU1798705A1 |

| Устройство для перебора сочетаний | 1986 |

|

SU1397936A2 |

| Устройство для сбора и передачи информации | 1984 |

|

SU1221675A1 |

Авторы

Даты

1978-03-05—Публикация

1976-02-16—Подача