Изобретение откосится к электрическим измерениям и может быть использовано при построении высокоточных измерительных приборов.

Цель изобретения - повышение точности измерений среднеквадратического значения напряжения.

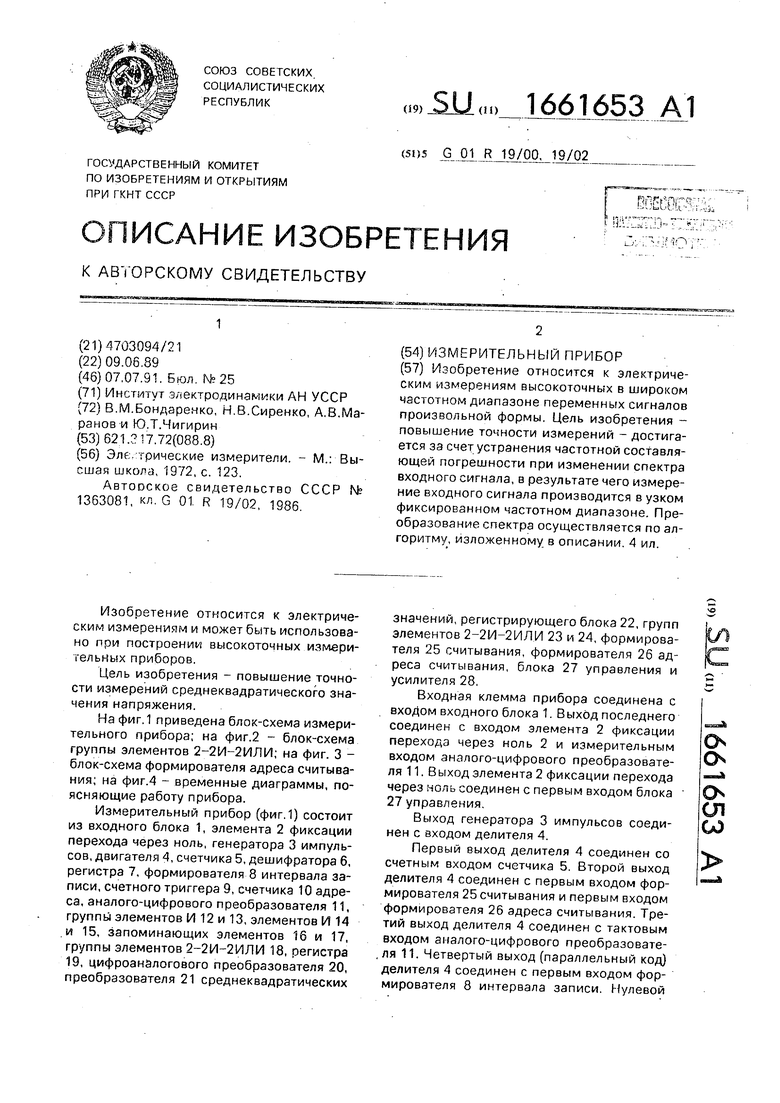

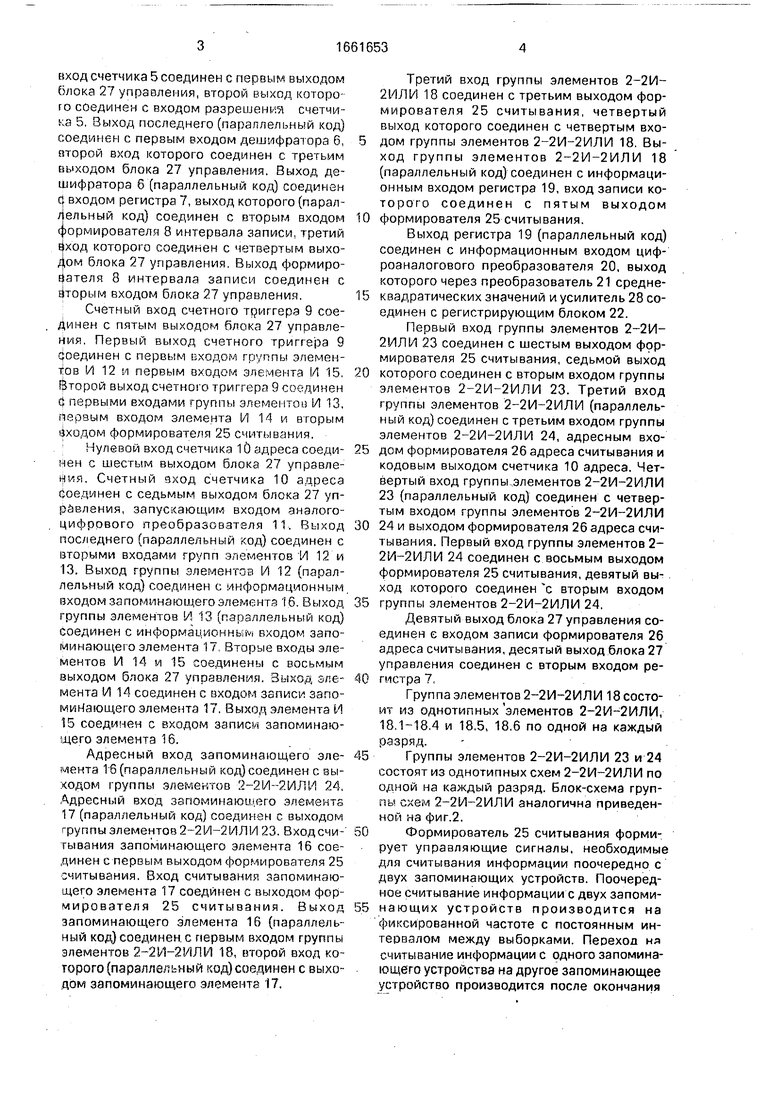

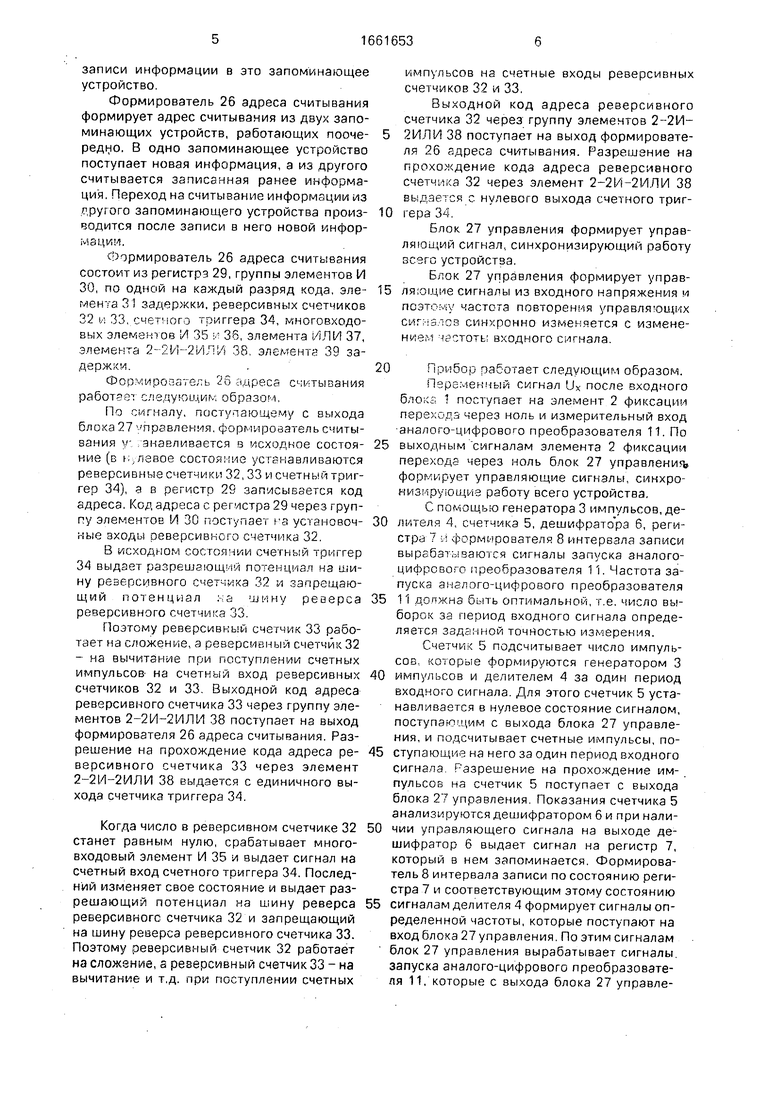

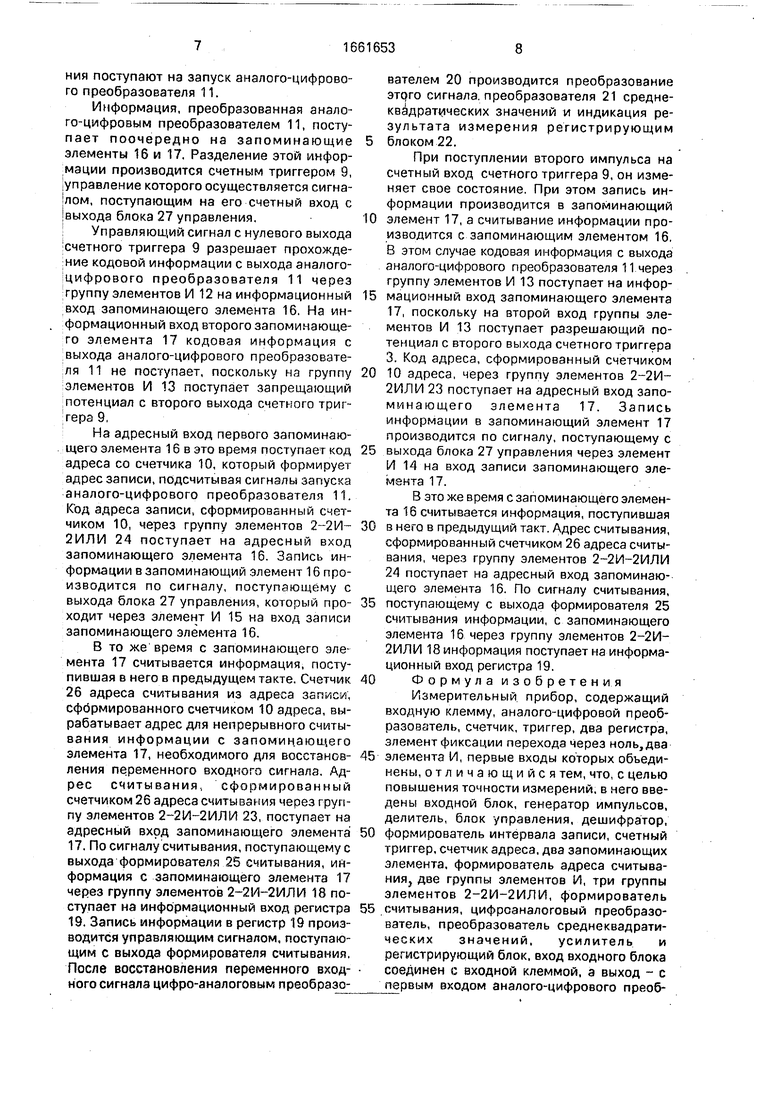

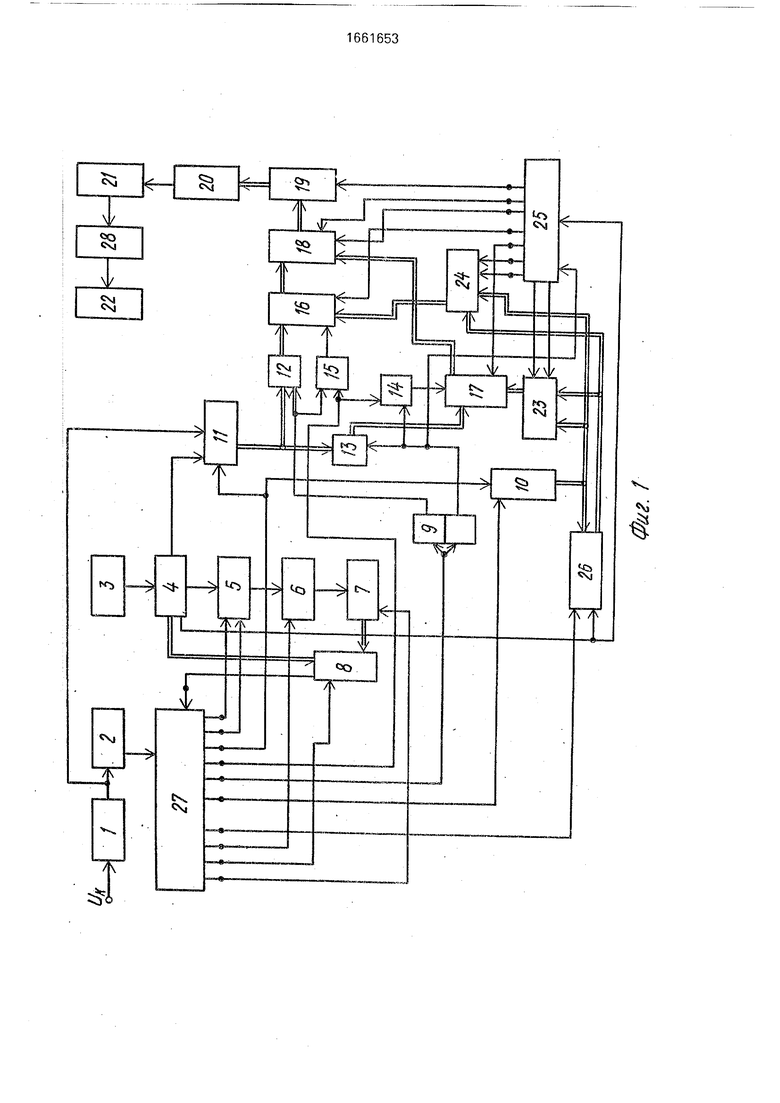

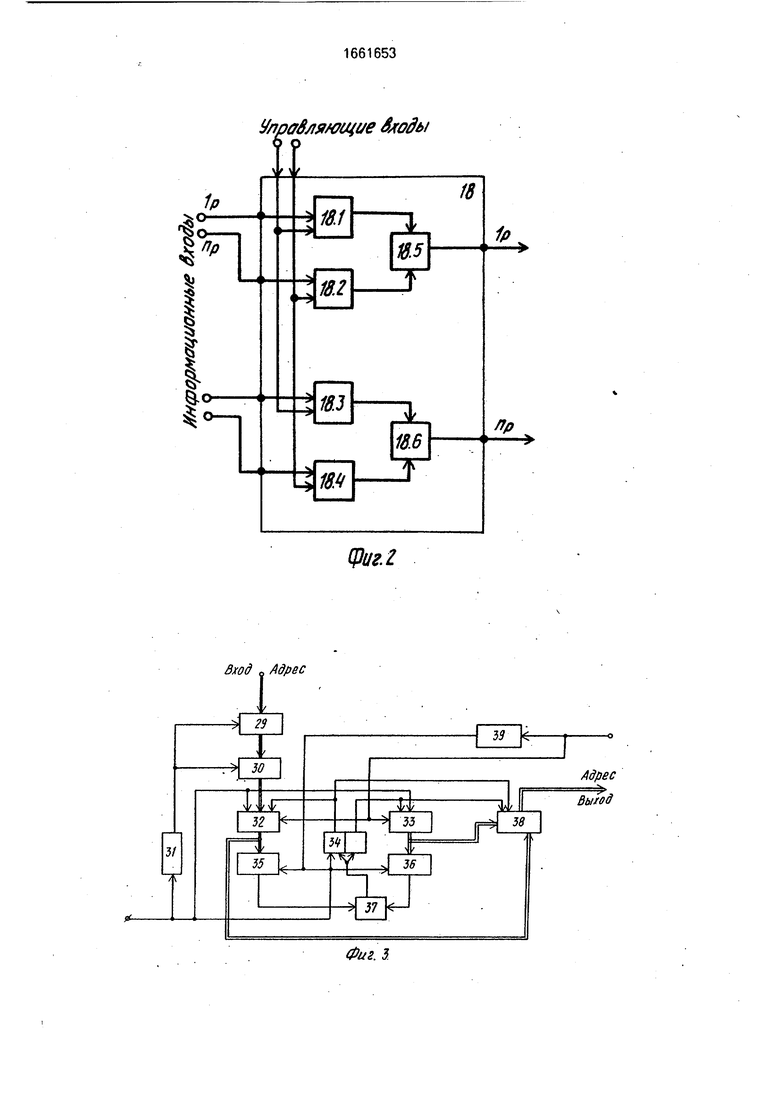

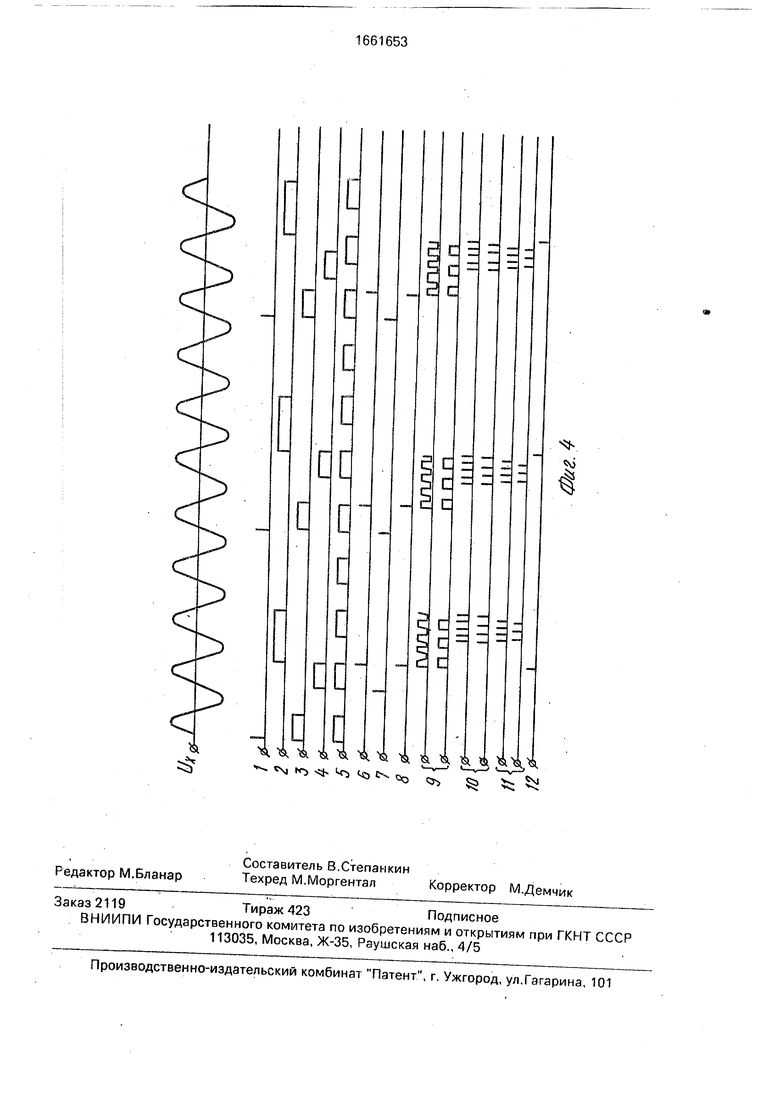

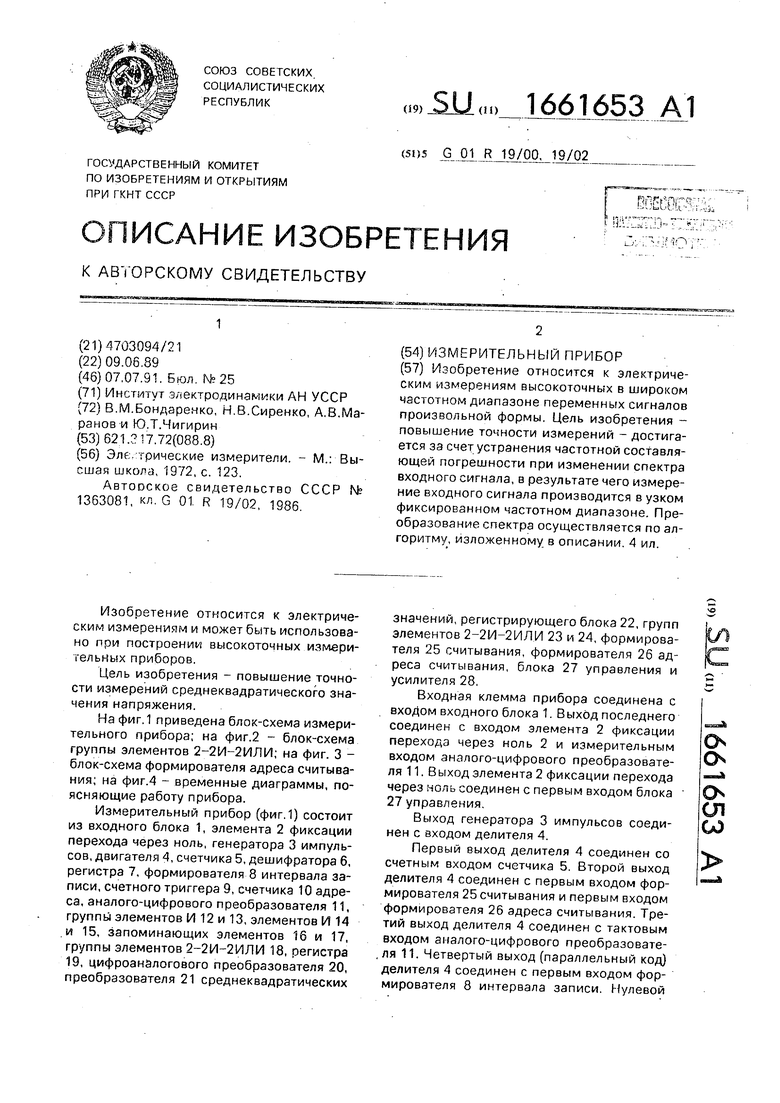

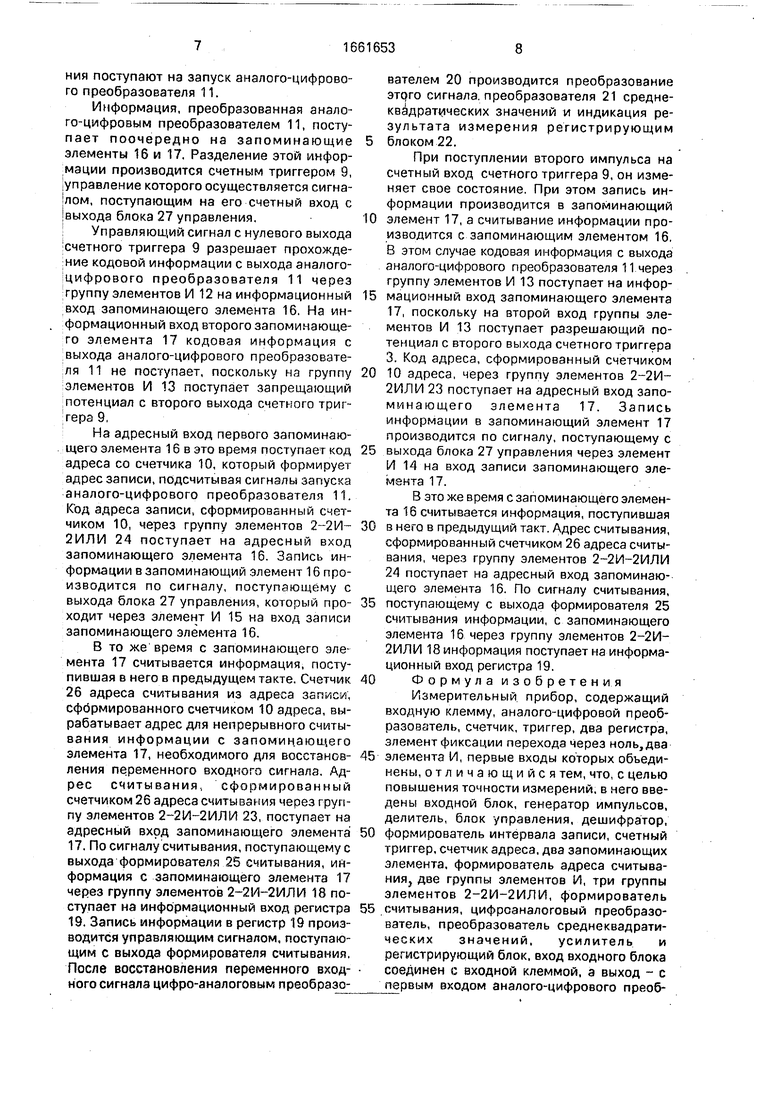

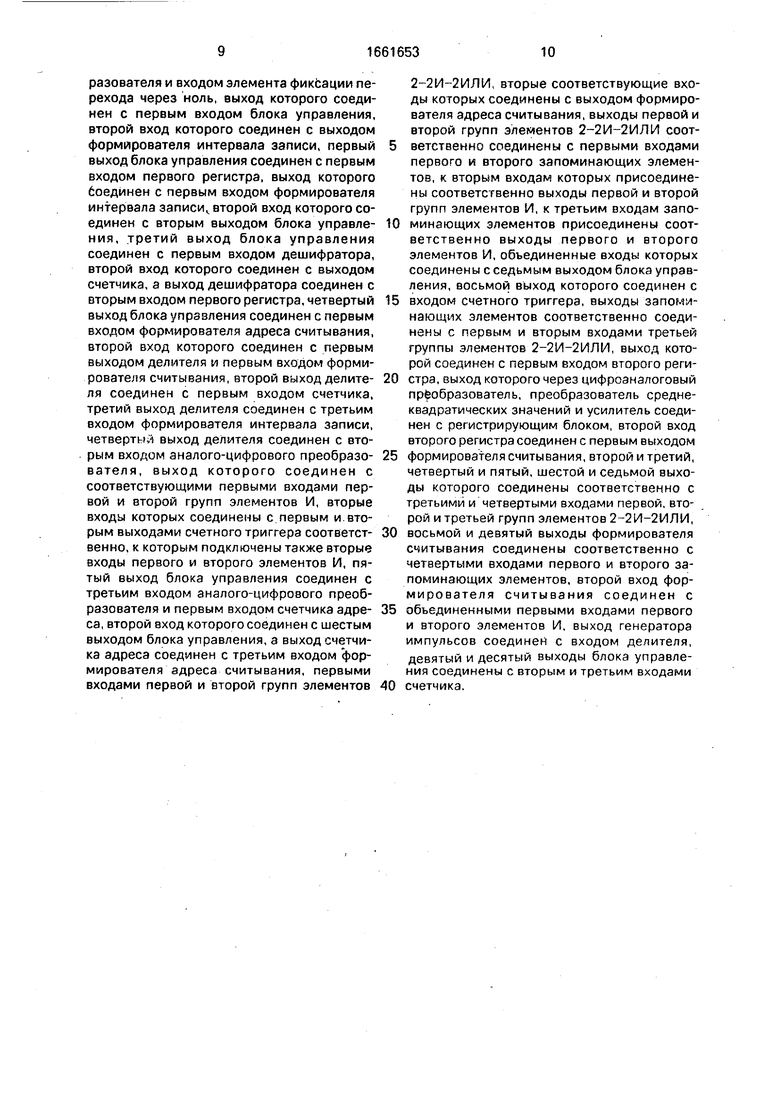

На фиг.1 приведена блок-схема измерительного прибора; на фиг.2 - блок-схема группы элементов 2-2И-2ИЛИ; на фиг. 3 - блок-схема формирователя адреса считывания; на фиг.4 - временные диаграммы, поясняющие работу прибора.

Измерительный прибор (фиг.1) состоит из входного блока 1, элемента 2 фиксации перехода через ноль, генератора 3 импульсов, двигателя 4, счетчика 5, дешифратора 6, регистра 7, формирователя 8 интервала записи, счетного триггера 9, счетчика 10 адреса, аналого-цифрового преобразователя 11, группы элементов И 12 и 13, элементов И 14 и 15, запоминающих элементов 16 и 17, группы элементов 2-2И-2ИЛИ 18, регистра 19, цифроаналогового преобразователя 20, преобразователя 21 среднеквадратических

значений, регистрирующего блока 22, групп элементов 2-2И-2ИЛИ 23 и 24, формирователя 25 считывания, формирователя 26 адреса считывания, блока 27 управления и усилителя 28,

Входная клемма прибора соединена с входом входного блока 1. Выход последнего соединен с входом элемента 2 фиксации перехода через ноль 2 и измерительным входом аналого-цифрового преобразователя 11. Выход элемента 2 фиксации перехода через ноль соединен с первым входом блока 27 управления.

Выход генератора 3 импульсов соединен с входом делителя 4.

Первый выход делителя 4 соединен со счетным входом счетчика 5. Второй выход делителя 4 соединен с первым входом формирователя 25 считывания и первым входом формирователя 26 адреса считывания. Третий выход делителя 4 соединен с тактовым входом аналого-цифрового преобразовате- , ля 11. Четвертый выход (параллельный код) делителя 4 соединен с первым входом формирователя 8 интервала записи. Нулевой

О

о

СП

ы

вход счетчика 5 соединен с первым выходом блока 27 управления, второй выход которого соединен с входом разрешения счетчика 5. Выход последнего (параллельный код) соединен с первым входом дешифратора 6, второй вход которого соединен с третьим Е ЫХОДОМ блока 27 управления. Выход дешифратора 6 (параллельный код) соединен с| входом регистра 7, выход которого (парал- /|ельный код) соединен с вторым входом формирователя 8 интервала записи, третий Eixofl которого соединен с четвертым выходом блока 27 управления. Выход формирователя 8 интервала записи соединен с вторым входом блока 27 упрапления.

Счетный вход счетного триггера 9 соединен с пятым выходом блока 27 управления. Первый выход счетного триггера 9 Соединен с первым сходом группы элементов И 12 -л первым входом элемента И 15. Е&торой выход счетно о триггера 9 соединен 4 первыми входами группы элементов И 13, пеозым входом элемента И 14 и вторым входом формирователя 25 считывания.

Нулевой вход счетчика 10 адреса соединен с шестым выходом блока 27 управления. Счетный эход счетчика 10 адреса Соединен с седьмым выходом блока 27 управления, запускающим входом аналого- цифрового преобразователя 11. Выход последнего (параллельный код) соединен с вторыми входами групп элементов И 12 и 13. Выход группы элементов И 12 (параллельный код) соединен с информационным входом запоминающего элемента 16. Выход группы элементов И 13 (параллельный код) Соединен с информационном входом запоминающе о элемента 17 Вторые входы элементов И 14 и 15 соединены с восьмым выходом блока 27 управления. Выход элемента И 14 соединен с входом записи запоминающего элемента 17. Выход элемента И 15 соединен с входом записи запоминающего элемента 16.

Адресный вход запоминающего элемента 16 (параллельный код)соединен с вы- кодом группы элементов 2-2И--2ИЛИ 24, Адресный вход запоминающего элемента 17 (параллельный код) соединен с выходом группы элементов 2-2И-2ИЛИ 23. Вход считывания запоминающего элемента 16 соединен с первым выходом формирователя 25 считывания. Вход считывания запоминающего элемента 17 соединен с выходом формирователя 25 считывания. Выход запоминающего элемента 16 (параллельный код) соединен с первым входом группы элементов 2-2И-2ИЛИ 18. второй вход которого (параллельный код) соединен с выходом запоминающего элемента 17.

Третий вход группы элементов 2-2И- 2МЛИ 18 соединен с третьим выходом формирователя 25 считывания, четвертый выход которого соединен с четвертым входом группы элементов 2-2И-2ИЛИ 18. Выход группы элементов 2-2И-2ИЛИ 18 (параллельный код) соединен с информационным входом регистра 19, вход записи которого соединен с пятым выходом

0 формирователя 25 считывания.

Выход регистра 19 (параллельный код) соединен с информационным входом циф- роаналогового преобразователя 20, выход которого через преобразователь 21 средне5 квадратических значений и усилитель 28 соединен с регистрирующим блоком 22.

Первый вход группы элементов 2-2И- 2ИЛИ 23 соединен с шестым выходом формирователя 25 считывания, седьмой выход

0 которого соединен с вторым входом группы элементов 2-2И-2ИЛИ 23. Третий вход группы элементов 2-2И-2ИЛИ (параллельный код) соединен с третьим входом группы элементов 2-2И-2ИЛИ 24, адресным вхо5 дом формирователя 26 адреса считывания и кодовым выходом счетчика 10 адреса. Четвертый вход группы элементов 2-2И-2ИЛИ 23 (параллельный код) соединен с четвертым входом группы элементов 2-2И-2ИЛИ

0 24 и выходом формирователя 26 адреса счи- тывания. Первый вход группы элементов 2- 2И-2ИЛИ 24 соединен с восьмым выходом формирователя 25 считывания, девятый выход которого соединен с вторым входом

5 группы элементов 2-2И-2ИЛИ 24.

Девятый выход блока 27 управления соединен с входом записи формирователя 26 адреса считывания, десятый выход блока 27 управления соединен с вторым входом ре0 гистра 7,

Группа элементов 2-2И-2ИЛИ 18 состоит из однотипных элементов 2-2И-2ИЛИ, 18,1-18,4 и 18.5, 18.6 по одной на каждый разряд.

5 Группы элементов 2-2И-2ИЛИ 23 и 24 состоят из однотипных схем 2-2И-2ИЛИ по одной на каждый разряд. Блок-схема груп- ПУ схем 2-2И-2ИЛИ аналогична приведенной на фиг.2,

0Формирователь 25 считывания формирует управляющие сигналы, необходимые для считывания информации поочередно с двух запоминающих устройств. Поочередное считывание информации с двух запоми5 нающих устройств производится на фиксированной частоте с постоянным интервалом между выборками. Переход ня считывание информации с одного запоминающего устройства на другое запоминающее устройство производится после окончания

записи информации в это запоминающее устройство.

Формирователь 26 адреса считывания формирует адрес считывания из двух запоминающих устройств, работающих поочередно, В одно запоминающее устройство поступает новая информация, а из другого считывается записанная ранее информация. Переход на считывание информации из другого запоминающего устройства производится после записи в него новой информации.

Формирователь 26 адреса считывания состоит из регистра 29, группы элементов И 30, по одной на каждый разряд кода, элемента 3 1 задержки, реверсивных счетчиков 32 и 33, счетмого триггера 34, многовходо- вых элементов (Л 35 36, элемента ИЛИ 37, элемента 2-2И-2ИЛV 38, элементе 39 задержки.

Формирователь 26 здреса считывания работг Т следующие, образом,

По сигналу, поступающему с выхода блока 27 . правления, формирователь считывания V анавливается в исходное состояние (в ь..левое состояние устанавливаются реверсивные счетчики 32,33 и счетный триггер 34), а в регистр 29 записывается код адреса. Код адреса с регистра 29 через группу элементов И 30 поступает гз установочные входы реверсивного счетчика 32.

В исходном состоянии счетный триггер 34 выдает разрешающий потенциал на шину реверсивного счетчика 32 и запрещающий потенциал ьа шину реверса реверсивного счетчика 33.

Поэтому реверсивный счетчик 33 работает на сложение, а реверсивный счетчик 32 - на вычитание при поступлении счетных импульсов- на счетный вход реверсивных счетчиков 32 и 33. Выходной код адреса реверсивного счетчика 33 через группу элементов 2-2И-2ИЛИ 38 поступает на выход формирователя 26 адреса считывания. Разрешение на прохождение кода адреса реверсивного счетчика 33 через элемент 2-2И-2ИЛИ 38 выдается с единичного выхода счетчика триггера 34.

Когда число в реверсивном счетчике 32 станет равным нулю, срабатывает много- входовый элемент И 35 и выдает сигнал на счетный вход счетного триггера 34. Последний изменяет свое состояние и выдает разрешающий потенциал на шину реверса реверсивного счетчика 32 и запрещающий на шину реверса реверсивного счетчика 33. Поэтому реверсивный счетчик 32 работает на сложение, а реверсивный счетчик 33 - на вычитание и т.д. при поступлении счетных

импульсов на счетные входы реверсивных счетчиков 32 и 33.

Выходной код адреса реверсивного счетчика 32 через группу элементов 2-2И- 5 2ИЛИ 38 поступает на выход формирователя 26 адреса считывания. Разрешение на прохождение кода адреса реверсивного счетчика 32 через элемент 2-2И-2ИЛИ 38 выдается с нулевого выхода счетного триг- 10 гера 34.

Блок 27 управления формирует управляющий сигнал, синхронизирующий работу всего устройства.

Блок 27 управления формирует управ- 15 ляющие сигналы из входного напряжения м поэтому частота повторения управляющих сигналов синхронно изменяется с изменением - УСТОТЬ; входного сигнала.

0Прибор работает следующим образом.

Переменный сигнал Ux после входного блока 1 поступает на элемент 2 фиксации перехода через ноль и измерительный вход аналого-цифрового преобразователя 11. По 5 выходным сигналам элемента 2 фиксации перехода через ноль блок 27 управления формирует управляющие сигналы, синхронизирующие работу всего устройства,

С помощью генератора 3 импульсов, де- 0 лителя 4, счетчика 5, дешифратора 6, регистра 7 i . формирователя 8 интервала записи вырабатываются сигналы запуска аналого- цифрового преобразователя 11. Частота запуска аналого-цифрового преобразователя 5 11 должна быть оптимальной, т.е. число выборок за период входного сигнала определяется заданной точностью измерения.

Счетчик 5 подсчитывает число импульсов, которые формируются генератором 3 0 импульсов и делителем 4 за один период входного сигнала. Для этого счетчик 5 устанавливается в нулевое состояние сигналом, поступающим с выхода блока 27 управления, и подсчитывает счетные импульсы, по- 5 ступающие на него за один период входного сигнала. Разрешение на прохождение импульсов на счетчик 5 поступает с выхода блока 27 управления. Показания счетчика 5 анализируются дешифратором 6 и при нали- 0 чип управляющего сигнала на выходе дешифратор 6 выдает сигнал на регистр 7, который в нем запоминается. Формирователь 8 интервала записи по состоянию регистра 7 и соответствующим этому состоянию 5 сигналам делителя 4 формирует сигналы определенной частоты, которые поступают на вход блока 27 управления. По этим сигналам блок 27 управления вырабатывает сигналы, запуска аналого-цифрового преобразователя 11, которые с выхода блока 27 управления поступают на запуск аналого-цифрового преобразователя 11.

Информация, преобразованная аналого-цифровым преобразователем 11, поступает поочередно на запоминающие элементы 16 и 17. Разделение этой информации производится счетным триггером 9, управление которого осуществляется сигна- лом, поступающим на его счетный вход с выхода блока 27 управления.

Управляющий сигнал с нулевого выхода счетного триггера 9 разрешает прохождение кодовой информации с выхода аналого- цифрового преобразователя 11 через группу элементов И 12 на информационный вход запоминающего элемента 16. На информационный вход второго запоминающего элемента 17 кодовая информация с выхода аналого-цифрового преобразователя 11 не поступает, поскольку на группу элементов И 13 поступает запрещающий потенциал с второго выхода счетного триггера 9,

На адресный вход первого запоминающего элемента 16 в это время поступает код адреса со счетчика 10, который формирует адрес записи, подсчитывая сигналы запуска аналого-цифрового преобразователя 11. Код адреса записи, сформированный счетчиком 10, через группу элементов 2-2И- 2ИЛИ 24 поступает на адресный вход запоминающего элемента 16. Запись информации в запоминающий элемент 16 производится по сигналу, поступающему с выхода блока 27 управления, который проходит через элемент И 15 на вход записи запоминающего элемента 16.

В то же время с запоминающего элемента 17 считывается информация, поступившая в него в предыдущем такте. Счетчик 26 адреса считывания из адреса записи, сфбрмированного счетчиком 10 адреса, вырабатывает адрес для непрерывного считывания информации с запоминающего элемента 17, необходимого для восстановления переменного входного сигнала. Адрес считывания сформированный счетчиком 26 адреса считывания через группу элементов 2-2И-2ИЛИ 23, поступает на адресный вход запоминающего элемента 17. По сигналу считывания, поступающему с выхода формирователя 25 считывания, информация с запоминающего элемента 17 через группу элементов 2-2И-2ИЛИ 18 поступает на информационный вход регистра 19. Запись информации в регистр 19 производится управляющим сигналом, поступающим с выхода формирователя считывания, После восстановления переменного входного сигнала цифро-аналоговым преобразователем 20 производится преобразование этрго сигнала преобразователя 21 средне- квадратуческих значений и индикация результата измерения регистрирующим

блоком 22.

При поступлении второго импульса на счетный вход счетного триггера 9, он изменяет свое состояние. При этом запись информации производится в запоминающий

0 элемент 17, а считывание информации производится с запоминающим элементом 16. В этом случае кодовая информация с выхода аналого-цифрового преобразователя 11 через группу элементов И 13 поступает на инфор5 мационный вход запоминающего элемента 17, поскольку на второй вход группы элементов И 13 поступает разрешающий потенциал с второго выхода счетного триггера 3. Код адреса, сформированный счетчиком

0 10 адреса, через группу элементов 2-2И- 2ИЛИ 23 поступает на адресный вход запоминающего элемента 17. Запись информации в запоминающий элемент 17 производится по сигналу, поступающему с

5 выхода блока 27 управления через элемент И 14 на вход записи запоминающего элемента 17.

В это же время с запоминающего элемента 16 считывается информация, поступившая

0 в него в предыдущий такт. Адрес считывания, сформированный счетчиком 26 адреса считывания, через группу элементов 2-2И-2ИЛИ 24 поступает на адресный вход запоминающего элемента 16. По сигналу считывания,

5 поступающему с выхода формирователя 25 считывания информации, с запоминающего элемента 16 через группу элементов 2-2И- 2ИЛИ 18 информация поступает на информационный вход регистра 19.

0 Формула изобретения

Измерительный прибор, содержащий входную клемму, аналого-цифровой преобразователь, счетчик, триггер, два регистра, элемент фиксации перехода через ноль, два

5 элемента И, первые входы которых объединены, отличающийся тем, что, с целью повышения точности измерений, в него введены входной блок, генератор импульсов, делитель, блок управления, дешифратор,

0 формирователь интервала записи, счетный триггер, счетчик адреса, два запоминающих элемента, формирователь адреса считыва- ния две группы элементов И, три группы элементов 2-2И-2ИЛИ, формирователь

5 считывания, цифроаналоговый преобразователь, преобразователь среднеквадрати- ческих значений, усилитель и регистрирующий блок, вход входного блока соединен с входной клеммой, а выход - с первым входом аналого-цифрового преобразователя и входом элемента фиксации перехода через ноль, выход которого соединен с первым входом блока управления, второй вход которого соединен с выходом формирователя интервала записи, первый выход блока управления соединен с первым входом первого регистра, выход которого соединен с первым входом формирователя интервала записи второй вход которого соединен с вторым выходом блока управле- ния, третий выход блока управления соединен с первым входом дешифратора, второй вход которого соединен с выходом счетчика, а выход дешифратора соединен с вторым входом первого регистра, четвертый выход блока управления соединен с первым входом формирователя адреса считывания, второй вход которого соединен с первым выходом делителя и первым входом формирователя считывания, второй выход делите- ля соединен с первым входом счетчика, третий выход делителя соединен с третьим входом формирователя интервала записи, четвертый выход делителя соединен с вторым входом аналого-цифрового преобразо- вателя, выход которого соединен с соответствующими первыми входами первой и второй групп элементов И, вторые входы которых соединены с первым и вторым выходами счетного триггера соответст- венно, к которым подключены также вторые входы первого и второго элементов И, пятый выход блока управления соединен с третьим входом аналого-цифрового преобразователя и первым входом счетчика адре- са, второй вход которого соединен с шестым выходом блока управления, а выход счетчика адреса соединен с третьим входом формирователя адреса считывания, первыми входами первой и второй групп элементов

2-2И-2ИЛИ, вторые соответствующие входы которых соединены с выходом формирователя адреса считывания, выходы первой и второй групп элементов 2-2И-2ИЛИ соответственно соединены с первыми входами первого и второго запоминающих элементов, к вторым входам которых присоединены соответственно выходы первой и второй групп элементов И, к третьим входам запоминающих элементов присоединены соответственно выходы первого и второго элементов И, объединенные входы которых соединены с седьмым выходом блока управления, восьмой выход которого соединен с входом счетного триггера, выходы запоминающих элементов соответственно соединены с первым и вторым входами третьей группы элементов 2-2И-2ИЛИ, выход которой соединен с первым входом второго регистра, выход которого через цифроэналоговый преобразователь, преобразователь средне- квадратических значений и усилитель соединен с регистрирующим блоком, второй вход второго регистра соединен с первым выходом формирователя считывания, второй и третий, четвертый и пятый, шестой и седьмой выходы которого соединены соответственно с третьими и четвертыми входами первой, второй и третьей групп элементов 2-2И-2ИЛИ, восьмой и девятый выходы формирователя считывания соединены соответственно с четвертыми входами первого и второго запоминающих элементов, второй вход формирователя считывания соединен с объединенными первыми входами первого и второго элементов И, выход генератора импульсов соединен с входом делителя, девятый и десятый выходы блока управления соединены с вторым и третьим входами счетчика.

фцг.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения среднеквадратического значения сигнала | 1989 |

|

SU1728808A1 |

| Способ измерения среднеквадратических значений переменных сигналов | 1990 |

|

SU1798705A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Устройство для ретрансляции речевых сигналов | 1990 |

|

SU1830627A1 |

| Полевая телеметрическая сейсмическая станция | 1986 |

|

SU1327031A2 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР | 2000 |

|

RU2208836C2 |

| Многоканальный фотометр | 1987 |

|

SU1492224A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1986 |

|

SU1377894A1 |

| Мажоритарное декодирующее устройство | 1986 |

|

SU1372627A1 |

Изобретение относится к электрическим измерениям высокоточных в широком частотном диапазоне переменных сигналов произвольной формы. Цель изобретения - повышение точности измерений - достигается за счет устранения частотной составляющей погрешности при изменении спектра входного сигнала, в результате чего измерение входного сигнала производится в узком фиксированном частотном диапазоне. Преобразование спектра осуществляется по алгоритму, изложенному в описании. 4 ил.

Вход 0 Адрес

Фиг. 3

| Эле грические измерители | |||

| - М.: Высшая школа, 1972, с | |||

| Устройство для разметки подлежащих сортированию и резанию лесных материалов | 1922 |

|

SU123A1 |

| Устройство для измерения среднеквадратического значения напряжения | 1986 |

|

SU1363081A1 |

Авторы

Даты

1991-07-07—Публикация

1989-06-09—Подача