Изобретение относится к цифровой измерительной технике и может найти применение при построении преобразователей аналоговых величин в числовые эквиваленты с промежуточным преобразованием время (фазовый сдвиг) - код.

Известны также преобразователи, у которых имеется дополнительный делитель частоты, выходные сигналы которого сдвигаются относительно сигналов опорного делителя в специально предназначенном режиме работы на время равное начальному сдвигу фазы выходных сигналов фильтра, а выходная информация определяется опросом дополнительного делителя частоты I

Наиболее близким техническим решением к данному преобразователю является преобразователь, содержащий кварцевый генератор, один из выходов которого подключен к входу фазируемого делителя частоты и через последовательно соединенные опорные делитель частоты и фильтр непосредственно к первому входу ключа и через датчик угла ко второму входу ключа, выход формирователя меандра соединен с одним из входов синхронизатора, другой вход кварцевого генератора соединен с другим входом синхронизатора, выход которого соединен с одними входами двух элементов И, коммутатор режимов одним из выходов подключен к другому входу первого элемента И и входу ключа, а другим выходом подключен к другому входу второго элемента И, выход которого подключен к одному из входов регистра, кодовые выходы фазируемого делителя частоты подключены ко входам регистра 2.

Однако оно обладает весьма существенным недостатком заключающимся в том, что сбой работы делителя частоты может привести к значительным искажениям выходной информации.

0 Целью изобретения является повышение помехозащищенности и надежности преобразователя.

Поставленная цель достигается тем, что в преобразователь угла поворота в код введены фазовращатель, элемент ИЛИ и группы элементов И, дополнительные синхронизатор, регистр и элементы И, вход фазовращателя соединен с выходом ключа, а выход -с входом формирователя меандра, входы дополнительного синхронизатора соединены со входом синхро д низатора и выходом опорного делителя частоты, и с первыми входами дополнительных первого и второго элементов И, второй вход первого дополнительного элемента И соединен с другим входом коммутатора, первыми входами группы элементов И и с установочными входами стар5 ших разрядов фазируемого делителя частоты.

выход первого дополнительного элемента И соединен с одним из входов элемента ИЛИ, другой вход элемента ИЛИ соединен с выходом первого элемента И, а выход соединен с управляющим входом фазируемого делителя, второй вход второго дополнительного элемента И соединен с одним из выходов коммутатора, а выход - с управляющим входом дополнительного регистра, установочные входы которого соединены с кодовыми выходами младших разрядов фазируемого делителя, а выходы дополнительного регистра через группу элементов И соединены с установочными входами младших разрядов фазируемого делителя.

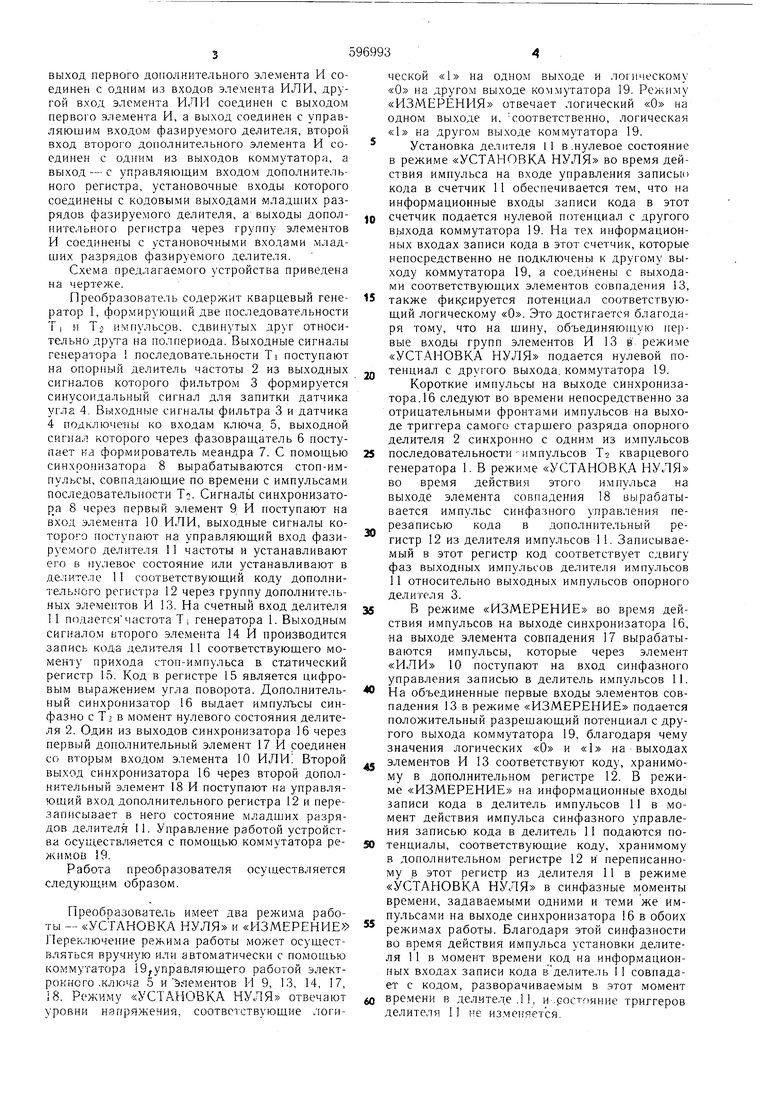

Схема предлагаемого устройства приведена на чертеже.

Преобразователь содержит кварцевый генератор 1, формируюший две носледовательности ТI и Tj импульсов, сдвинутых друг относительно друта на пол периода. Выходные сигналы генератора последовательности Ti поступают на опорный делитель частоты 2 из выходных сигналов которого фильтром 3 фор.мируется синусоидальный сигнал для запитки датчика угла 4. Выходные сигналы фильтра 3 и датчика 4 подключе-иы ко входам ключа 5, выходной сигнал которого через фазовращатель 6 поступает ка формирователь меандра 7. С помощью синхронизатора 8 вырабатываются стоп-импульсы, совпадающие по времени с импульсами последовательности Т. Сигналы синхронизатора 8 через первый элемент 9. И поступают на вход элемента 10 ИЛИ, выходные сигналы которого поступают на управляющий вход фазируемого делителя 11 частоты и устанавливают его в нулевое состояние или устанавливают в делителе 11 соответствующий коду дополнительного регистра 12 через группу дополнительных элементов И 13, На счетный вход делителя 1 1 подаетсячастота Ti генератора 1. Выходным сигнало.м второго элемента 14 И производится запись кода делителя 11 соответствующего моменту прихода стон-импульса в ст.атический регистр 15. Код в регистре 15 является цифровым выражением угла поворота. Дополнительный синхронизатор 16 выдает импульсы синфазно с Т) в момент нулевого состояния делителя 2. Один из выходов синхронизатора 16 через первый дополнительный элемент 17 И соединен со вторым входом элемента 10 ИЛИ Второй выход синхронизатора 16 через второй дополнительный элемент 18 И поступают на управляющий вход дополнительного регистра 12 и перезаписывает в него состояние младших разрядов делителя 11. Управление работой устройства осуществляется с помощью коммутатора режимов 19.

Работа преобразователя осуществляется следующим образом.

Преобразователь имеет два режима работы - «УСТАНОВКА НУЛЯ и «ИЗМЕРЕНИЕ Переключение реж,и,1а работы может осуществляться вручную или автоматически с помощью коммутатора 19,управляющего работой электронного .ключа 5 иЭлементов И 9, 13, 14, 17, 18. Режиму «УСТАНОВКА НУЛЯ отвечают уровни нзпря.жения, соответствующие логической «Ь на одном выходе и логическому «О на другом выходе коммутатора 19. Режиму «ИЗМЕРЕНИЯ отвечает логический «О на одном выходе и, соответственно, логическая «1 на другом выходе коммутатора 19. Установка делителя 11 в .нулевое состояние

в режиме «УСТАНОВКА НУЛЯ во время действия импульса на входе управления записью кода в счетчик 1I обеспечивается тем, что на информационные входы записи кода в этот

0 счетчик подается нулевой потенциал с другого выхода коммутатора 19. На тех информационных входах записи кода в этот счетчик, которые непосредственно не подключены к другому выходу коммутатора 19, а соединены с выходами соответствующих элементов совпадения 13,

5 также фиксируется потенциал соответствующий логическому «О. Это достигается благодаря тому, что на шину, объединяющую не()вые входы групп элементов И 13 в режиме «УСТАНОВКА НУЛЯ подается нулевой по тенциал с другого выхода, коммутатора 19.

Короткие импульсы на выходе синхронизатора. 16 следуют во времени непосредственно за отрицательными фронтами импульсов на выходе триггера самого старшего разряда опорного делителя 2 синхронно с одним из импульсов

5 последовательности-импульсов Т кварцевого генератора 1. В режиме «УСТАНОВКА НУЛЯ во время действия этого импульса на выходе элемента совпадения 18 вырабатывается импульс синфазного управления перезаписью кода в дополнительный регистр 12 из делителя импульсов 11. Записываемый в этот регистр код соответствует сдвигу фаз выходных импульсов делителя импульсов 11 относительно выходных импульсов опорного делителя 3.

В режиме «ИЗМЕРЕНИЕ во время действия импульсов на выходе синхронизатора 16, на выходе элемента совпадения 17 вырабатываются импульсы, которые через элемент «ИЛИ 10 поступают на вход синфазного управления записью в делитель импульсов 11.

На объединенные первые входы элементов совпадения 13 в режиме «ИЗМЕРЕНИЕ подается положительный разрешающий потенциал с другого выхода коммутатора 19, благодаря чему значения логических «О и «1 на выходах

элементов И 13 соответствуют коду, хранимому в дополнительном регистре 12. В режиме «ИЗМЕРЕНИЕ на информационные входы записи кода в делитель импульсов 11 в момент действия импульса синфазного управления записью кода в делитель 11 подаются поО тенциалы, соответствующие коду, хранимому в дополнительном регистре 12 И переписанному в этот регистр из делителя 11 в режиме «УСТАНОВКА НУЛЯ в синфазные моменты времени, задаваемыми одни.ми и теми же импульсами на выходе синхронизатора 16 в обоих режимах работы. Благодаря этой синфазности во время действия импульса установки делителя 1 1 в момент времени код на информационных входах записи кода вделитель 11 совпадает с кодом, разворачиваемым в этот момент

времени в делителе.11, и .состояние триггеров делителя 11 не изменяется. Если в результате воздействия имих.испои иомехи произошло ложное переключение триг1еров, то импульс с выхода синхронизатора 16 подается на вход синфазного управления записью кода в делитель 11 и происходит запись кода, хранимого в доиолнительиом регистре 12, т. е. восстанавливаются первоначальные, имевшие место до воздействия помехи фазовые соотношения между импульсами на выходах делителя 11 и опорного делителя 2. В наихудшем случае, когда сбой триггеров делителя 11 произойдет в интервале времени между выходным импульсом синхронизатора 16 и импульсом записи информации в регистр 15, восстановление фазовых соотношений счетчика будет нроизведено noc,ie одного ложного отсчета. Диапазон возможных флюктаций суммарного фазового .сдвнга в трактах собственного преобразователя- в большинстве случаев лежит в пределах единиц градусов электрических, что дает возможность ограничить емкость д ;полиительного статического регистра меньшим количеством разрядов по сравнению с полной емкостью делителя, определяемой тем количеством разрядов, которое необходимо для формирования-значного кода в пределах О-ЗбОЧ заданной дискретностью. Фазовращатель 6 введен для выборя ,чьного сдвига фаз собственно преобразователя так, чтобы возможные флюктуации сдвига фазы от дестабилизирующих факторов не совпадали страницей смены кода старших разрядов делителя. Это уменьшает количество разрядов дополнительного регистра. Таким образом, помехоустойчивость предлагаемого преобразователя фазового сдвига в празрядиый код определяется в основном, помехоустойчивость р-разрядного статического регистра на RS-триггерах при Р п, работающие в режиме хранения информации в течение длительного времени, намного превышающего время стробирования регистра по входу .правле| ия за1Н1Сью информации, что снижа -ероятносгь ,- ожиого переключения RS-триггеров под воздействием помехи со стороны входов. 11омехо)стойчивость известного преобразователя суп1ественпо ниже, так как определяется помехоустойчивость функи; м-.::,1ьно более сложного делителя частоты ,.-1 в с гр пповым переносом, выполненного .:а 1Ь-триггерах. При сравнительной oiieiiKe помехозашч :ч нности RS-триггеров и IK-T-v.: , еров o6paniae и;. себя внИмание .тот факт, ч: все 9 входов i 2 выхода каждого из 1К-три;еров счетчика числа импульсов задействованы к разветвленных взаимных связях, в то время как каждый RS-триггер статического регистра свя 2 своими входами - олько с источником входной информации посредством схем совпадения, отпираемых на очень короткое время дей.-твия импульса управления записью 11нформаиии, Таким обря: пм, .ведение . предлагаемом преобразователе до:.лнитель;| 1 опе:аци11 АУСТАПОВК.Л 11,.1Я в режиме работы «ИЗМЫЛЕН IE суи1ественно повышает помеxoaanuimciiiiocTi, и падежиость 1|реобразовате,-|Я фазов1)1Й сдвг:г-код. Фор МП.к: цзпбретени.ч Преобразовате,П5 гла поворота Ba,ia в код, содержащий кварцевый генератор, один пз iu iходов которого иодклк чен к входу фазирус.мого делнтеля частоты и через пос,-1едовате, соединенные опорный делитель частоты и фильтр непосредстве ло к первому в.хлдх-- к,поча и через датчик угла ко второмх- входу клкч;г, выход (юрмигювателя ме,;|пдра е о/ишм п.-; входов сиихропиз;;то 1:, ;1ругой выход 1 вариеного генератора соединен с другим входом синхронизатора, выход которогс; соедииен с одними входами двух элементов И, коммутатор режиM(iB (дним из выходов 11С1ДК,1ючсн к .ipyroMX входу первого э,1емепти 11 и Bxixu ключа, а выходом подк,п тчеИ к нходу второго г) ci 11, выход котс-.юг.) 11од|, к (:) ;;з вхсмон регистр ;, -. ,овые выходы фазируемого де. ,1я частоты ,1ючепы ко регистра, отличающийся тем, что, с п.е,1ьк1 п)М) номехозанипценности и надежности работы преобразовате,пя, в неге введены фазовраии1те,1Ь, элемент 1,411 и группа элементов П. доп(1,1нительн1 1е синхронизате1р, регистр и э,1ементы 11, BX(XT, фазоврг-ицателя еосдипен е 1м,1ходом к,-|Юча, а выход - с входом ({ opxHipOiUii xTH еандра, входы дополнительногч еинхронизаюра соединенго с входом синх|к ни атора и выходом eKipnoro делите,1я часготы и с первыми входам ; .ммсхтните.чьных нсрво1м и второго элементов 11, второй вход иервого дчполните, ьного элемента ii соединен с дру1н ; входом коммута ; ., первыми входамп rpyiuii.i элементов II и с становпч1 ы 11 ьxoдa lи разрядов фaзlIpye loгo де,ппчмя частоты, выхид иервого дополнительного :).:смента 11 Clеди;:ен с одним нз входов элемента И.Ич Д) гой вход МЛ И соединен с выходом первого элемента И, а выход соединен с у |1авляюшнм входом (IJiHiipye.Moro делителя, вТЧои вход второго допп,- ни ельного э;1емента II соединен с одним : : выходсВ коммутатор;;, а выход - с управляющнм входом дополнительного регистра, установочнь1е входы -oTopoi-o соединены с кодовыми выходами младн.ич р.язрядов фазируемого делите 1я, а выходы .юполпительного регистра через %ieNiei-i(.B И соединены с установочными ;-,:ода.пi м,а.чLHHx разрядов фазируемого дели чмя. Источники информации, принятые во ние при экспертизе: 1,Авторское свидетельство СССР AV 402048 кл. G 08 С 9..09, 1973, 2.Авторское свидетельство СССР ЛЬ 409268 кл.С 08 С 9/04, 1973,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для воспроизведения видеосигнала | 1987 |

|

SU1555918A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ ТОЧНОГО ВРЕМЕНИ | 1990 |

|

RU2033640C1 |

| Устройство для воспроизведения видеосигнала | 1982 |

|

SU1069189A1 |

| Устройство для измерения частоты и ритмичности сердечных сокращений | 1984 |

|

SU1219048A1 |

| Устройство автоматической подстройки линейного закона частотной модуляции | 1984 |

|

SU1218463A1 |

| Частотный преобразователь | 1980 |

|

SU884131A1 |

| ГЕНЕРАТОР С АВТОМАТИЧЕСКОЙ ПОДСТРОЙКОЙ ЧАСТОТЫ | 1992 |

|

RU2060584C1 |

| Умножитель-нормализатор частотныхСигНАлОВ | 1979 |

|

SU847505A1 |

| Система формирования и приема телевизионного сигнала при передаче изображения | 1988 |

|

SU1555909A2 |

| Устройство для программного управления скоростью подачи | 1982 |

|

SU1067473A1 |

Авторы

Даты

1978-03-05—Публикация

1976-05-17—Подача