(54) ЧАСТОТНЫЙ ПРЕОБРАЗОВАТЕЛЬ

I

Изобретение относится к вычислитель- ной технике и может быть использовано для связи вычислительной машины с внешними устройствами, в системах управления и моделирования и в измерительных системах.

Известен интерполятор, содержащий регистр кода приращений, блок анализа коэффициентных прирашений, накапливающие сумматоры, блок совпадения кодов, блок сравнения и блок управления i.

Недостатком этого устройства является то, что оно не обеспечивает преобразование частоты в код и кода в частоту.

Известен также преобразователь частоты в код, содержащий распределитель импульсов, первый и второй выходы которого соединены с первыми входами первогх) и второго коммутаторов, соответственно, к вторым входам Которых подключен выход регистра суммы, выход первого коммутатора через последовательно соединенные первый информационный регистр и третий коммутатор подключен к третьему

входу комбинационного сумматора, выход второго коммутатора через последовательно соединенные второй информационный регистр и четвертый коммутатор подключен к четвертому входу комбинационного сумматора, выход которого соединен с входом регистра суммы, третий и четвертый выходы распределителя импульсов подключены к управляющим входам третьего и четвертого ксйлмутаторов, управ10ляющие входы первого и второго синхронизаторов соединены с пятым выходом распределителя импульсов, шестой выход которого подключен к управляющим входам третьего и четвертого синхронизато15ров, выходы первого и третьего синхронизаторов через первый элемент ИЛИ подключены к первому входу комбинационно го сумматора, к второму входу которого через второй элемент ИЛИ подключены

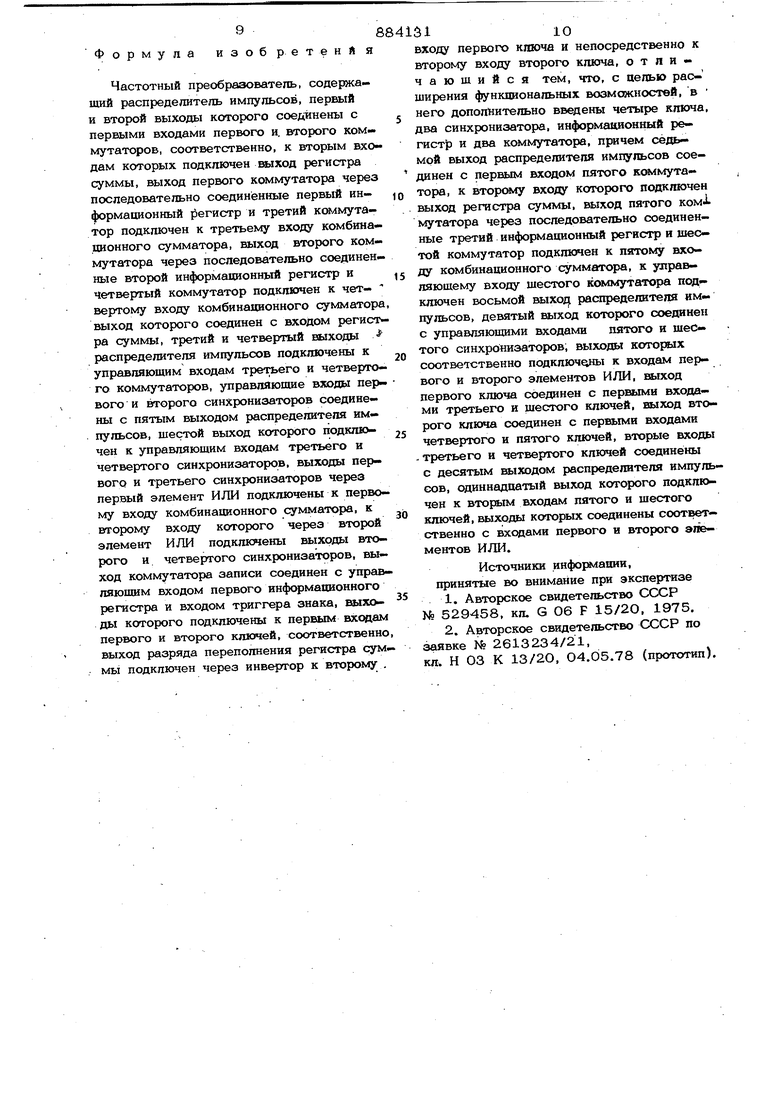

20 выходы вторюго и четвертого синхронизаторов, выход коммутатора записи соеди нен с управляющим входом первого информационного регистра и входом триггера знака, выходы которого подключены к пер вым входам первого и второго ключа, соответственно, выход разрада переполнения регистра суммы подключен через инвертор к второму входу первого ключа и непосредственно к второму входу второго ключа 2. Недостатком известного преобразовате ля является то, что он не выполняет функ ции линейного интерполирования, что сужа ет функциональные возможности устройства. Цель изобретения - расширение функциональных возможностей за счет реализации функций линейного интерполирования и увеличения числа каналов преобразований частота - код и код-частота. Поставленная цель достигается тем, что в преобразователь, содержаший распр делитель импульсов, первый и второй выходы которого соединены с первыми входами первого и второго коммутаторов, со ответственно, к вторым входам которых подключен выход регистра суммы, выход первого коммутатора через последователь но соединенные первый информационный регистр и третий коммутатор подключен к третьему входу комбинационного сумма тора, выход второго коммутатора через последовательно соединенные второй информационный регистр и четвертый коммутатор подключен к четвертому входу комбинационного сумматора, выход которого соединен с входом регистра суммы, третий и четвертый выходы распределителя импульсов подключены к управляющим входам третьего и четвертого коммутаторов, управляющие входы первого и.второго синхронизаторов соединены с пятым выходом распределителя импульсо шестой выход которого подключен к управляющим входам третьего и четвертог синхронизаторов, выходы первого и третьего синхронизаторов через первый эле- мент ИЛИ подключены к первому входу комбинационного сумматора, к второму входу которого через второй элемент ИЛ подключены выходы второго и четвертого синхронизаторов, выход коммутатора записи соединен с управляющим входом первого информационного регистра и входом триггера знака, выходы которого по ключены к первым входам первого и вто рого ключа, соответственно, выход разряда переполнения регистра суммы подключен через инвертрр ко второму входу первого ключа и непосредственно к втором входу второго ключа, дополнительно введены ключа, два синхронизатора, инфо 14 ационный регистр и два комк1утатора, прием седьмой выход распределителя Hivfny/ibсов соединен с первым входом пятого комутатора, к второму входу которого подключей выход регистра суммы, выход пяого коммутатхэра через последовательно соединенные третий информационный регистр и шестой коммутатор подключен к пятому входу комбинационного сумматора, к управляющему входу шестого коммутатора подключен восьмой выход распределителя импульсов, девятый выход которого соединен с управляющими входами пятого и шестого синхронизаторов, выходы которых соответственно подключены ко входам первого и второго элементов ИЛИ, выход первого ключа соединен с пер выми входами третьего и шестого ключей, выход второго к,люча соединен с первыми входами четвертого и пятого ключей, вто- . рые входы третьего и четвертого ключей соединены с десятым выходом распреде-) лителя импульсов, одиннадцатый выход которого подключен к вторым входам пятого и шестого ключей, выходы которых соединены соответственно с входами первого и второго элементов ИЛИ. На чертеже представлена структурная электрическая схема преобразователя. Частотный преобразователь содержит информационные регистры 1-3, выходы которых через третий 4, четвертый 5 и шестой 6 коммутаторы соединены со входами комбинационного сумматора 7. Выход комбинационного сумматора 7 соединен с входом регистра 8 суммы. Выход регистра 8 суммы через первый 9, второй 10 и пятый 11 кэммутаторы подключен к входам информационных регистров 1-3, а выход разряда переполнения регистра суммы подключен через инвертор 12 к первому 13 и второму 14 ключам непосредственно. Преобразуемый дополнительный код, поступающий по шине 15 через коммутатор 16 записи, хранится в первом информационном регистре 1, а знаковый разряд - в триггере 17 знака. Импульс записи по шине 18 управляет записью дополнительного коде. Прямой и инверсный выходы триггера 17 знака соединены с входами первого 13 и второго 14 ключей, соответственно. Выходы ключей 13 и 14 попарно соединены с входами ключей 19, 20 и 21, 22, соответственно. Вторые входы ключей 19-22 соедине)ы с выходами распределителя 23 импульсов. Преобразуемая частота по шинам 24-2- поступас т на

входы синхронизаторов ЗО-35. Выходы синхронизаторов 30-35 и ключей 20 и 21 через элементы ИЛИ 36 и 37 подкп1О чены к входам комбинированного Сумматора 7. Выходы распределителя ИЗ импульсов соединены с вхогдами синхронизаторов 30-35 и коммутаторов 4-6 и 9-11. По шинам 38-40 поступают сигналы, устанавливающие режим работы частотного преобразователя. Коды чисел с выходов информационных регистров 1-5 снимают ся по шинам 41-43.

Устройство работает следующим образом.

Частотный преобразователь осуществ- ляет трехканальное преобразование частоты в код; одноканальное преобразование кода в частоту совместно с одноканапьным преобразованием частоты в код и линейное интерполирование выходной вепичины во времени..

Для установки преобразователя в режим частота-код на вход распределителя 23 импульсов по шине 38 подается управляющий сигнал. С распределителя 23 импульсов на входы коммутаторов 4-6 и 9-11 поступают управляющие импульсы. Импульсы положительного приращения для первого канала поступают на синхронизатор 30 входной частоты и по управляюшему импульсу с распределителя 23 импульсов через элемент ИЛИ 36 поступают на вход младшего разряда комбинационного сумматора 7. Импульсы отрицательного приращения поступают на синхрони- . затор 31 входной частоты и по управляющему импульсу с распределителя 23 импульсов через элемент ИЛИ 37 псюту- пают на все разряды комбинационного сумматора 7, т.е. осуществляется прибав- ление дополнительного кода отрицательной единицы. Одновременно с-импульсом приращения (положительным или отрицательным) через открытый коммутатор 4 на вход комбинационного сумматора 7 иэ

информационного регистра 1 поступает предыдущее значение кода и результат записывается в регистр 8 суммы. По приходу импульса из распределителя 23 им- пульсов на коммутатор 9 результат пе- реписывается в информационный регистр 1. Затем управляющий импульс из распределителя 23 импульсов поступает на синхронизаторы 32 и 33 входной частоты. Импульсы положительного приращения вто- рого канала поступают на вход синхронизатора 32 входной частоты и через элемент .ИЛИ 36 на вход младшего разряда комбинационного сумматора 7. Импульсы отрицательного приращения второго канала поступают на вход синхронизатора 33 входной частоты и через элемент ИЛИ 37 на все разряды комбинационного сумматора 7, т.е. осуществляется прибавление дополнительного кода отрицательной единицы.

Одновременно с импульсом приращения через коммутатор 5 из информационного регистра 2 на комбинационный сумматор 7 поступает предыдущее значение кода, и результат попадает в регистр 8 суммы, откуда результат переписывается в информационный регистр 2 через коммутатор 10 при приходе управляющего импульса из распределителя 23 импульсов. Затем управлякчций импульс из распределителя 23 импульсов поступает на синхронизаторы 34 и 35 входной частоты. Импульсы положительного приращения третьего канала поступают на вход синхронизатора 34 входной частоты и через элемент ИЛИ 36 иа вход мл щшего разряда комбинационного сумматора 7. Импульсы отрицательного приращения третьего канала поступают на вход синхронизатора 35 входной частоты и через элемент ИЛИ 37 на все разряды комбинационного сумматора 7, т.е. осуществляется прибавление дополнительного кода отрицательной единицы.

Одновременно с импульсом приращения через коммутатор 6 из информационного регистра 3 на комбинационный сумматор 7 поступает предыдущее значение кода,-и результат попадает в регистр 8, из которого результат переписывается в информационный регистр 3 через коммутатор 11 при приходе управляющего импульса из распределителя 23 импульсов.

Опрос всех каналов циклически повторяется. Моменты поступления импульсов положительного и отрицательного приращений разделены во времени. Информационные регистры 1-3 обнуляются при считывании из них двоичного кода по шинам 41-43.

Для установки прюобразователя в режим код-частота на второй вход распределителя 23 имгульсов по шине 39 подается управляющий сигнал. В распределителе 23 импульсор вырабатываются управляк шие импульсы, которые в данном режиме поступают на коммутаторы 4-6, Юн 11. Преобразуемый дополнительный код по шине 18 приходит на вход коммутатора 16 записи. По импульсу шины 15, разрешающему запись кода в преобразователь осуществляется запись информационных разрадов кода в информационный регистр 1, а знак кода записывается в триггер 17 знака. Импульсы с распределителя 23 импульсов подаются на входы коммутаторов 4 и 5 и осуществляется суммировани кодов из информационных регистров 1 и 2 в комбинационном сумматоре 7. Резуль тат поступает в регистр 8 суммы. Затем подаются импульсы на вход ком мутатора 10 и на входы ключей 19и 22. В результате в информационный регистр 2 перезаписывается сумма, а значение разряда переполнения регистра 8 суммы выдается через ключи 13 и 14 в зависимости от состояния триггера знака 17 на ключи 19 -я 22 к формируется выходной импульс. Такое циклическое суммирование осуществляется н4 всем интервале преобразования. Затем управляющий импульс из распределителя 23 импульсов поступает на синхронизаторы 34 и 35 входной частоты. Третий канал преобразователя работает аналогично режиму частота-код. Таким образом, в данном режиме осуще твляются одноканальные преобразования кода в частоту и частоты в код. . Для установки преобразователя в режим линейная интерполящия на третий вход распределителя 23 импульсов по шине 4О подается управляющий сигнал. В распределителе 23 импульсов вырабатываются управляющие импульсы, которы в данном режиме поступают на коммутаторы 4-6, 1О и 11. Приращение, подлежащее интерполяции поступает по шине 18 на вход коммутатора 16 записи. По импульсу 15, разрешающему запись кода в преобразователь, осуществляется запис информационных разрядов кода в информационный регистр 1, а знак приращения записывается в триггер 17 знака. Импульсы с распределителя 23 импульсов подаются на входы коммутаторов 4 и 5, осуществляется суммирование кодоб из информационных регистров 1 и 2 в комбинационном сумматоре 7 и результа поступает в регистр 8 суммы. Затем подается импульс на вход коммутатора 1О и результат ббз разряда переполнения за писывается в информационный регистр 2. Подаются .импульсы на коммутатор 6 и ключи 20, 21. При этом происходит суммирование кода из информационного регистра 3 с дополнительным кодом разряда переполнения регистра 8 суммы. Знак разряда переполнения определяется 31 триггером 17 знака. При наличии единицы в разряде переполнения и значении триггера 17 знака, равном нулю, сигнал с разряда переполнения регистра 8 суммы через ключи 14 ti 21 к элемент ИЛИ 36 поступает на вход младшего разряда комбинационного сумматора 7. При состояниях триггера 17 знака, равном единице, и разряда переполнения, равном нулю, сигнал с инвертора 12 через ключи 13 и 20 и элемент ИЛИ 37 поступает на все разряды комбинационного сумматора 7, т.е. осуществляется прибавление отрицательной единицы. Затем подается импупьс с распределителя 23 импульсов на коммутатор 11 и результат из регистра 8 суммы перезаписывается в информационный регистр 3, откуда может быть снят внешними устройствами по шине 41. Информационный регистр 3 не обнуляется при считывании из него информации. Такая последовательность сигналов и действий осуществляется на всем интервале интерполирования, в результате чего осуществляется разворот приращения в поток импульсов с частотой, пропорциональной входному приращению, и суммирование данного потока с предыдущим значением функции, которое хранится в информйционном регистре 3. Изобретение позволяет уменьшить аппаратурные затрать:, разгрузить процессор вычислительной машины и повысить его производительность. Использование предлагаемого устройства позволяет повысить производительность центрального процессора, определяемую по формуле W- f, Тр где Тр - время решения задачи. На применении одного частотного преобразователя в режиме интерполяции на выходе ЦВМ производительность повьпцается. в К раз гдеТ,.- время, необходимое для осуществления операций интерполирования программным путем. При решении на ЦВМ задач, не требующих операций интерполирования, преобразователь может использоваться в режиме преобразования код-частота или частота-код. Вместе с тем, частотный преоб- разовфепь по, затратам оборудования сравним с известным. 9 Формула изоб ретенА я Частотный преобразоватепь, содержаший распределитель импульсов, первый и второй выходы которого соединены с первыми входами первого и. второго коммутаторов, соответственно, к вторым вхо дам которых подключен выход регистра суммы, выход первого коммутатора через последовательно соединённые первый информационный регистр и третий кдалмутатор подключен к третьему входу комбинационного сумматора, выход второго коммутатора через последовательно соединенные второй информационный регистр и четвертый коммутатор подключен к чет- вертому входу комбинационного сумматора выход которого соединен с входом регистра суммы, третий и четвертый выходы распределителя импульсов подключены к управляющим входам третьего и четвертого коммутаторов, управляющие входы первого и второго синхронизаторов соединены с пятым выходом распределителя импульсов, шестой выход которого подключен к управляющим входам третьего и четвертого синхронизаторов, выходы первого и третьего синхронизаторов через первый элемент ИЛИ подключены к первому входу комбинационного сумматора, к второму входу которого через второй элемент ИЛИ подключены выходы второго и четвертого синхронизаторов, выход коммутатора записи соединен с управляющим входом первого информационного регистра и входом триггера знака, выходы которого подключены к первым входам первого и второго ключей, соответственно выход разряда переполнения регистра сум- Mbi подключен через инвертор к второму . 31 входу первого кшоча к непосредственно к второму входу второго ключа, отличающийся тем, что, с цепью расширения функциональных возможностей, в него дополнительно введены четыре ключа, два синхронизатора, информационный регистр и два коммутатора, причем седьмой выход распределителя импульсов соединен с первым входом пятого ксшмутатора, к второму входу которого подключен выход регистра суммы, выход пятого ком мутатора через последовательно соединенные третий информационный регистр и шестой коммутатор подключен к пятому входу комбинационного сумматора, к управляющему входу щестого коммутатора подключен восьмой выхо/ распределителя импульсов, девятый выход которого соединен с управляющими входами пятого и шестого синхронизаторов, выходы которых соответственно подключены к входам первого и второго элементов ИЛИ, выход первого ключа соединен с первыми входами третьего и щестого ключей, выход второго ключа соединен с первыми входами четвертого и пятого ключей, вторые входь третьего и четвертого ключей соединены с десятым выходом распределителя импулоьсов, одиннадцатый выход которого подключен к вторым входам пятого и щестого ключей, выходы которых соединены соответственно с входами первого и вторюго элементов ИЛИ. Источники инфор«1ации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР O 529458, кл. G Об F 15/20, 1975. 2.Авторское свидетельство СССР по аявке № 2613234/21, кл. Н 03 К 13/20, O4.d5.78 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь частоты в код | 1978 |

|

SU744977A1 |

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

| Цифровой следящий электропривод | 1981 |

|

SU1008703A1 |

| Устройство для определения оптимальных траекторий | 1983 |

|

SU1223240A1 |

| УСТРОЙСТВО ДЛЯ ИМИТАЦИИ РАДИОЛОКАЦИОННОГО ИЗОБРАЖЕНИЯ МЕСТНОСТИ | 1988 |

|

SU1841035A1 |

| Цифровой синтезатор частоты | 1980 |

|

SU966849A2 |

| Устройство для решения игровых задач на вычислительных сетях | 1982 |

|

SU1104522A1 |

| Цифровой преобразователь координат | 1980 |

|

SU942004A1 |

| Вычислительный узел цифровой сетки | 1987 |

|

SU1501053A1 |

| Устройство для отображения информации | 1983 |

|

SU1124374A1 |

Авторы

Даты

1981-11-23—Публикация

1980-03-12—Подача