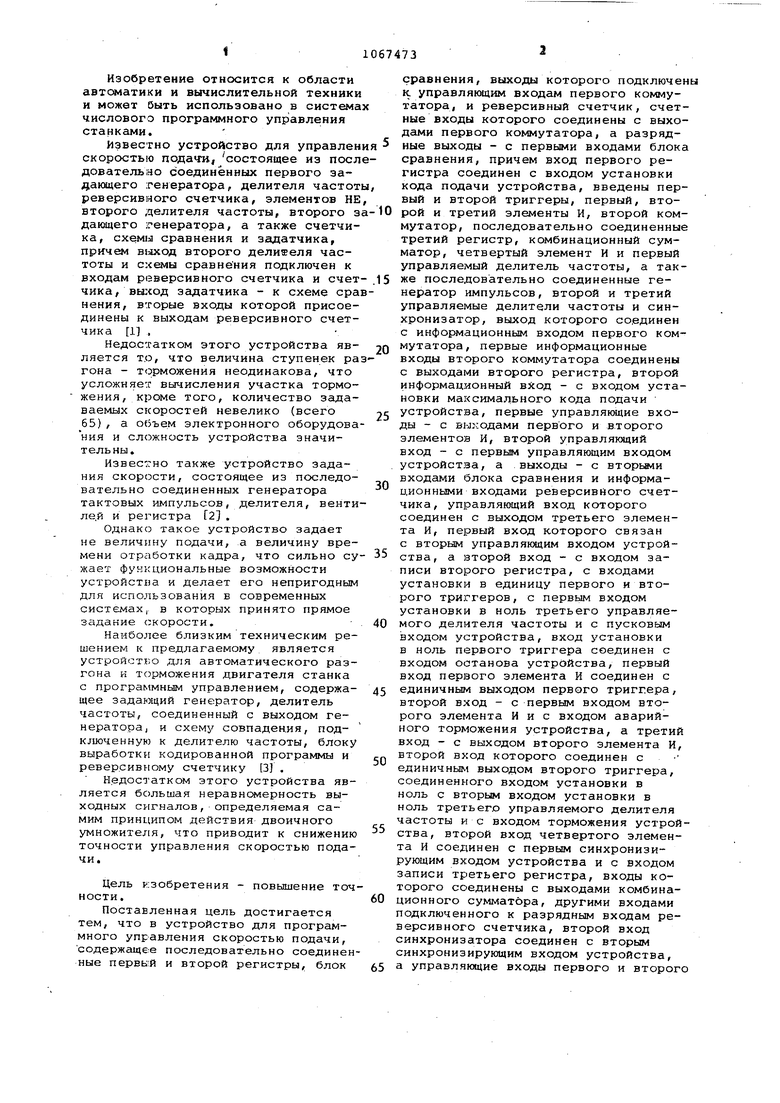

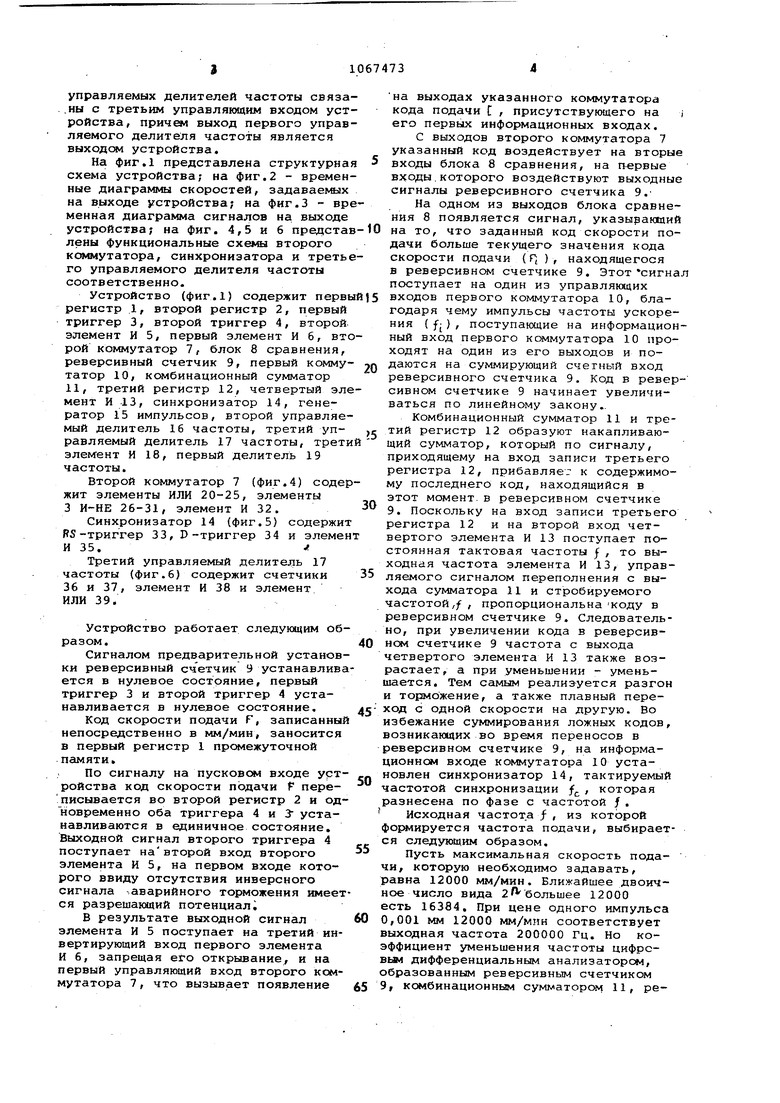

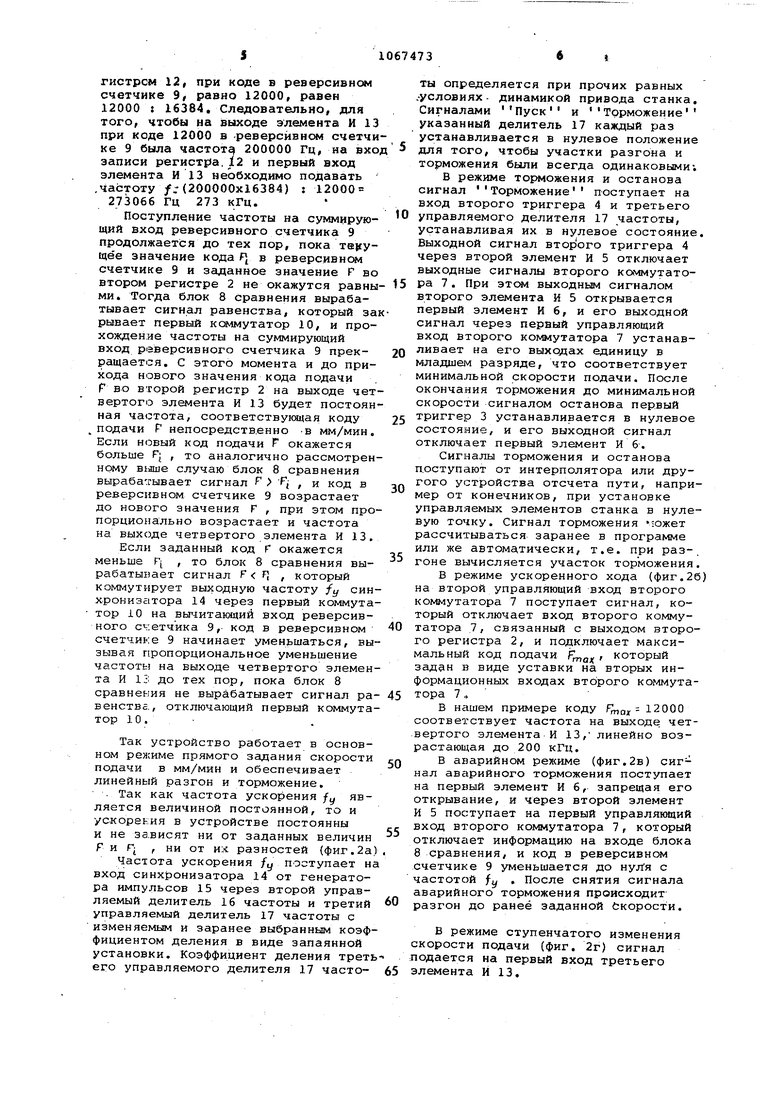

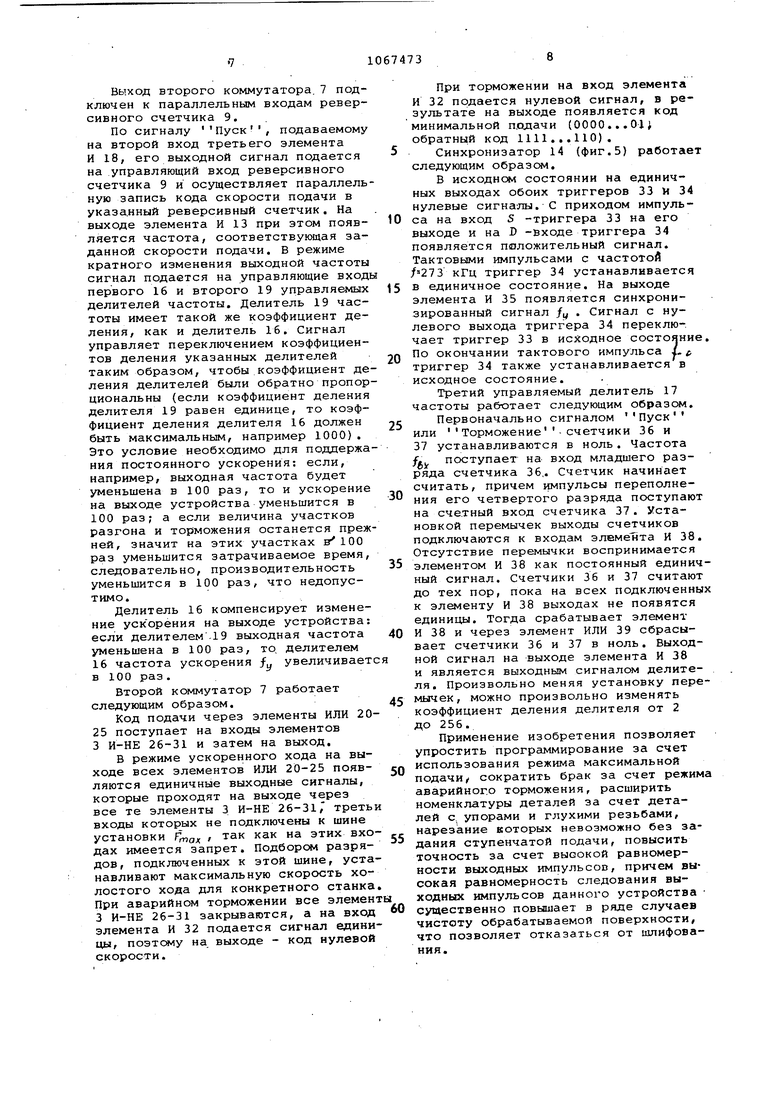

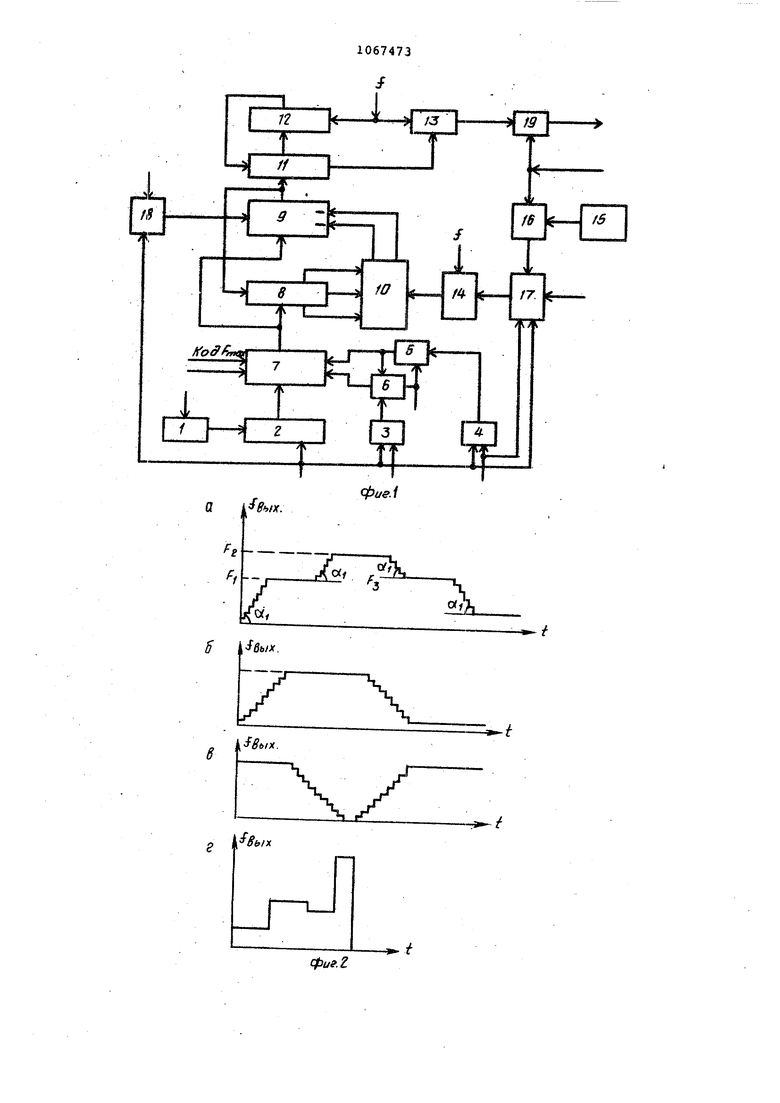

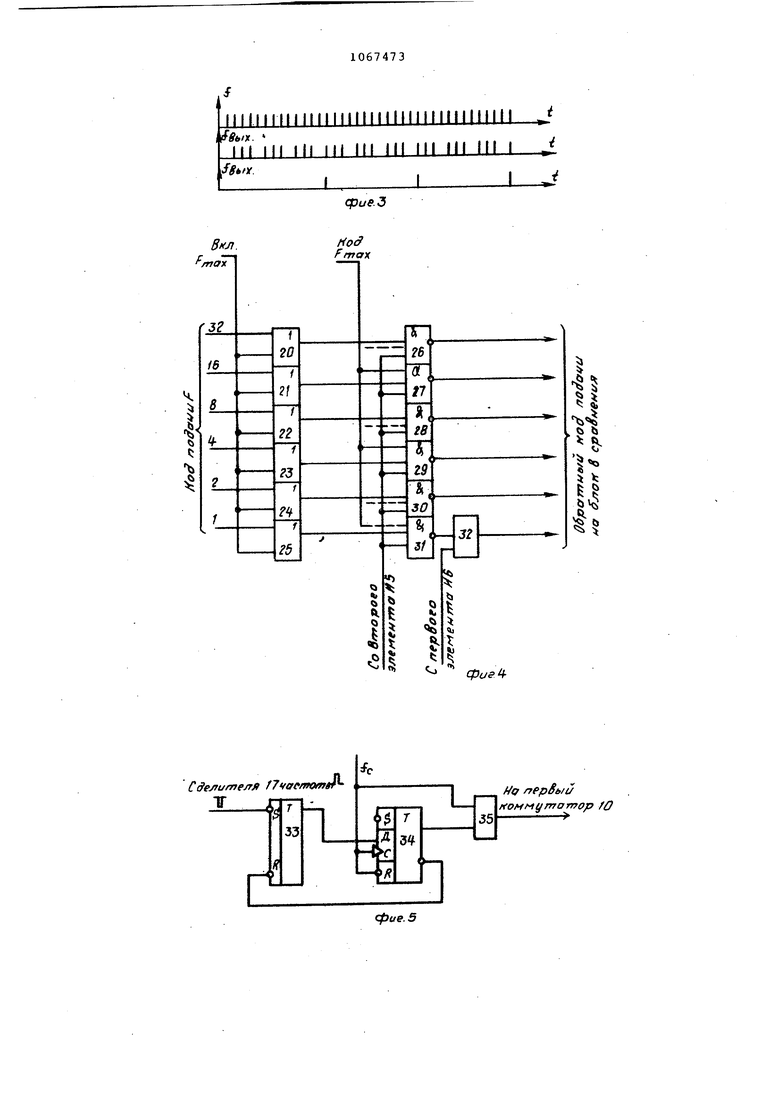

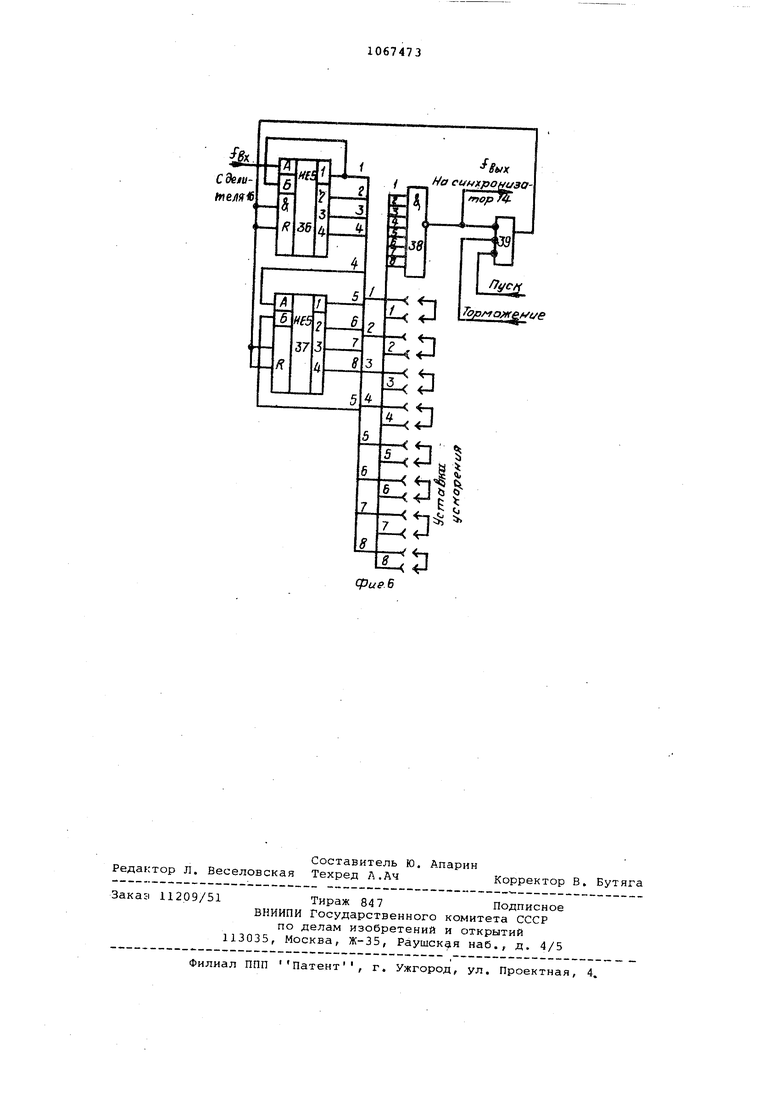

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в система числового программного управления станками. Известно устройство для управлен скоростью подачтй, состоящее из посл дователыяо соединённых первого задающего генератора, делителя частот реверсивного счетчика, элементов НЕ второго делителя частоты, второго з дающего генератора, а также счетчика, схем1л сравнения и задатчика, причем второго делителя частоты и схемы сравнения подключен к входам реверсивного счетчика и счет чика, вы;сод задатчика - к схеме сра нения, вторые входы которой присоединены к выходам реверсивного счетчика 1 , Недостатком этого устройства является т.о, что величина ступенек ра гона - торможения неодинакова, что усложняе::: вычисления участка торможения, кроме того, количество задаваемых скоростей невелико (всего 65), а объем электронного оборудова ния и сл зжность устройства значительны. Известно также устройство задания скорости, состоящее из последовательно соединенных генератора тактовых импульсов, делителя, венти ле.й и регистра Г2 . Однако такое устройство задает не величину подачи, а величину времени отработки кадра, что сильно су жает функциональные возможности устройстиа и делает его непригодным для использования в современных системах, в которых принято прямое задание скорости, Наиболее близкимтехническим решением к предлагаемому, является устройство для автоматического разгона и торможения двигателя станка с программным управлением, содержащее задающий генератор, делитель частоты, соединенный с выходом генератора, и схему совпадения, подключенную к делителю частоты, блоку выработкрг кодированной программы и реверсивному счетчику 3} . Недостатком этого устройства является большая неравномерность выходных сигналов, определяемая самим принципом действия двоичного умножителя, что приводит к снижению точности управления скоростью подачи. Цель изобретения - повышение точ ности. Поставленная цель достигается тем, что в устройство для программного управления скоростью подачи, содержаще:е последовательно соединен ные первь й и второй регистры, блок сравнения, выходы которого подключены к. управляющим входам первого коммутатора, и реверсивный счетчик, счетные входы которого соединены с выходами первого коммутатора, а разрядные выходы - с первыми входами блока сравнения, причем вход первого регистра соединен с входом установки кода подачи устройства, введены первый и второй триггеры, первый, второй и третий элементы И, второй коммутатор, последовательно соединенные третий регистр, комбинационный сумматор, четвертый элемент И и первый управляемый делитель частоты, а также последовательно соединенные генератор импульсов, второй и третий управляемые делители частоты и синхронизатор, выход которого соединен с информационным входом первого коммутатора , первые информационные входы второго коммутатора соединены с выходами второго регистра, второй информационный вход - с входом установки максимального кода подачи устройства, первые управляющие входы - с выходами первого и второго элементов И, второй управляющий вход - с первым управляющим входом устройства, а выходы - с вторь 1И входами блока сравнения и информационными входами реверсивного счетчика, управляющий вход которого соединен с выходом третьего элемента И, первый вход которого связан с вторым управляющим входом устройства, а второй вход - с входом записи второго регистра, с входами установки в единицу первого и второго триггеров, с первым входом установки в ноль третьего управляемого делителя частоты и с пусковым входом устройства, вход установки в ноль первого триггера соединен с входом останова устройства, первый вход первого элемента И соединен с единичным выходом первого триггера, второй вход - с первым входом второго элемента И и с входом аварийного торможения устройства, а третий вход - с выходом второго элемента И, второй вход которого соединен с единичным выходом второго триггера, соединенного входом установки в ноль с вторым входом установки в ноль третьего управляемого делителя частоты и с входом торможения устройства, второй вход четвертого элемента И соединен с первым синхронизирующим входом устройства и с входом записи третьего регистра, входы которого соединены с выходами комбинационного сумматора, другими входами подключенного к разрядным входам реверсивного счетчика, второй вход синхронизатора соединен с вторым синхронизирующим входом устройства, а управляющие входы первого и второго управляемых делителей частоты связа ..ны с третьим управляющим входом уст ройства, причем выход первого управ ляемого делителя частоты является выходом устройства. На фиг.1 представлена структурна схема устройства; на фиг,2 - времен ные диаграммы скоростей, задаваег«лх на выходе устройства; на фиг.З - вр менная диаграмма сигналов на выходе устройства; на фиг. 4,5 и 6 предста лены функциональные второго коммутатора, синхронизатора и треть го управляемого делителя частоты соответственно. Устройство (фиг.1) содержит первы регистр 1, второй регистр 2, первый триггер 3, второй триггер 4, второй элемент И 5/ первый элемент И б, вт рой коммутатор 7, блок 8 сравнения, реверсивный счетчик 9, первый татор 10, комбинационный сумматор 11, третий регистр 12, четвертый эл мент И 13, синхронизатор 14, генератор 15 импульсов, второй управляемый делитель 16 частоты, третий управляемый делитель 17 частоты, трети элемент И 18, первый делитель 19 частоты. Второй коммутатор 7 (фиг.4) содер жит элементы ИЛИ 20-25, элементы 3 И-НЕ 26-31, элемент И 32. Синхронизатор 14 (фиг.5) содержит Я5-триггер 33, D-триггер 34 и элемен И 35. Третий управляемый делитель 17 частоты (фиг.6) содержит счетчики 36 и 37, элемент И 38 и элемент ИЛИ 39. Устрюйство работает следующим образом. Сигналом предварительной установки реверсивный счетчик 9 устанавлива ется в нулевое состояние, первый триггер 3 и второй триггер 4 устанавливается в нулевое состояние. Код скорости подачи F, записанный непосредственно в мм/мин, заносится в первый регистр 1 промежуточной памяти. По сигналу на пусковс входе уртройства код скорости подачи f переписывается во второй регистр 2 и од новременно оба триггера 4 и 3 устанавливаются в единичное состояние. Выходной сигнал второго триггера 4 поступает навторой вход второго элемента И 5, на первом входе которого ввиду отсутствия инверсного сигнала -аварийного торможения имеет ся разрешающий потенциалi В результате выходной сигнал элемента И 5 поступает на третий инвертирующий вход первого элемента И 6, запрещая еГо открывание, и на первый управляющий вход второго коммутатора 7, что вызывает появление на выходах указанного коммутатора кода подачи С , присутствующего на i его первых информационных входах. С выходов второго коммутатора 7 указанный код воздействует на вторые входы блока 8 сравнения, на первые входы.которого воздействуют выходные сигналы реверсивного счетчика 9. На одном из выходов блока сравнения 8 появляется сигнал, указывающий на то, что заданный код скорости подачи больше текущего значения кода скорости подачи (Г ), находящегося в реверсивном счетчике 9. Этотсигнал поступает на один из управляющих входов первого коммутатора 10, благодаря чему импульсы частоты ускорения ( f), поступающие на информационный вход первого коммутатора 10 проходят на один из его выходов и подаются на суммирующий счетный вход реверсивного счетчика 9. Код в реверсивном счетчике 9 начинает увеличиваться по линейному закону.. Комбинационный сумматор 11 и третий регистр 12 образуют накапливающий сумматор, который по сигналу, приходящему на вход записи третьего регистра 12, прибавляет к содержимому последнего код, находящийся в этот момент, в реверсивном счетчике 9. Поскольку на вход записи третьего регистра 12 и на второй вход четвертого элемента И 13 поступает постоянная тактовая частоты , то выходная частота элемента И 13, управляемого сигналом переполнения с выхода сумматора 11 и стробируемого частотой,/ , пропорциональна коду в реверсивном счетчике 9. Следовательно, при увеличении кода в реверсивном счетчике 9 частота с выхода четвертого элемента И 13 также возрастает, а при уменьшении - уменьшается. Тем самым реализуется разгон и торможение, а также плавный переход с одной скорости на другую. Во избежание суммирования ложных кодов, возникающих во время переносов в реверсивном счетчике 9, на информационном входе коммутатора 10 установлен синхронизатор 14, тактируемый частотой синхронизации f. , которая разнесена по фазе с частотой f. Исходная частот.а f , из которой формируется частота подачи, выбирается следукяи.им образом. Пусть максимальная скорость подачи, которую необходимо задавать, авна 12000 мм/мин. Ближайшее двоичное число вида 2 большее 12000 есть 16384. При цене одного импульса 0,001 мм 12000 мм/мин соответствует выходная частота 200000 Гц. Но коэффициент уменьшения частоты цифровым дифференциальным анализатором, образованным реверсивным счетчиком 9, комбинационным сумматором И, регистрсм 12, при коде в реверсивном счетчике 9/ равно 12000, равен 12000 : 16384. Следовательно, для того, чтобы на в ыходе элемента И 13 при коде 12000 в -реверсивном счетчи ке 9 была частоту 200000 Гц, на вхо записи регистра.12 и первый вход элемента И 13 необходимо подавать .частоту /.(200000x16384) : 12000 273066 Гц 273 кГц. Поступление частоты на суммирующйй вход реверсивного счетчика 9 продолжается до тех пор, пока текущее значение кода F в реверсивнс счетчике 9 и заданное значение Р во втором регистре 2 не окажутся равны ми. Тогда блок 8 сравнения вырабатывает сигнал равенства, который за рывает первый коммутатор 10, и прохождение частоты на суммирующий вход реверсивного счетчика 9 прекращается. С этого момента и до прихода нового значения кода подачи Г во второй регистр 2 на выходе чет вертого элемента И 13 будет постоян ная частота, соответствуквдая коду подачи Р непосредственно -в мм/мин. Если новый код подачи Г окажется больше F; , то аналогично рассмотрен ному Biime случаю блок 8 сравнения вырабаггывает сигнал f Pj , и код в реверсивном счетчике 9 возрастает до нового значения F , при этом про порционально возрастает и частота на выходе четвертого элемента И 13. Если заданный код Г окажется меньше f , то блок 8 сравнения вырабатыиает сигнал f , который коммутирует выходную частоту /у син хронизг1тора 14 через первый коммута тор 10 на вычитающий вход реверсивного счетчика 9, код в реверсивном счетчике 9 начинает уменьшаться, вы зывая пропорциональное уменьшение частоть на выходе четвертого элемен та И 13; до тех пор, пока блок 8 сравнения не вырабатывает сигнал ра венствс., отключающий первый коммута тор 10 . Так устройство работает в основном реисиме прямого задания скорости подачи в мм/мин и обеспечивает линейный разгон и торможение. . Так как частота ускорения /у является величиной постоянной, то и ускорения в устройстве постоянны и не за.висят ни от заданных величин F и г , ни от их разностей {фиг.2а Частота ускорения /у поступает н вход синхронизатора 14 от генератора импульсов 15 через второй управляемый делитель 16 частоты и третий управляемый делитель 17 частоты с изменяемым и заранее выбранным коэф фициентом деления в виде запаянной установки. Коэффициент деления трет его управляемого делителя 17 частоты определяется при прочих равных .-условиях - динамикой привода станка. Сигналами Пуск и Торможение указанный делитель 17 каждый раз устанавливается в нулевое положение для того, чтобы участки разгона и торможения были всегда одинаковыми-. В режиме торможения и останова сигнал Торможение поступает на вход второго триггера 4 и третьего управляемого делителя 17 частоты, устанавливая их в нулевое состояние. Выходной сигнал второго триггера 4 через второй элемент И 5 отключает выходные сигна.лы второго коммутатора 7. При выходньии сигналом второго элемента И 5 открывается первый элемент И 6, и его выходной сигнал через первый управляющий вход второго коммутатора 7 устанавливает на его выхсдаах единицу в младшем разряде, что соответствует минима.пьной скорости подачи. После окончания торможения до минимальной скорости сигналом останова первый триггер 3 устанавливается в нулевое состояние, и его выходной сигнал отключает первый элемент И 6. Сигна.лы торможения и останова поступают от интерполятора или другого устройства отсчета пути, например от конечников, при установке управляемых элементов станка в нулевую точку. Сигнал торможения южет рассчитываться заранее в программе или же автоматически, т.е. при раз-, гоне вычисляется участок торможения. В режиме ускоренного хода (фиг.26) на второй управляющий вход второго KOMMyTciTopa 7 поступает сигнал, который отключает вход второго коммутатора 7, связанный с выходом второго регистра 2, и подключает максимальный код подачи frria, который задан в виде уставки на вторых информационных входах BTdporo коммутатора 7., В нашем примере коду Ртах- 12000 соотвео.ствует частота на выходе четвертого элемента И 13, линейно возрастающая до 200 кГц. В аварийном режиме (фиг.Зв) сигнал авсфийного торможения поступает на первый элемент И 6, запрещая его открывсшие, и через второй элемент И 5 поступает на первый управляющий вход второго коммутатора 7, который отключает информацию на входе блока 8 сравнения, и код в реверсивном счетчике 9 уменьшается до нуля с частотой fy . После снятия сигнала аварийного торможения происходит разгон до ранее заданной йкорости. В режиме ступенчатого изменения скорости подачи (фиг. 2г) сигнал подается на первый вход третьего элемента И 13. Выход второго коммутатора. 7 подключен к параллельным входам реверсивного счетчика 9. По сигналу Пуск, подаваемому на второй вход третьего элемента И 18, его выходной сигнал подается на управляющий вход реверсивного счетчика 9 и осуществляет параллель ную запись кода скорости подачи в указанный реверсивный счетчик. На выходе элемента И 13 при этом появляется частота, соответствукмцая заданной скорости подачи, В режиме кратного изменения выходной частоты сигнал подается на управляющие вход первого 16 и второго 19 управляемых делителей частоты. Делитель 19 частоты имеет такой же коэффициент деления, как и делитель 16. Сигнал управляет переключением коэффициентов деления указанных делителей таким образом, чтобы коэффициент де ления делителей были обратно пропор циональны (если коэффициент деления делителя 19 равен единице, то коэффициент деления делителя 16 должен быть максимальным, например 1000). Это условие необходимо для поддержа ния постоянного ускорения: если, например, выходная частота будет уменьшена в 100 раз, то и ускорение на выходе устройства уменьшится в 100 раз; а если величина участков разгона и торможения останется преж ней, значит на этих участках 100 раз уменьшится затрачиваемое время, следовательно, производительность уменьшится в 100 раз, что недопустимо. Делитель 16 компенсирует изменение ускорения на выходе устройства: если делителемМ9 выходная частота уменьшена в 100 раз, то. делителем 16 частота ускорения fy увеличивает в 100 раз. Второй коммутатор 7 работает следующим образом. Код подачи через элементы ИЛИ 2025 поступает на входы элементов 3 И-НЕ 26-31 и затем на выход. В режиме ускоренного хода на выходе всех элементов ИЛИ 20-25 появляются единичные выходные сигналы, которые проходят на выходе через все те элеме.нты 3 И-НЕ 26-31 треть входы которых не подключены к шине установки Гтац так как на этих вхо дах имеется запрет. Подбором разрядов, подключенных к этой шине, уста навливают максимальную скорость холостого хода для конкретного станка При аварийном торможении все элемен 3 И-НЕ 26-31 закрываются, а на вход элемента И 32 подается сигнал едини цы, поэтому на, выходе - код нулевой скорости. При торможении на вход элемента И 32 подается нулевой сигнал, в результате на выходе появляется код минимальной п.одачи (0000...01; обратный код 1111...110). Синхронизатор 14 (фиг.5) работает следующим образом. В исходном состоянии на единичных выходах обоих триггеров 33 Я 34 нулевые сигналы. С приходом импульса на вход S -триггера 33 на его выходе и на D -входе триггера 34 появляется положительный сигнал. Тактовыми импульсами с частотой кГц триггер 34 устанавливается в единичное состояние. На выходе элемента И 35 появляется синхронизированный сигнал /1 . Сигнал с нулевого выхода триггера 34 переключает триггер 33 в исходное состояние. По окончании тактового импульса L. (, триггер 34 также устанавливается в исходное состояние. Третий управляемый делитель 17 частоты работает следующим образом. Первоначально сигналом Пуск или Торможение.счетчики 36 и 37 устанавливаются в ноль. Частота поступает на вход младшего разряда счетчика 36.. Счетчик начинает считать, причем импульсы переполнения его четвертого разряда поступают на сче.тный вход счетчика 37. Установкой перемычек выходы счетчиков подключаются к входам элемеТ1та И 38. Отсутствие перемычки воспринимается элементом И 38 как постоянный единичный сигнал. Счетчики 36 и 37 считают до тех пор, пока на всех подключенных к элементу И 38 выходах не появятся единицы. Тогда срабатывает элемент И 38 и через элемент ИЛИ 39 сбрасывает счетчики 36 и 37 в ноль. Выходной сигнал на выходе элемента И 38 и является выходным сигналом делителя. Произвольно меняя установку перемычек, можно произвольно изменять коэффициент деления делителя от 2 до 256. Применение изобретения позволяет упростить программирование за счет использования режима максимальной подачи/ сократить брак за счет режима аварийного торможения, расширить номенклатуры деталей за счет деталей с упорами и глухими резьбами, нарезание которых невозможно без задания ступенчатой подачи, повысить точность за счет высокой равномерности выходных импульсов, причем высокая равномерность следования выходных импульсов данного устройства сутдественно повышает в ряде случаев чистоту обрабатываемой поверхности, что позволяет отказаться от шлифования.

О .

фе/е.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного управления | 1986 |

|

SU1376065A1 |

| Устройство для управления разгоном и торможением исполнительного двигателя станка | 1981 |

|

SU1062646A1 |

| Устройство для программного управления позиционированием | 1987 |

|

SU1418651A1 |

| Устройство для управления позиционированием в ноль исполнительных органов станка | 1988 |

|

SU1571549A1 |

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

| Устройство для программного управления | 1982 |

|

SU1108392A1 |

| Фазоимпульсный преобразователь | 1983 |

|

SU1161977A1 |

| Устройство для программного управления | 1981 |

|

SU976428A1 |

| Устройство для числового программного управления станками | 1985 |

|

SU1291928A1 |

| Телевизионный координатор | 1983 |

|

SU1109956A1 |

УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ СКОРОСТЬЮ ПОДАЧИ, содержащее последовательно соединенные первый и второй регистры, блок сравнения, выходы которого подключены к управляющим входам первого,коммутатора, и реверсивный счетчик, счетные входы которого соединены с выходами первого коммутатора, а разрядные выходы - с первыми входами блока сравнения, причем вход первого регистра соединен с входом установки кода подачи устройства, отличающееся тем, что, с целью повышения точности устройства, оно содержит первый и второй триггеры, первый, второй и третий элементы И, второй коммутатор., последовательно соединенные третий регистр, комбинационный сумматор, четвертый элемент И и первый управляемый делитель частоты,- а также последовательно соединенные генератор импульсов, второй и третий управляемые делители частоты, и синхронизатор, выход которого соединен с информационным входом первого коммутатора, первые информационные входы второго коммутатора соединены с выходами второго регистра, второй информационный вход - с входом установки максимального кода подачи устройства, первые управляющие входы - с выходами первого и второго элементов и, второй управляющий вход- - с первым управляющим входом устройства, а выходы - с вторыми входами блока сравнения и информационными входами реверсивного счетчика, управляющий зход которого соединен с выходом третьего элемента И, первый вход которого связан с вторым управляющим входом устройства, а второй вход - с входом записи второго регистра, с входами установки в единицу первого и второго триггеров, с первым входом установки в ноль третьего управляемого делите.ля частоты и с пусковым входом устройства, вход установки в ноль пер(Л вого триггера соединен с входом останова устройства, первый вход первого элемента И соединен с единичным выходом первого триггера, второй вход.с первым входом второго .элемента И и с входом аварийного торможения устройства, а третий вход - с выходом второго элемента И, второй вход которого соединен с единичным выхоС35 дом второго- триггера, соединенного входом установки в ноль с вторым входом установки в ноль третьего 4 управляемого делителя частоты и с входом торможения устройства, второй вход четвертого элемента И соединен DO с первьм синхронизирующим входом устройства и с входом записи третьего регистра, входы которого соединены с выходами комбинационного сумматора, другими входами подключенного к разрядным входам реверсивного счетчика, второй вход синхронизатора соединен с вторым синхронизирующим входом устройства, а управлякхцие входы первого и второго управляемых делителей частоты связаны с третьим управлякяцим входом устройства, причем выход первого управляемого делителя частоты является выхол кустройства.

, ,

:«/

ff вь/х.

ifBblX.

g

фиг.г

л

Cpuf.S

u и

bIo

I

t.

HQ ,/a ffOMMyirrarrfop fO

S5

pue.5

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Электроавтоматика станков | |||

| Способы подготовки програг м и интерполяторы для контурных систем числового управления станками | |||

| М., Машиностроение, 1970, с | |||

| Приспособление для автоматической односторонней разгрузки железнодорожных платформ | 1921 |

|

SU48A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Прибор для очистки паром от сажи дымогарных трубок в паровозных котлах | 1913 |

|

SU95A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-01-15—Публикация

1982-04-09—Подача