Изобретение относится к вычислительной технике и может быть использовано для дешифрации информации в командных линиях связи.

Известен дешифратор двоичной- информации, содержащий генератор хронирующих имцульсов, устройство синхронизации и специальное устройство для разрешения неопределенности фаз хронизатора 1.

Недостатком этого устройства является наличие блока автономной синхронизации и фазирования.

Наиболее близким техническим решением к предлагаемому изобретению является дешифратор команд, содержащий регистр сдвига, элементы И, ИЛИ, триггеры, дешифратор н реле времени, причем выходы разрядов регистра сдвига подключены к первым входам соответствуюидих элементов И, вторые входы элементов И четных разрядов нодключены к единичному информационному входу четных разрядов, а вторые входы элементов И нечетных разрядов - к единичному информационному входу нечетных разрядов, выходы элементов И подключены к единичным входам соответств -ю цих триггеров, выходы триггеров к соответствующим входам дешифратора, выходы которого являются выходами дешифратора команд 2 .

Недостатко.м этого устройства является невысокая достоверность переданной информащп из-за невозможности приема команд в старт - стопном режи.ме с сравнением переданного и отквитированного кодов, а также отсутствие кодового разделения информации, передаваемой по одному каналу связи в несколько адресов.

Целью изобретения является повышение на дежности дешифратора и расширение его функ циональных возможностей.

Поставленная цель достигается те.м, что дешифратор содержит логический блок приема стартовых посылок, логический блок приема посылок исполнения, логический блок формирования сигнала исполнения, причем нулевой и единичный информационные входы четных разрядов подключены соответственно к первому и второму входам блока приема стартовых посылок, а также первого элемента ИЛИ, нулевой и единичный информационные входы нечетных разрядов - соответственно к первому и второму входам блока приема посылок сполнения, а также второго элемента ИЛИ, выход второго элемента ИЛИ подключеиь к ервому установочно.му входу блока приема тартовых посылок и первому синхронизирующему входу регистра сдвига, выход первого

элемента ИЛИ подключен к первому установечному входу блока приема посылок исполнения и второму синхронизирующему входу регистра сдвига, выход блока приема стартовых посылок подключен к управляющемувходу регистра сдвига, выход блока приема посылок исполнения - к парвому входу блока формирования сигнала исполнения, второй вход кг- орого подключен к выходу последнего разряда регистра сдвига, первый выход блока формирования сигнала исполнения подключен к уп-. равляющему входу дещифратора и к входу реле, времени, второй выход блока формирования сигнала исполнения и выход реле времени -рез третий элемент ИЛИ подключены к вторым установочным входам блоков приема стартовых посылок и посылок исполнения, а также к первому входу четвертого элемента. ИЛИ, .второй вход которого подключен к выхЬду установочного сигнала с блока приема стартовых досылок, а выход этого элемента ИЛИ подключен к установочному входу регистра сдвига и нулевым входам триггеров.

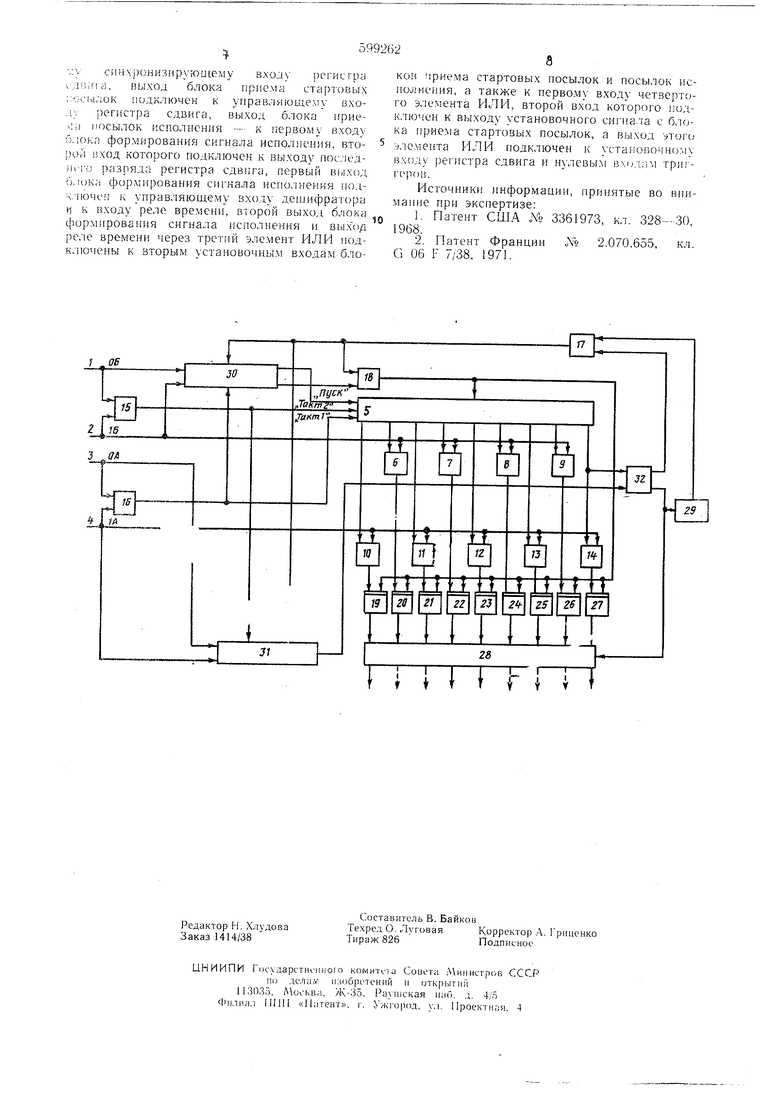

На чертеже представлена схема дешифратора команд, соответствующая устройству для адресного приема 256 команд, передаваемых ч тырехсимвольным кодом.

Дещифратор команд содержит нулевой вход 1 четных разрядов кода, единичный вход 2 четных разрядов, нулевой вход 3 нечетных разрядов кода, единичный вход 4 нечетных разрядов, регистр 5 сдвига, элементы И 6-14, элементы ИЛИ 15-18, триггеры 19-27, дешифратор 28, реле 29 времени, логический блок 30 приема стартовых посылок, логический блок 31 приема посылок исполнения, логический блок 32 формирования сигнала исполнения.

Дешифратор команд работает следующим образом.

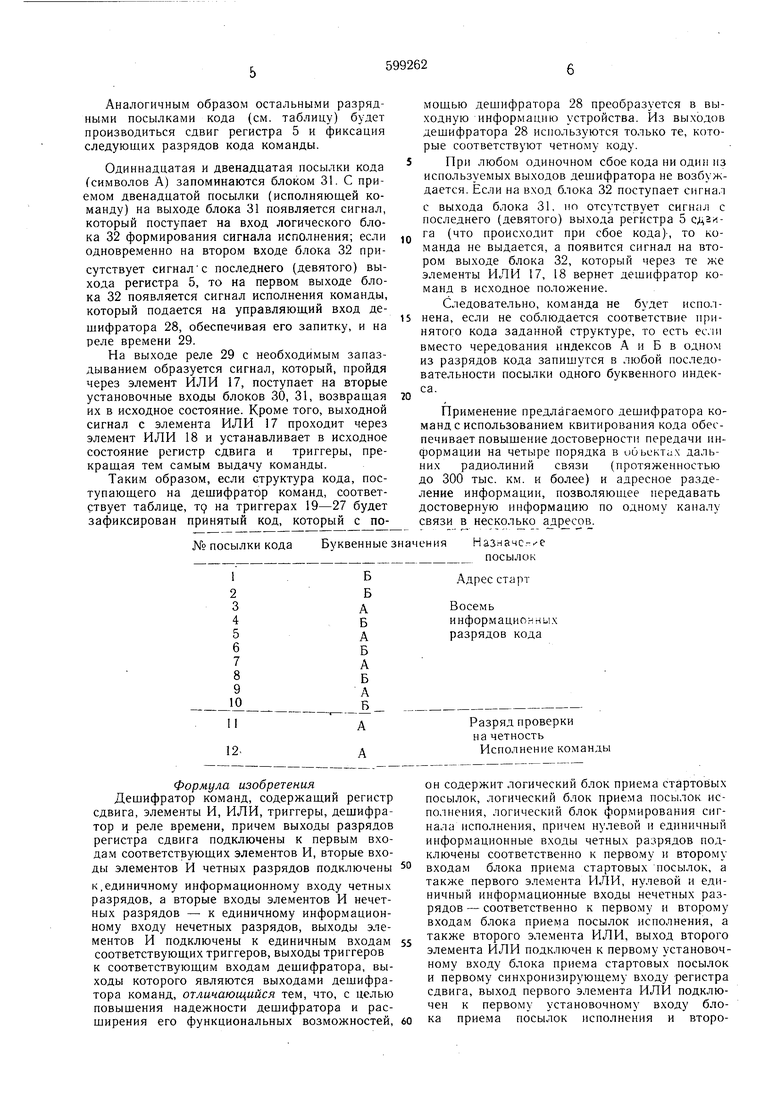

Каждая команда передается двенадцатью кодовыми посылками, назначение которых и принадлежность к символам приведены в табли 1е. При этом пары символов для передачи нечетных бит кода команды обозначены буквой А (1А и, ОА), два других символа :,/,и передачи четных .бит кода, команды - буквой Б (1Б и ОБ). .

Стартовая кодовая группа посылок включает дешифратор команд: последовательностью 1Б-ОБ включается первый дешифратор, ОБ-1Б - второй. Восемь последующих посылок передаются с чередованием символов А и Б, при этом их числовое значение соответствует двоичному коду команды. Одиннадцатая посылка служит для передачи разряда проверки на четность, если число единиц восьми информационных разрядов четно, то эта посылка передается символом ОА, если нечетно - символом 1А. Последняя двенадцатая посылка разрешает исполнение команды (запись информации). Эта посылка принадлежит к группе символов А, но числовое значение ее обратно по отношению к одиннадцатой посылке, и выдается на дешифратор при поразрядном совпадении переданного до нее кода с кодом квитанции.

Информация поступает на четыре входа: символы ОБ на нулевой вход 1 четных разрядов кода, 1Б на единичный вход 2 четных разрядов, ОА на нулевой вход 3 нечетныхразрядов кода, 1А на единичный вход 4 нечетных разрядов. Первая стартовая посылка поступает на вход логического блока 30 приема стартовых посылок, где запоминается; при появлении на втором входе блока 30 следующей (второй) стартовой посылки - непосредственно за первой - с выхода блока 30 выдается установочный сигнал, поступающий через элемент ИЛИ 18 на установочный вход регистра 5 и нулевые входы триггеров 19-27. В это же время и до конца приема команды на управляющий вход регистра 5 подается пусковой сигнал, разрешающий прием регистром тактовых последовательностей А и Б («такт 1 и «такт 2).

Если после первой стартовой посылки еле дует посылка индекса .4 (при сбое кода), то на установочный вход блока 30 поступит с выхода элемента ИЛИ 16 сигнал, отменяющий запоминание первой стартовой посылки; при этом с приемом второй стартовой посылки блок 30 выходные сигналы не выдает.

Пусковой сигнал с блока 30 отсутствует и в том случае, если информация предназначена для второго адреса. Тогда на данный дешифратор команд вначале поступит вторая стартовая посылка, которая запретит прием следующей посылки старта.

С приемом первой посылки символа А (первый разряд кода команды) через элемент ИЛИ 16 на первый синхронизирующий вход регистра сдвига поступает сигнал« такт 1, после которого на первом выходе регистра сдвига 5 появляется сигнал, поступающий на первый вход элемента И 10 нечетного (первого) разряда. Если первый разряд имеет значение единицы (посылка 1А), то на выходе элемента И 10 появится сигнал единицы, который поступит на единичный вход триггера 19 (фиксация первого разряда кода команды); если посылка первого разряда имеет нулевое значение (ОА), то триггер 19 останется в нулевом состоянии. Кроме того, посылки символов А (как единичного значения 1А, так. и нулевого - ОА) запоминаются в блоке 31 приема посылок исполнения; этот блок принимает исходное состояние с приходом любой посылки четного разряда (1Б или ОБ) с элемента ИЛИ 15.

Вторая разрядная посылка кода команды (си.мвол Б), сформироваЕипись элементом ИЛИ 15 в посылку «такт 2, произведет сдвиг регистра 5 (при этом появится сигнал на второ.м выходе регистра). Если значение второй разрядной посылки кода - 15, то на выходе элемента И 6 четного (второго) разряда появится сигнал и триггер 20 зафиксирует наличие единицы во втором разряде кода команды. Одновременно вторая разрядная посылка (и всех четных разрядов кода) будет поступать на вход логического блока 30 приема стартовых посылок и запоминаться в нем; однако следующие за ними посылки нечетных разрядов (с индексом А) через элемент ИЛИ 16 будут возвращать блок 30 в исходное состояние.

Аналогичным образом остальными разрядными посылками кода (см. таблицу) будет производиться сдвиг регистра 5 и фиксация следующих разрядов кода команды.

Одиннадцатая и двенадцатая посылки кода (символов А) запоминаются блоком 31. С приемом двенадцатой посылки (исполняющей команду) на выходе блока 31 появляется сигнал, который поступает на вход логического блока 32 формирования сигнала исполнения; если одновременно на втором входе блока 32 присутствует сигналС последнего (девятого) выхода регистра 5, то на первом выходе блока 32 появляется сигнал исполнения команды, который подается на управляющий вход дешифратора 28, обеспечивая его запитку, и на реле времени 29.

На выходе реле 29 с необходимым запаздыванием образуется сигнал, который, пройдя через элемент ИЛИ 17, поступает на вторые установочные входы блоков 30, 31, возвращая их в исходное состояние. Кроме того, выходной сигнал с элемента ИЛИ 17 проходит через элемент ИЛИ 18 и устанавливает в исходное состояние регистр сдвига и триггеры, прекращая тем самым выдачу команды.

Таким образом, если структура кода, поступающего на дещифратор команд, соответствует таблице, Т9 на триггерах 19-27 будет зафиксирован принятый код, который с помощью дешифратора 28 преобразуется в выходную информацию устройства. Из выходов дешифратора 28 используются только те, которые соответствуют четному коду.

При любом одиночном сбое кода ни один из используемых выходов дещифратора не возбуждается. Если на вход блока 32 поступает сигнал

с выхода блока 31, но отсутствует сигнал с последнего (девятого) выхода регистра 5 (что происходит при сбое кода)-, то команда не выдается, а появится сигнал на втором выходе блока 32, который через те же элементы ИЛИ 17, 18 вернет дешифратор команд в исходное положение.

Следовательно, команда не будет исполнена, если не соблюдается соответствие принятого кода заданной структуре, то есть ec.in вместо чередования индексов А и Б в одном из разрядов кода запишутся в любой последовательности посылки одного буквенного индекса.

Применение предлагаемого дешифратора команд с использованием квитирования кода обеспечивает повыщение достоверности передачи информации на четыре порядка в ойьектах дальних радиолиний связи (протяженностью до 300 тыс. км. и более) и адресное разделение информации, позволяющее передавать достоверную информацию по одному каналу связи в несколько адресов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Шифратор команд | 1973 |

|

SU467466A1 |

| Кодирующее устройство | 1987 |

|

SU1481899A1 |

| Устройство для сопряжения | 1978 |

|

SU723561A1 |

| Устройство для сопряжения цифровой вычислительной машины с магнитофоном | 1984 |

|

SU1188745A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА СООБЩЕНИЙ | 1992 |

|

RU2042276C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ТЕЛЕГРАФНЫХ КАНАЛОВ С ЭЛЕКТРОННО-ВЫЧИСЛИТЕЛЬНОЙ МАШИНОЙ | 1970 |

|

SU266386A1 |

| Стартстопное приемное устройство | 1985 |

|

SU1259506A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Устройство для передачи цифровой информации | 1976 |

|

SU595761A1 |

| Устройство приема и передачи дискретных сигналов | 1979 |

|

SU856031A1 |

Формула изобретения

Дешифратор команд, содержащий регистр сдвига, элементы И, ИЛИ, триггеры, дешифратор и реле времени, причем выходы разрядов регистра сдвига подключены к первым входам соответствующих элементов И, вторые входы элементов И четных разрядов подключены

к,единичному информационному входу четных разрядов, а вторые входы элементов И нечетных разрядов - к единичному информационному входу нечетных разрядов, выходы элементов И подключены к единичным входам соответствующих триггеров, выходы триггеров к соответствующим входам дешифратора, выходы которого являются выходами дещифратора команд, отличающийся тем, что, с целью повышения надежности дешифратора и расширения его функциональных возможностей,

он содержит логический блок приема стартовых посылок, логический блок приема посылок исполнения, логический блок формирования сигнала исполнения, причем нулевой и единичный информационные входы четных разрядов подключены соответственно к первому и второму входа.м блока приема стартовых посылок, а также первого элемента ИЛИ, нулевой и единичный информационные входы нечетных разрядов - соответственно к первому и второму входам блока приема посылок исполнения, а также второго элемента ИЛИ, выход второго элемента ИЛИ подключен к первому установочному входу блока приема стартовых посылок и первому синхронизирующему входу регистра сдвига, выход первого элемента ИЛИ подключен к первому установочному входу блока приема посылок исполнения и второсинхро)изируюи1.ему входу регистр v-,jiiiiia, выход блока приема стартовых ::осы,:гок ис дключен к уг1равляюще.у в.хо.лу ;)егистра сдвига, выход блока ирие.li посылок ксполненля -- к первому входу о.()кл формирования сигнала исполнения, втоiOii иход которого подключен к вы.ходу последni-1-o разряда регистра сдв1;га, первый выход блока формирования сигнала исполнеиия подключел к управляющему входу деи ифратора И к входу реле времени, второй выход б.-юка формирования сигнала 1 сг1олнения и выход реле времени через третий элемент ИЛИ иодк,л10чены к вторым установочным входам блоков чриема стартовых посылок и посылок исиолисния, а также к первому входу четвертого элемента ИЛИ, второй вхЪд которого 1 одклю-;еи к выходу установочного снгиа/ш с блока приема стартовых посылок, а выход этого элемента ИЛИ подключен к хчтанопочному входу jjerncTpa сдвига и нулевым входг-м тряггс-ров.

Источники информации, принятые во внимание при экспертизе:

Авторы

Даты

1978-03-25—Публикация

1974-10-04—Подача