1

Изобретение относится к вычислительной технике и может быть использовано для передачи информации в командных линиях связи.

Известен шифратор команд, содержащий регистр записи кода команд, регистр сдвига, инверторы, схемы совпадения «И, триггер, входную и четыре выходные шины.

С целью повышения достоверности передачи команд в стартстопном режиме по п адресам в предлагаемом шифраторе дополнительно установлены схема сравнения выданного кода и кода квитанции, реле времени и ключ кодирования адреса, причем входы ключа кодирования адреса соединены с первыми двумя выходами регистра сдвига, а выходы через инверторы - с выходными шинами четных бит, каждый из следующих выходов регистра сдвига соединен с первыми входами одной и другой схем совпадения «И, вторые входы которых соответственно соединены непосредственно и через инвертор с соответствующим разрядом регистра записи кода команды, выходы схем совпадения «И нечетных разрядов кода команды соединены с выходными шинами нечетных бит, выходы схем совпадения «И четных разрядов кода команд подключены к выходным шинам четных бит, последний выход регистра сдвига

соединен с одним входом триггера, выход которого подключен к первым входам двух трехвходовых схем совпадения «И, вторые входы одних и других трехвходовых схем совпадения «И соответственно соединены непосредственно и через инверторы с последним разрядом регистра записи кода команд, третьи входы первой и второй пар трехвходовых схем совпадения «И соединены соответственно через инвертор и непосредственно с выходом схемы сравнения выданного кода и кода квитанции, выходы первой пары трехвходовых схем совпадения «И соединены с выходными шинами нечетных бит, а выходы

второй пары трехвходовых схем совпадения «И соединены перекрестно с этими же входными шинами нечетных бит, выход схемы сравнения выданного кода и кода квитанции соединен с входом реле времени, выход которого подключен ко второму входу триггера.

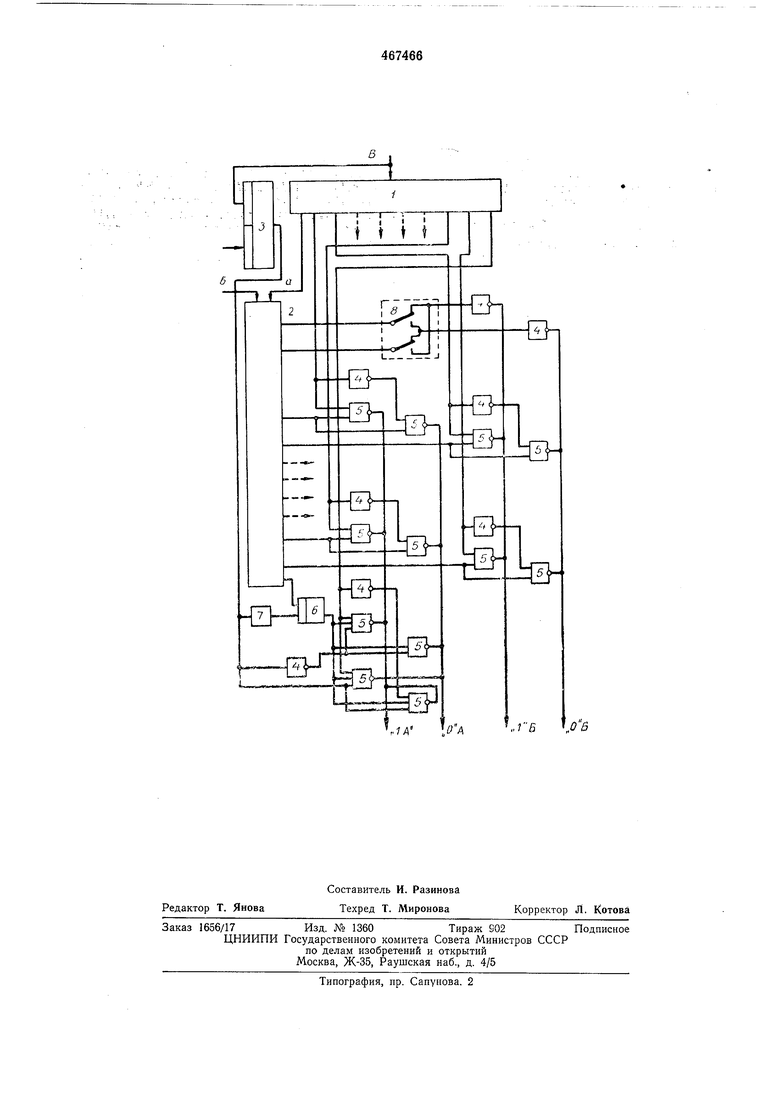

На чертеже показана блок-схема предлагаемого устройства.

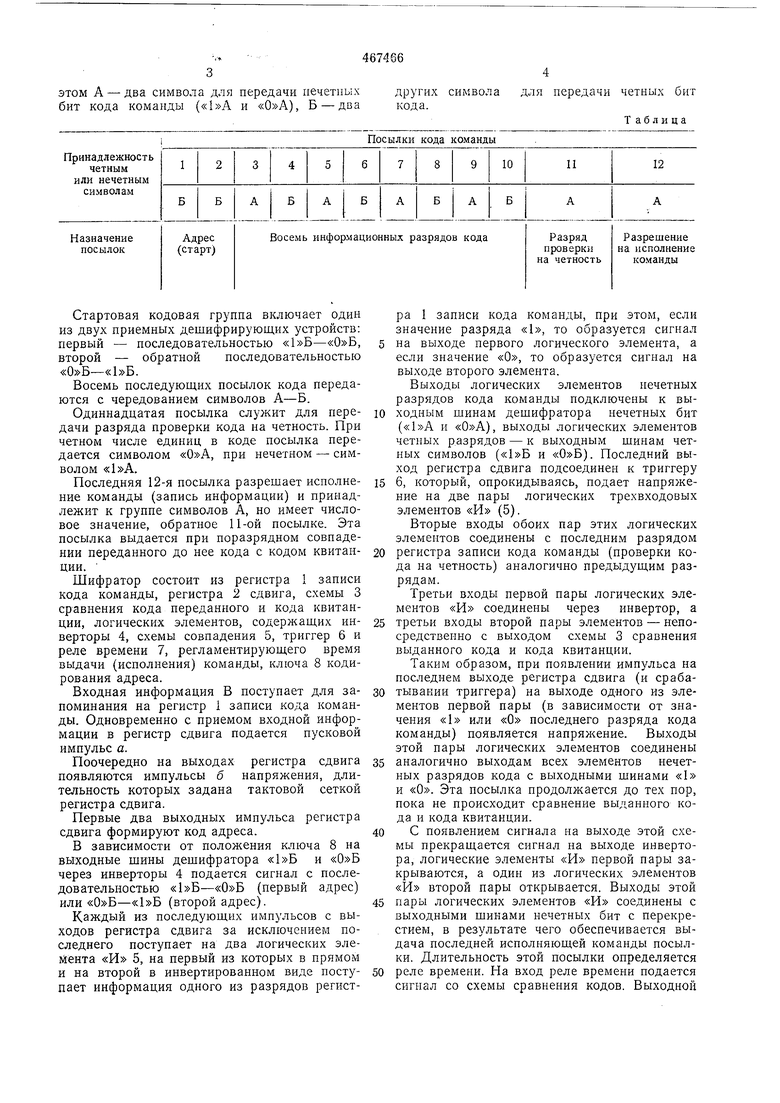

Устройство предназначено для передачи 256 команд в два адреса четырехсимвольным кодом в режиме «С КВИТИРОВАНИЕМ. Каждая команда передается 12-ю кодовыми посылками, назначение которых и принадлежность к символам показана в таблице, при этом А - два символа для передачи нечетных бит кода команды ( и ), Б - два

Принадлежность четным

или нечетным символам

Посылки кода команды другнх символа для передачи четных бит кода. Т аб л и ц а

| название | год | авторы | номер документа |

|---|---|---|---|

| Дешифратор команд | 1974 |

|

SU599262A1 |

| Устройство для ввода-вывода информации | 1984 |

|

SU1246103A2 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ | 1992 |

|

RU2051416C1 |

| Формирователь кодов для рельсовой цепи | 1990 |

|

SU1753598A1 |

| ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ | 1971 |

|

SU305477A1 |

| УСТРОЙСТВО ДЛЯ ПАРАЛЛЕЛЬНОЙ ОБРАБОТКИ ИНФОРМАЦИИ | 2008 |

|

RU2379751C2 |

| Устройство для управления вентильным преобразователем | 1984 |

|

SU1205243A2 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

| СДВИГАЮЩИЙ РЕГИСТР | 1995 |

|

RU2105357C1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЯ | 1992 |

|

RU2045781C1 |

Назначение посылок

Стартовая кодовая группа включает один из двух приемных дешифрирующих устройств: первый - последовательностью , второй - обратной последовательностью .

Восемь последующих посылок кода передаются с чередованием символов А-Б.

Одиннадцатая посылка служит для передачи разряда проверки кода на четность. Прн четном числе единиц в коде посылка передается символом , при нечетном - символом .

Последняя 12-я посылка разрешает исполнение команды (запись информации) и принадлежит к группе символов А, но имеет числовое значение, обратное 11-ой посылке. Эта посылка выдается при поразрядном совпадении переданного до нее кода с кодом квитанции.

Шифратор состоит из регистра 1 записи кода команды, регистра 2 сдвига, схемы 3 сравнения кода переданного и кода квитанции, логических элементов, содержащих инверторы 4, схемы совпадения 5, триггер 6 и реле времени 7, регламентирующего время выдачи (исполнения) команды, ключа 8 кодирования адреса.

Входная информация В поступает для запоминания на регистр 1 записи кода команды. Одновременно с приемом входной информации в регистр сдвига подается пусковой импульс а.

Поочередно на выходах регистра сдвига появляются импульсы б напряжения, длительность которых задана тактовой сеткой регистра сдвига.

Первые два выходных импульса регистра сдвига формируют код адреса.

В зависимости от положения ключа 8 на выходные шины дешифратора и через инверторы 4 подается сигнал с последовательностью (первый адрес) или (второй адрес).

Каждый из последующих импульсов с выходов регистра сдвига за исключением последнего поступает на два логических элемента «И 5, на первый из которых в прямом и на второй в инвертированном виде поступает информация одного из разрядов регистра 1 записи кода команды, при этом, если значение разряда «1, то образуется сигнал на выходе первого логического элемента, а если значение «О, то образуется сигнал на выходе второго элемента.

Выходы логических элементов нечетных разрядов кода команды подключены к выходным шинам дешифратора нечетных бит ( и ), выходы логических элементов четных разрядов - к выходным шинам четных символов ( и ). Последний выход регистра сдвига подсоединен к триггеру

6, который, опрокидываясь, подает напряжение на две пары логических трехвходовых элементов «И (5).

Вторые входы обоих пар этих логических элементов соединены с последним разрядом

регистра записи кода команды (проверки кода на четность) аналогично предыдущим разрядам.

Третьи входы первой пары логических элементов «И соединены через инвертор, а

третьи входы второй пары элементов - непосредственно с выходом схемы 3 сравнения выданного кода и кода квитанции.

Таким образом, при появлении импульса на последнем выходе регистра сдвига (и срабатывании триггера) на выходе одного из элементов первой пары (в зависимости от значения «1 или «О последнего разряда кода команды) появляется напряжение. Выходы этой пары логических элементов соединены

аналогично выходам всех элементов нечетных разрядов кода с выходными шинами «I и «О. Эта посылка продолжается до тех пор, пока не происходит сравнение выданного кода и кода квитанции.

С появлением сигнала на выходе этой схемы прекращается сигнал на выходе инвертора, логические элементы «И первой пары закрываются, а один из логических элементов «И второй пары открывается. Выходы этой

пары логических элементов «И соединены с выходными шинами нечетных бит с перекрестием, в результате чего обеспечивается выдача последней исполняющей команды посылки. Длительность этой посылки определяется

реле времени. На вход реле времени подается сигнал со схемы сравнения кодов. Выходной

импульс реле времени подается на второй выход триггера, устанавливая его и всю схему шифратора в исходное положение. Время задержки реле времени обеспечивает требуемое время выдачи (исполнения) команды.

При отсутствии сигнала на выходе схемы 3 сравнения кодов предусматривается ручная или,автомати1 ская повторная выдача команды (на чертеже не показано).

Предмет изобретения

Шифратор Команд, содержащий регистр записи кода команд, регистр сдвига, инверторы, схемы совпадения И, триггер, входную и четыре выходных шины, отличающийся тем, что, с целью повышения достоверности передачи команд в стартстопном режиме по п адресам, в нем дополнительно устрановлены схема сравнения выданного кода и кода квитанции, реле времени и ключ кодирования адреса, причем входы ключа кодирования адреса соединены с первыми п выходами регистра сдвига, а выходы через инверторы - с выходными шинами четных бит, каждый из следуюш,их выходов регистра сдвига соединен с первыми входами одной и другой схем совпадения «И, вторые входы которых соответственно соединены непосредственно и через инвертор с соответствующим разрядом регистра записи кода команды, выходы схем совпадения «И нечетных разрядов кода команды соединены с выходными шинами нечетных бит, выходы схем совпадения «И четных разрядов кода команд подключены к выходным шинам четных бит, последний выход регистра сдвига соединен с одним входом триггера, выход которого подключен к первым входам двух трехвходовых схем совпадения «И, вторые входы одних и других трехвходовых схем совпадения «И соответственно соединены непосредственно и через инверторы с последним разрядом регистра

записи кода комаид, третьи входы первой и второй пар трехвходовых схем совпадения «И соединены соответственно через инвертор и непосредственно с выходом схемы сравнения выданного кода и кода квитанции, выходы первой пары трехвходовых схем совпадеиия «И соединены с выходными шинами нечетных бит, а выходы второй пары трехвходовых схем совпадения «И соединены перекрестно с этими же выходными шинами нечетных бит, выход схемы сравнения выдаиного кода и кода квитанции соединен с входом реле времени, выход которого подключен ко второму входу триггера.

Авторы

Даты

1975-04-15—Публикация

1973-12-10—Подача