изобретение относится к вычислительной технике и может использоваться в телеграфной аппаратуре передачи данных.

Цель изобретения - повьппение на- дежйости устройства путем обеспечения, автоматического тестового контроля.

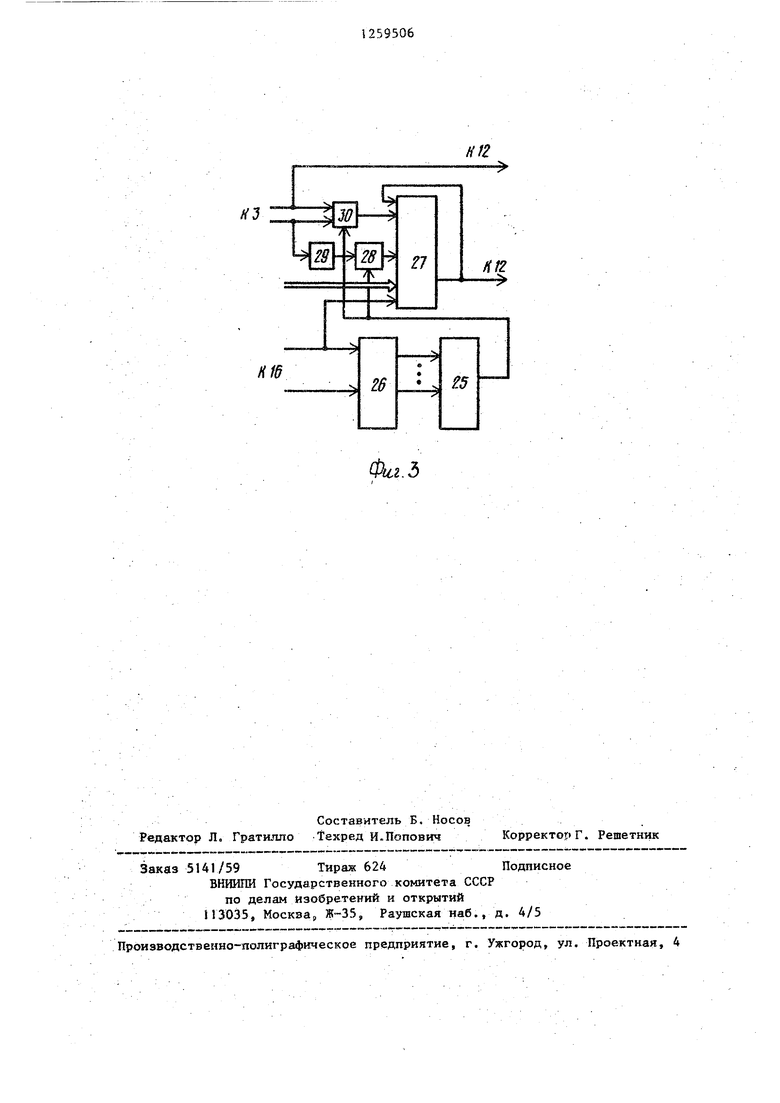

На фиг. 1 представлена структурная электрическая схема предложенного устройства; на фиг. 2 - схема последовательно-параллельного преобразователя, вариант вьшолнения; на фиг. 3 - схема блока имитации источника информации, вариант выполнения.

Стартстопное приемное устройство содержит (фиг. 1) входной согласующий блок 1, цикловой триггер 2, блок 3 формирования частот, делитель 4 частоты, первый и второй элементы И 5 и 6, стартовый триггер 7, элемент ИЛИ 8, последовательно-параллельный преобразователь 9, формирователь 10 тактов, блок П имитации источника информации, элемент И-ИЖ 12. Последовательно-параллельный преобразователь 9 (фиг, 2) содержит элемент И-НЕ 13, счетчик 1А импульсов передачи, первый и второй дешифраторы 15 и IS, счетчик 17 длины слова, бло

18свертки по модулю три, регистр

19приема, первый элемент И 20, первый элемент ИЛИ 21, буферный регистр 22 знака, второй элемент И 23, второ элемент И.ПИ 24.

Блок имитации источника информаци (фиг, 3) содержит дешифратор 25, счетчик 26 количества кодовых посылок, регистр 27, элемент И-НЕ 28, элемент НЕ 29, триггер 30,

Стартстопное приемное устройство работает следующим образом.

Для обеспечения программно-аппаратного контроля работоспособности стартстопного приемного устройства по определенной команде из цифровой вычислительной мапп-шь (ЦВМ) (не показана) формируются последовательно установочньй и управляющий сигнал (фиг, 1), по которым задается режим имитации внешнего источника информации блоком 11, и в регистр 27 (фиг.З записывается имитируемая восьмиразрядная кодовая посыпка. В отличие от работы с реальным источником информации, когда стартстопная информация проходит через второй вход элемента И-1ШИ 12 из входного согласующего

блока 1, в режиме имитации входная стартстопная информация фор№1руется блоком 11 имитации истсчнигга информации, который работает следующим . образом. После приема спгнала триггер 30 (фиг. 3) задним фронтом импульса управления переключается в противоположное состояние, вследствие чего изменяется режда{ работы регистра 27, из режима параллельной записи он переходит в режим последо- вательного сдвига. Записанная кодовая посылка начнет сдвигаться по регистру с частотой телеграфирования.

Благодаря наличию в регистре 27 обратной связи из младшего разряда в старший в данном режиме имитируется передача одинаковых кодовых посылок, соответствующих записанной пе0 ред режимом.

Количество кодовых посылок в стартстопном канале связи для каждого сообщения, например, фиксировано, поэтому блок 11 имитации источника

5 информации содержит счетчик 26 количества кодовых посылок с дешифратором 25, который настроен на фиксированную длину сообщения. По окончаний вьздачи имитируемого сообщения

0 на выходе дешифратора 23 формируется сигнал, который через элемент И-НЕ 28 блокирует сдвиговую цепь регистра 27. Управление элементом И-НЕ 28 осуществляется .сигналом с выхода элемента НЕ 29. Таким образом, имитация передачи кодового сообщения заканчивается.

Прием стартстопной информации происходит следующим образом.

Перед началом приема телеграфного сообщения цикловой триггер 2 находится в нерабочем состоянии и сигнал с его вь5хода запрещает работу делителя 4 частоты и не пропускает сигнал с выхода элемента И-ИЛИ 12 через второй элемент И 6 в последовательно- параллельный преобразователь 9. Для разрешения прохождения через элемент И-ИЛИ 2 информации из входного согласующего блока 1 перед началом приема из устройства связи подается сигнал на первый управляюпшй вход. Входной канал приема находится в состоянии, соответствующем уровню сигнала Стоп, и постоянно опрашивается частотой генератора (не показан)9 поступающей на синхровход циклового триггера 2. Цикл передачи каждой кодовой посылки всегда начинается с маркерно5

0

5

0

5

го сигнала Старт, который в отличи от сигнала Стоп имеет противоположный логический уровень. При поступлении с выхода элемента И-ИЛИ 12 перехода от Стопа к Старту, т.е. при появлении на (нформационном входе циклового триггера 2 уровня, соответ ствующего сигналу Старт, первым импульсом частоты генератора, поступающим из блока 3 формирования часто на еинхровход циклового триггера 2, последний устанавливается в рабочее состояние и сигнал с его выхода разрешает работу делителя 4 частоты и прохождение через второй элемент И 6 входного сигнала на информационный вход буферного регистра знака 22 (фиг. 2) последовательно-параллельного преобразователя 9. С выхода делителя 4 частоты через время, несколько превышакйцее половину периода передачи одного бита, вырабатывается сигнал, который, поступив на первый вход первого злемента ИЗ, опрашивает сигнал на выходе элемен- та И-ИЖ 12 при нулевом состоянии стартового триггера 7, За это время переходньй сигнал шума исчезнет и, если на линии все еще сохраняется уровень, соответствующий сигналу Старт, поступает стартовый бит. В противном случае на выходе первого элемента И 5 появится сигнал защиты от ложного старта, который, пройдя через ИЛИ 8, установит в исходное состояние цикловой триггер 2 и делитель 4 частоты. В случае приема сигнала Старт сигнал запреты от ложного старта не пройдет через первый элемент и 5 и делитель 4 частоты продолжает счет, в результате которого на втором выходе делителя 4 частоты появится сигнал Строб, который по заднему, фронту установит в единичное состояние стартовый триггер 7. Таким образом, в счетчик 17 длины слова первый сигнал Сброс не пройдет и бит кодовой посылки, соответствующий сигналу Старт, в буферный регистр 22 знака не запишется.

Если рабочая частота делителя 4 частоты обратно пропорциональна длительности передачи одного бита информации, то сигнал Строб с его выхода вырабатывается с частотой телеграфирования. Таким образец, поступающая с выхода второго элемента И 6

j ю «з 20 25 Q

5

5

5

на информационный вход буферного регистра 22 знака кодовая посылка последовательно в него записывается с помощью стробирующих сигналов, поступающих на еинхровход буферного регистра 22 знака с выхода первого элемента ИЛИ 21. Одновременно с этим стробирующие сигналы подсчитываются в счетчике I7 длины слова для того, чтобы блокировать прием маркерного сигнала Стоп. По окончании приема информационной части (знака) первой кодовой посылки на выходе второго дешифратора 16 появится сигнал 5 Т, с формированием которого прекращается установка в исходное состояние счетчика 14 импульсов передачи. Кроме того, сигнал 5 Т с выхода второго элемента ИЖ 24 разрешает прохождение частоты через второй элемент И 23 в счетчик 14 импульсов передачи. С помощью счетчика 14 импульсов передачи первого дешифратора 15 на выходе второго элемента И 23 формируется пачка из пяти импульсов, которая поступает в сдвиговые цепи буферного регистра 22 знака и регистра 19 приема. Кроне того, эта пачка импульсов с выхода второго элемента И 23 проходит через элемент ИЛИ 8 и устанавливает в исходное состояние цикловой триггер 2, стартовый триггер 7 и делитель 4 частоты. Так как выход буферного регистра 22 знака подключен к информационному входу регистра 19 приема, принятый знак продвигается по нему. По окончании передачи на выходе первого дешифратора 15 появится сигнал, который заблокирует передачу импульсов через второй элемент И 23. Прием cлeдyющ ix кодовых посьток происходит аналогично описанному. С поступлением следукицего стартового сигнала вновь установится в единичное состояние цикловой триггер 2 и произойдет прием следующего знака, а информация через формирователь 10 тактов продвигается на выход.

По окончании приема последнего знака (в приведенном примере - третьего) на выходе второго дешифратора 16 появится сигнал, который, пройдя через элемент И-НЕ 13, включит формирователь 10 тактов. Последний работает следующим образом. Когда второй элемент И-НЕ 23 закрыт, т.е. на его выходе потенциал, соответствующий

уровню логической t, формирователь 10 тактов работает в режиме параллельной i в его первый раз- .ряд, Порле .того,, как на его входе 2

появится сигнал 5 соответствующий уроню логического О, он переходит в режим последовательного сдвига. Записанная в него I начнет последовательно сдвигаться от начала к концу. На выходе формирователя 10 фор- мируется серия сигналов, одним из которых записывается контрольный код с блока 18 в контрольные разряды регистра 19 приема, другим вьщается сигнал прерьгоания в ЦВМ на выход устройства, а следующим импульсом устанавливается в исходное состояние счетчик 17 длины слова. Таким образом, стартстопное приемное устройство готово к приему и упаковке следующих кодовых посылок телеграфного сообщения.

Формула изобретения

1. Стартстопное приемное устройство, содержащее последовательно-параллельный преобразователь, входной согласующий блок и последовательно соединенные блок формирования час- тот, делитель частоты, к второму входу которого подключен выход циклового триггера, первый элемент И,, второй вход которого подключен к перво- i-fy входу второго элемента й элемент ИЛИ, к второму входу которого подключен первый выход последовательно- параллельного преобразователя и стартовый триггер, выходы которого подключены к третьему входу первого элемента И, второй вход которого соединен с. первым входом циклового триггера, и к первому входу последовательно-параллельного преобразователя, второй вход которого соединен с вто- рым входом стартового триггера и вторым выходом делителя частоты, третий и второй входы которого соединены соответственно с выходом элемента ИЛИ и вторым входом второго элемента И, выход которого подключен к третьему входу последовательно-параллельного преобразователя, четвертьш вход которого соединен с вторым входом цик лового триггера, к третьему входу которого подключен выход элемента И-ПИ, и первым выходом блока формирования частот, второй выход которого подключен к первому входу входног

JQ15 20

25

5

-jo д ,

0

5

согласующего блока, второй вход которого является информационным входом устройства, и первому входу формирователя тактов, первый и второй выходы которого подключены соответственно к пятому и шестому входам последовательно-параллельного преобразователя, второй выход которого соединен с вторым входом формирователя тактоа, третий выход которого является управляющим выходом устройства, инфор- мационнь1М выходом которого является третий выход последовательно-параллельного преобразователя, отличающееся тем, что, с целью повышения надежности устройства путем обеспечения автоматического тестового контроля, в него введены последовательно соединенные блок имитации источника информации и элемент И-ИЛИ, второй и третий входы которого соединены соответственно с выходом входного .согласующего блока и первым входом блока имитации источника информации, к второму и третьему входам которого подключены соответственно четвертый выход последовательно-параллельного преобразователя и третий выход блока формирования частот, при этом первьш управляющим входом устройства является четвертый вход элемента И-ИЛИ, выход которого подключен к первому входу циклового триггера, а первый, четвертьш и пятый входы блока имитации источника информации являются соответственно вторым управляющим, кодо- BSiM и установочным входами устройства.

2, Устройство по п. 1, . о т л и - ч и ю щ е е с я тем, что последовательно-параллельный преобразователь содержит последовательно соединенные первый элемент И, первый элемент ИЛИ, к второму входу которого подключен выход второго элемента И, буферный регистр знака, регистр приема и блок свертки по модулю.три, выход которого подключен к второму входу регистра приема, третий вход которого соединен с первым входом счетчика импульсов передачи, выход которого через первый дешифратор подключен к первому входу элемента И-НЕ, и выходом второго элемента И, первый и второй входы которого соединены со- о.тветственно с выходом первого дешифратора и выходом второго элемена:а ИЛИ, первый вход которого соединен

с вторым входом элемента И-НЕ и первым выходом второго дешифратора, вход и второй выходы которого соединены соответственно с выходом счетчика длины слова, к первому входу которого подключен выход первого элемента И, и вторым входом второго элемента , ИЛИ, выход которого подключен к второму входу счетчика импульсов передачи, при этом первьй и второй входы первого элемента И, второй вход буферного регистра знака, третий вход второго элемента И, второй вход счетчика длины слова и четвертый вход регистра приема являются соответственно первьм, вторым, третьим, четвертым, пятым и шестым входами последовательно-параллельного преобразователя, первым, вторым, третьим и четвертым выходами которого являются соответственно выход второго элемента И, выход элемента И-НЕ, второй выход регистра приема и первый выход второго дешифратора.

3. Устройство по п. 1, отличающееся тем, что блок имитации источника информации содержит счетчик количества кодовых посылок, выходы которого подключены к входам дешифратора, выход которого соединен 5 с первым входом элемента И-НБ, выход которого подключен к первому входу регистра, и первым входом триггера, второй вход и выход которого соединены соответственно с входом элемента

0 НЕ, выход которого подключен к вто рому входу элемента И-НБ, н вторым входом регистра, выход которого подключен к третьему входу регистра, четвертый вход которого соединен

5 с первым входом счетчика количества кодовых посылок, причем третий вход триггера, второй вход счетчика количества кодовых посылок, второй вход триггера, пятый вход регистра и пер0 вый вход счетчика количества кодовых посылок являются соответственно первым, вторым, третьим, четвертым и пятым входами блока имитации источника информации, выходом кото 5 рого является выход . регист РОо

Составитель Б. Носов Редактор Л. Гратилло Техред И.Попович

Заказ 5141/59 Тираж 624Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий И3035, МоскваJ , Раушская иаб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

tfka.3

Корректор Г. Решетник

| название | год | авторы | номер документа |

|---|---|---|---|

| Стартстопное приемное устройство | 1984 |

|

SU1205315A1 |

| Стартстопный электронный регенератор | 1973 |

|

SU508957A1 |

| Устройство для настройки стартстопного приемника на скорость передачи | 1976 |

|

SU620026A1 |

| Устройство для контроля работоспособности стартстопных передатчиков | 1979 |

|

SU777868A1 |

| Стартстопное приемное устройство | 1979 |

|

SU843283A2 |

| Устройство для синхронизации приемника телеграфных сигналов | 1978 |

|

SU985960A1 |

| Устройство для определения достоверности передачи дискретной информации | 1989 |

|

SU1674387A1 |

| Многоканальное приемное устройство стартстопных телеграфных сигналов | 1984 |

|

SU1264367A1 |

| Устройство приема и передачи дискретных сигналов | 1979 |

|

SU856031A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНЫХ СИГНАЛОВ | 1990 |

|

RU2012149C1 |

Изобретение отиосится к вычислительной технике. Повьшается надежность устр-ва путем обеспечения автоматического тестового контроля. Устр-во содержит входной согласукнций блок (ВСВ) I, цикловой триггер 2, блок формирования -частот 3, делитель частоты 4, два элемента И 5 и 6, стартовый триггер 7, элемент ИЛИ 8, последовательно-параллельный преобразователь (ППП) 9, формирователь тактов 10, блок имитации источника информации (БИИИ) 11 и элемент И-ИЛИ 12. При работе с реальным источником информации входная стартстопная информация проходит через элемент И-ИЛИ 12 из ВСБ 1. В режиме имитации виеш- него источника информации входная стартстопная информация формируется в БИИИ 1 по сигналам из ЦВМ. По окончании имитации перер.ач« кодового сообщения в устр-ве осуществляется прием стартстопной информации. Цель достигается введением БИИИ II и элемента И-ИЛИ 12. Устр-во также отличается выполнением ППП 9 и БШШ П, даны иллюстрации юс выполнения. 2 з.п. ф-лы, 3 ил.

| Стартстопное приемное устройство | 1984 |

|

SU1205315A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-09-23—Публикация

1985-05-15—Подача