(54) ГЕНЕРАТОР СЛУЧАЙНЫХ ПРОЦЕССОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регулирования расходажидКОСТи | 1979 |

|

SU842728A1 |

| Многоканальный программируемый аналого-цифровой преобразователь | 1985 |

|

SU1266002A1 |

| Двухотсчетный преобразователь угла поворота вала в код | 1977 |

|

SU734776A1 |

| Измеритель сдвига фаз (его варианты) | 1982 |

|

SU1040432A1 |

| Сейсмический вибратор | 1985 |

|

SU1277036A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Устройство для настройки и поверки импульсной электроразведочной аппаратуры | 1984 |

|

SU1241177A1 |

| Устройство для поверки электрических секундомеров | 1986 |

|

SU1392543A1 |

| Синтезатор интервалов времени | 1986 |

|

SU1406558A1 |

| УСТРОЙСТВО ДИСКРЕТНОГО ИЗМЕНЕНИЯ ФАЗЫСИГНАЛА | 1971 |

|

SU306559A1 |

1

Изобретение относится к вычислительной технике.

По основному авт. св. № 439064 известен генератор случайных процессов, содержащий задающий генератор импульсов, делитель частоты, устройство управления коэффициентом деления, реверсивный счетчик, преобразователь код-аналог, фильтр нижних частот, дещифратор, цифровой компаратор, выход которого подключен к входу триггера, реверсивный счетчик задания амплитуд, регистр сдвига, генератор случайной двоичной последовательности yпpaвлe ния амплитудой и частотой, переключатели, схему совпадения, устройство управления регистром сдвига и триггер управления 1.

Недостатком данного генератора является отсутствие автоматизации регулирования статистических характеристик контролируемого процесса.

Цель изобретения - расщирение функцио.нальных возможностей путем автоматизации регулирования статистических характеристик контролируемого процесса.

Поставленная цель достигается тем, что в генератор случайных, процессов, содержащий задающий генератор импульсов, делитель частоты с управляемым коэффициентом деления, блок управления коэффициентом деления, реверсивный счетчик, преобразователь код-аналрг, фильтр нижних частот, . дещифратор, цифровой компаратор, выход которого подключен к входу триггера, реверсивный счетчик задания амплитуды, регистр сдвига, генераторы случайной двоичной последовательности управления амплитудой и частотой, элемент совпадения, блок

to управления регистром сдвига, триггер управления, при этом выход задающего генератора импульсов через делитель частоты соединен с входом реверсивного счетчика, один из выходов которого через преобразователь код-аналог и фильтр нижних частот соеди5 нен с аналоговым выходом генератора, а выход дещифратора связан с входом цифрового компаратора и выходом реверсивного счетчика задания амплитуд, к входам которого подключены выход элемента совпаде„ ния, генераторы случайной двоичной после довательности управления частотой непосредственно, а управления амплитудой через триггер управления, выходы делителя частоты через устройство управления коэффициентом деления подключены к входам дешифратора и через блок управления регистром сдвига к входу регистра сдвига, введены последовательно соединенные генератор синхроимпульсов, синхронизатор, генератор управляющих импульсов, формирователь импульсов, запоминающий блок, регистр и дещифратор, причем выход генератора управляющих импульсов соединен с управляющим входом запоминающего блока и с входом в нулевое состояние регистра, при этом второй выход синхронизатора подключен к входу задающего генератора импульсов, а выходы дополнительного дещифратора сое-динены со соответствующими входами коммутатора.

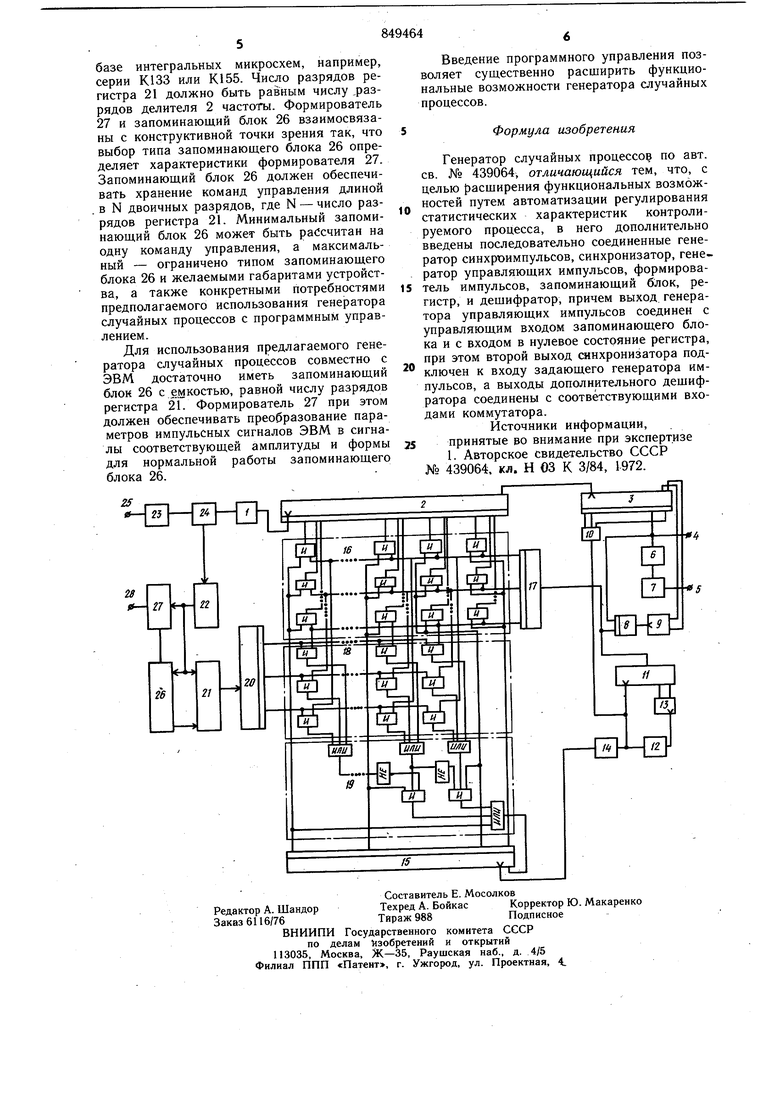

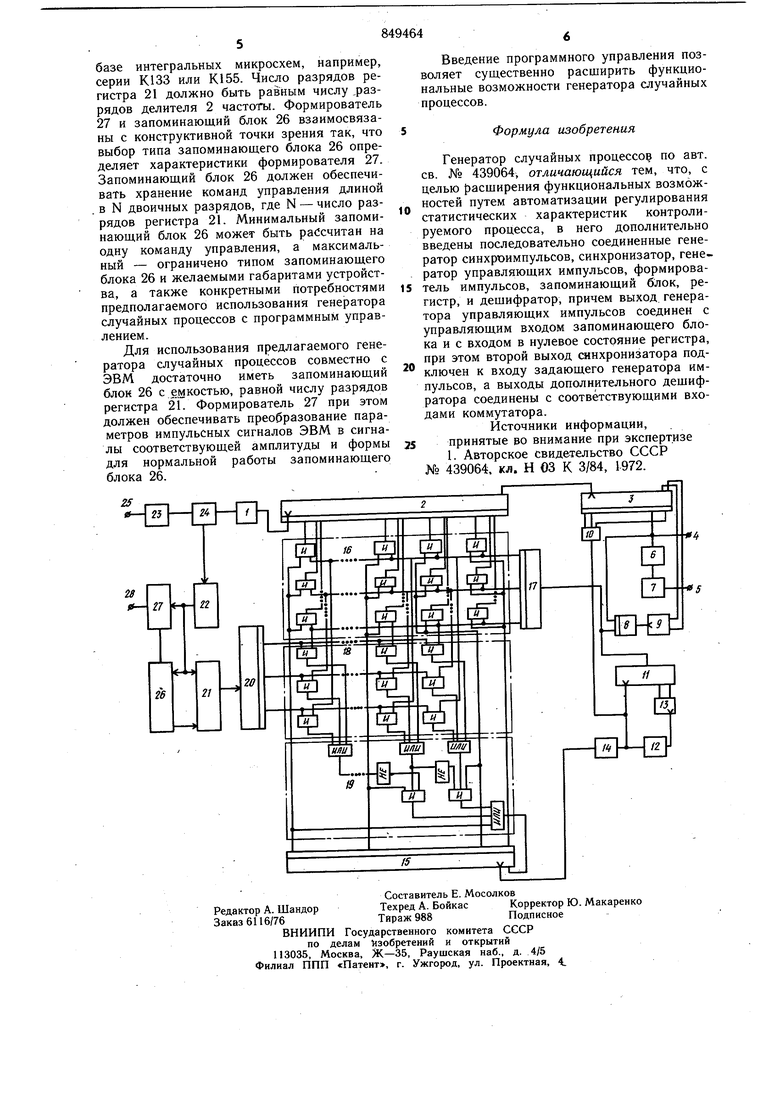

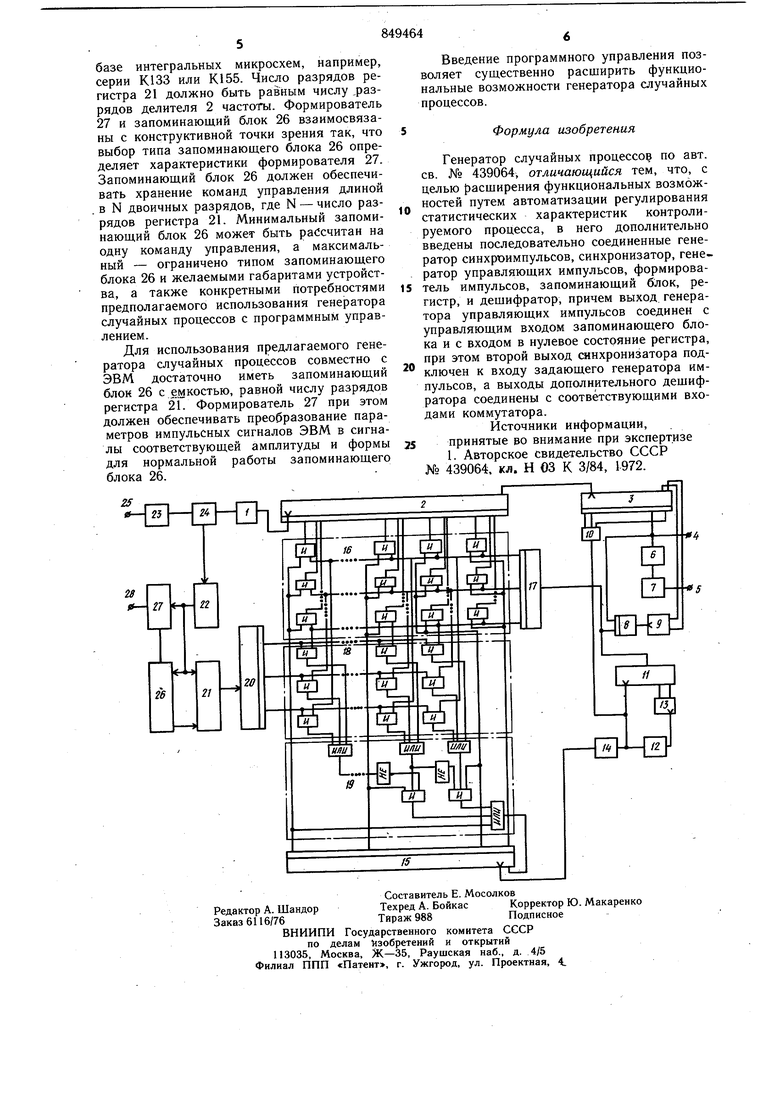

На чертеже изображен предлагаемый генератор.

Генератор случайных процессов содержит задающий генератор 1 импульсов, делитель 2 частоты с управляемым коэффициентом деления, реверсивный счетчик 3, щины 4 и 5 цифрового и аналогового выхода, преобразователь 6 код-аналог, фильтр 7 нижних частот, цифровой компаратор 8, триггер 9, элемент 10 совпадения, реверсивный счетчик 11 задания амплитуды, генератор 12 случайной двоичной последовательности управления амплитудой, триггер 13 управления,генератор 14 случайной двоичной последовательности управления частотой, регистр 15 сдвига, блок 16 управления коэффициентом деления, дешифратор 17, коммутатор 18, который выполнен на элементах И, блок 19 управления регист зом 15 сдвига, дешифратор 20, регистр 21, Генератор 22 управляющих импульсов, генератор 23 синхроимпульсов, синхронизатор 24, щина 25 синхронизации, запоминающий блок

26, формирователь 27 импульсов, щина 28 ввода программы управления.

Устройство работает следующим образом.

Генератор 23 синхроимпульсов с внешней синхронизацией от щины 25 запускает синхронизатор 24, первый выход которого подключен к задающему генератору 1 импульсов, а второй выход к входу генератора 22. Генератор 22 вырабатывает серии управляющих импульсов, запускающих формирователь 27, запоминающий блок 26, и устанавливающих в нулевое состояние регистр 21. При этом на части входов коммутатора 18, подключенных к выходу регистра 21 через дещифратор 20, управляющие сигналы отсутствуют и коммутатор 18 отключает блок 19 управления регистром 15 сдвига, который устанавливается в нулевое состояние и запирает логические элементы блока 16 управления коэффициентом деления, что приводит к запиранию делителя 2 частоты и отсутствию сигналов на его выходе. При этом обеспечивается режим ввода программы управления от щины 28 через формирователь 27 в запоминающий блок 26. По окончании ввода программы управления генератор 22 отключает формирователь 27 и переходит в режим обработки программы управления, при котором на каждую команду управления формируется цикл случайного процесса с характеристиками, заданными командой управления в двоичном виде. При этом генератор 22 выдает сигнал на управO ляющий вход запоминающего блока 26 для считывания команды управления в регистр 21, вход которого подключен к выходу запоминающего блока 26. Команда управления переводит регистр 21, и последовательно с ним соединенный дещифратор 20 в такое состояние, при котором на единицу в разряде регистра 21 соответствует наличие сигнала на выходе дешифратора 20 и первых входах элементов И коммутатора 18, а отсутствие единицы, т. е. нуль, приводит

0 к отсутствию выходного сигнала соответствующего разряда. В зависимости от команды состояние регистра 21 изменяется, что приводит к возбуждению соответствующих выходов дещифратора 20 и отпиранию соответствующих элементов И коммутатора -18. При этом на входах блока 19 управления регистром 15 сдвига появляются управляющие сигналы, приводящие в соответствующее состояние регистр 15 сдвига с выхода которого сигналы подаются на

- блок 16 управления коэффициентом деления, что приводит к соответствующему изменению коэффициента деления делителя 2 частоты, выходные сигналы которого подаются на вход реверсивного счётчика 3, формирующего случайный процесс в цифровом

5 виде на щине 4.

Формирование циклов случайных процессов происходит столько раз, сколько команд содержится в программе управления. При переходе от i-й команды управления

- к (1 + 1)-й команде управления генератор 22 выдает сигнал на сброс регистра 21 в начальное состояние, при этом генерация случайного процесса прекращается, и сигнал на запоминающий блок 26 на вызов (И-1)-й команды в регистр 21. Перевод

5 регистра 21 в состояние (1-ь1)-й команды управления приводит к генерации случайного процесса с параметрами, соответствующими (i-fl)-и .команде управления. Генерация случайных процессов прекращается с окончанием цикла выдачи случайного процесса, соответствующего последней команде управления, хранящейся в запоминающем блоке 26. При этом генератор 22 сбрасывает регистр 21 в начальное состояние и включает формирователь 27, что соответствует режиму ввода программы управления.

Регистр 21 и дешифратор 20 могут быть

выполнены аналогично широко применяемым

в вычислительной технике устройствам на

Авторы

Даты

1981-07-23—Публикация

1979-10-12—Подача