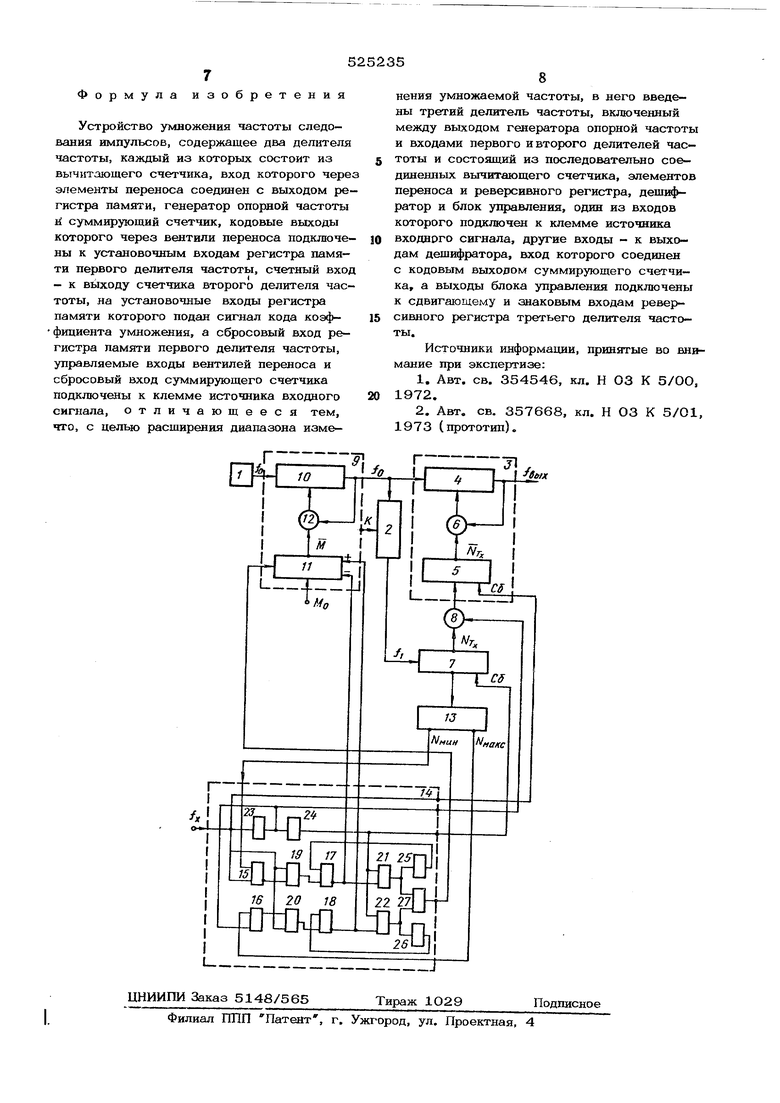

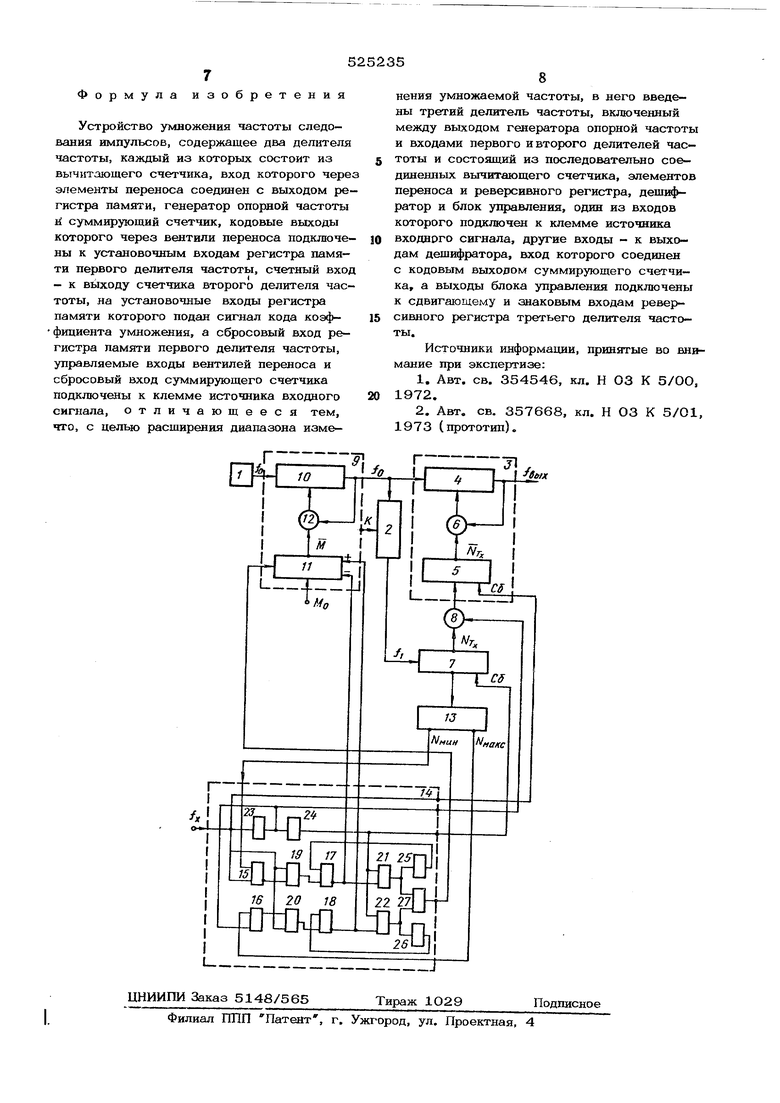

(54) УСТРОЙСТВО УМНОЖЕНИЯ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ На чертеже дана структур1гая электрическая схема предлагаемого устройства. Устройство содержит генератор 1 опорной частоты, два делителя частоты 2 и 3, каждый из которых содержит вычитающий счетчик 4, регистр памяти 5 и элементы 6 переноса кода по числу разрядов счетчика суммирующий счетчик 7 импульсов и вентйли 8 перенсюа кода, В устройство дополнительно введены третий делитель частоты 9, состоящий из вычитающего счетчика 10, реверсивного;регистра 11 и элементов 12 переноса кода, дешифратор блок 14 управления на логических элементах. Блок управления 14 содержит четыре триггера 15-18 с раздельными входами, четыре элемента И 19-22,четуре элемен та задержки 23-26 и элемент ИЛИ 27. Работает устройство следующим образом Выходные импульсы генератора 1 с высокой частотой JQ поступают на вход делит ля --МСТОТЫ 9, в реверсивный регистр 11 которого введен код коэффициента деления, равного Мц 1, если производится ум гожение максималыю возможной или неизвестно частоты. Если значение входной частоты известно, то в реверсивный регистр 11 вво дится коэффициент деления М, соответст- вуюший поддиапазону, в котором находится значение входной частоты. Обратный код М реверсивного регистра 11 каждым импульсо с выхода вычитающего счетчика Ю перепи сывается в него через элементы переноса 12 После списания из вычитающего счетчика 1О записанного в него числа на его выходе появляется импульс, повторяющий процесс деления. С выхода делителя: часто ты 9 на входы делителей частоты 2 и 3 поступают импульсы с частотой F,(1) где М MO ДМ - коэффициент деления делителя частоты 9, В делителе частоты 2 эта частота делится на коэффициант умнож ния устройства К. На вход суммирующего счетчика 7 поступают импульсы с частотой i-T-b 2) На сбросовый вход суммирующего счетчика 7 ностулают импульсы входной частоты f задержанные в элементах задермски 23 и 24. В. результате этого в регистре памят 5 формируется код, пропорциональный пери ду Tg входной частоты NT TK-fi(5) Этот код по сигнйлу управления с выхода элемента задержки 23 переписывается чер вентили перелоса 8 в регистр памяти 5 де пителя частоты 3, предварительно очище ш го импульсом входной Частоты. Обратный код N/I.JJ из регистра памяти 5 камщым импульсом с выхода вычитаюнюго счетчика 4 переписывается через элементы переноса 6 в вычитающий счетчик 4, предварительно установленный в состояние 2 (где П - число разрядов двоичного счетчика). После списания числа из вычитающего счетчика 4 на его выходе появляется импульс. На выходе делителя частоты 3 образуются импульсы выходной частоты устройства f bu - -fx1) к кодовым выходам суммирующего счетчика 7 иодключен дещифратор 13 на два положенйя. Первое дешифрируемое значение кода в суммирующем счетчике 7 ( N мин ) выбирается в зависимости от. требуемой точности Д Дискретности) для минимального зйачення периода входной частоты ТииН -FI ,С5), , где F - коэффициент пропорциональности, численно равный значению частоты на входе суммирующего счетчика 7, при которой для минимального периода входной частоты в нем образуется код, отвечающий требованиям заданной точности. Второе дешиф1- i рируемое гжачение кoдaN макс выбирается вдвое большим, т. е, равным Ммлкс 2Т «н.(6) Объем счетчиков 4,7 и регистра памяти 5 выбирается с небольщим запасом по сравнению с N макс, например на один дополнительный разряд, с целью учета динамики изменения периода входной частоты. Если умножение начинается с близкой к максимальной входной частоте, токоэффициент деления делителя частоты 9 устанавливается равным Мц 1, При этом в суммирующем счетчике 7 образуется код, находящийся в диапазоне N макс N т N мин. т, е. умножение производится с точностью, равной или превыщающей заданную. При уменьшении входной частоты f код в суммирую щем счетчике 7 увеличивается и при увеличении периода входной частоты вдвое-по сравнению с минимальным периодом он достигает величины МмАкс-При этом на соответствующем выходе дещифратора 13 появляется сигнал, по которому блок управления 14 вырабатывает два сигнала (сначала сигнал направлений сдвига, а затем сигнал сдвига), поступающие на входы реверсивного регистра 11 в делителе частоты 9, Сигнал сдвига сдвигает влево единицу, предварительно записанную в реверсивном регистре 11, и коэффициент деления делителя частоты 9 увеличивается вдвое и становится равным . В результате этого шторная частоты уменьшается вдвое ,и на вход суммио э ,11 на рующего счетчика 7 начинают поступать ик пульсы с частотой . вдвое меньшей, чем ь предыдущем такте. Соответственно уменьшается и код.,формируемый в сумми(Рующем счетчяке 7. При дальнейшем умен |шении входной частоты, когда период увел чиБ8.ется в 4 раза по сравнению с минимал |ным и в 2 раза по сравненшо с тем, что бып в момент предыдущего переключения, ,код в суммирующем счетчике 7 вновь стайовится равным . и сагнал с дешЦ ратора 13 через блок 14 производит I новый сдВйГ едипщы в реверсивном ре:гнстре 11, ь результате чего коэффициент деления делгггелк частоты 9 увеличивается еще вдвое и становится равным , Частота на входе суммирующего счетчика 17 уменьшаетса вдвое относительно пред- шествующей. Аналогично работает устроЙЕство и дальше, каждый раз увеличивая;КОэф Й)ИЦиент деления делителя частот-ы 8 вдэое при гфевышении кодом М., Iзаданного .аода jW fticc i При yeoiiiiqeHffli входной частоты код НчiB суммгфухощем счетчике 7 начинает умень ,шаться, и при соответствую ,я1ем выходе дешифратор.з 13 появляется Iсигнал, по которому в блоке управления 114 вырабатывает-ся сигнал изменения непра {ленйя сдвига и импульс сдвига регистра 11 :умекыиающий вдвое код коэффициента деления делителя частоты 9. Соответственно на Входе сум шрующего счетчика 7 вдвое увеянчйвается частота f 1,и код в нем снси ва находится в пределах|Мудк5. обес|печивай требуемую то оюсть, С учетам динамики необходимо выбирать нескога ко большик; по сравнению с кодом, выбран- из соображений требуемой точности в с-л-атике, При дальнейшем увеличении входной частоты каждый раз,, когда значение кода-в j суммирующем счетчике 7 становится fira., с дешифратора 13 через |блок управления 14 производится увеличе- |ние )4JHUHeHTa деления делителя частоты 9 вдвое. Благодаря тому, что опорная частота д является промежут-ощюй в устрой;CTBei ее изменение в процессе работы не .влинеч иа })езультат умноже} ия. Сдан из вариантов блока управления 14 работает следующим образом. ЕСЛИ код в суммирующем счетчике изменяемся в пределах Мкл1сс Мт Миин то каждым входным импульсом I триггеры 15 и 16 устанавливаются в нулевое состояние. При этом открывается элемент И 19, но так как до прихода следующего импулг са входной частоты появляется сигнал NMHH с ден1ифр 1тора 13, то триггер 15 переходит ,в еддашчное состояние и с управлжощего :BTior-j племей-а И 19 снимается разрешаю ший погглшиал. В результате этого через элементы И 19 и 20 не проходят сигналы, JH блок управления 14 не вырабатывает сигнала сдвига. Если же после установки триггеров 15 и 16 входным импульсом |- в нулевое состояние на единичном входе триггера 10 появляется сигнал мякс. с выхода дешифратора 13, что соответствует увеличению вдвое текущего периода ло сравнению с бывшим до переключения, то триггер 16 подготавливает своим единичным выходом элемент И 20, через который следующий входной импульс f проходит на нулевой вход триггера 18. Потенциал с нулевого выхода триггера 18 поступает на реверсиЕУный регистр 11, определяя направление его сдвига влево, т. е, в сторону увеличения коэффициента деления делителя частоть 9, (Нулевой выход триггера 18 подготавливает элемент И 22, через который проходит входной импульс f , задержанный в элементах задержки 23 и 24, на вход элемента ИЛИ 27, а с его выхода на сдвиговый вход реверсивного регистра 11. Выходной сигнал элемента И 22 через элемент задержки 26 возвращает триггер 18 в еди ничнов состоял1ие, снимающее с его выхода открывающий сигнал на элемент И 22. Если же после установки триггеров 15 и 16 входным импульсом fj в нулевое состо$шие на единичном входе триггера 15 не появ1 тся сигнала , что соответствует уменьшеншо вдвое текущего периода по сравненшо с предшествующим, то элемент И 19 остается подготовленным к срабатыванию, и очередной импульс входной частоты проходит через элемент И 19 на единичный вход триггера 17, который своим едшжч ным выходом подготавливает элемент И ,21 Импульс входной частоты, задержанный в элементах задержки 23 и 24, проходит через элемент И 21 на вход элемента ИЛИ 27, а с его выхода - на сдвиговый вход реверсивного регистра 11. С выхода |триггера 17 на знаковый вход реверсивно;ГО регистра 11 поступает сигнал, опрсделя1и|щий сдвиг в реверсивном регистре 11 кода Iвправо, уменьшающий коэффициент деления ;делителя частоты 9 вдвое. Выходдюй сигнал |элеме та И 21 через элемент : эадержки 25 возвращает триггер 17 в единичное счс{тояние, снимающее с iero выхода открыпою:ший сигнал на элемент И 21. Такое построение устройства |1о:шоля ;т значительно расширить вниз диапазон ипм.-ения умножаемой частоты с сохраненном требуемой точности преобразования пориодн |на всем диапазоне при оптимал шом OOI.O.M оборудования.

Формула изобретения

Устройство умножения частоты следования импульсов, содержащее два делителя частоты, каждый из которых состоит из вычитающего счетчика, вход которого через элементы переноса соединен с выходом регистра памяти, генератор опорной частоты и сутимирующий счетчик, кодовые выходы которого через вентили переноса подключены к установочным входам регистра памяти первого делителя частоты, счетный вход - к выходу счетчика второго делителя частоты, на установочные входы регистра памяти которого подан сигнал кода коэффициента умножения, а сбросовый вход регистра памяти первого делителя частоты, управляемые входы вентилей переноса и сбросовый вход суммирующего счетчика подключены к клемме источника входного сигнала, отличающееся тем, что, с целью расщирения диапазона изменения умножаемой частоты, в него введены третий делитель частоты, включенный между выходом генератора опорной частоты и входами первого и второго делителей частоты и состоящий из последовательно соединенных вычитающего счетчика, элементов переноса и реверсивного регистра, дещифратор и блок управления, один из входов которого подключен к клемме источника

входного сигнала, другие входы - к выходам дещифратора, вход которого соединен с кодовым выходом суммирующего счетчика, а выходы блока управления подключены к сдвигающему и знаковым входам реверсивного регистра третьего делителя частоты.

Источники информации, принятые во внимание при экспертизе:

1.Авт. св. 354546, кл. Н 03 К 5/00,

1972.

2.Авт. св. 357668, кл. Н 03 К 5/01, 1973 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для дифферинцирования частотно-импульсных сигналов | 1975 |

|

SU526916A1 |

| Частотно-импульсный функциональный преобразователь | 1975 |

|

SU543945A1 |

| Устройство умножения частоты следования импульсов | 1975 |

|

SU528695A1 |

| Устройство цифрового задания частоты следования импульсов | 1976 |

|

SU641455A1 |

| Цифровой частотомер | 1975 |

|

SU783701A1 |

| Цифровой умножитель частоты | 1987 |

|

SU1596444A1 |

| Цифровой умножитель частоты следования импульсов | 1982 |

|

SU1034146A1 |

| Устройство для умножения частоты следования импульсов | 1974 |

|

SU517163A1 |

| Устройство для измерения нелинейности пилообразного напряжения | 1986 |

|

SU1406528A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU991614A2 |

Авторы

Даты

1976-08-15—Публикация

1975-04-21—Подача