1

Изобретение относится к имстульсной технике.

Известен частотный компаратор 1, который содержит генератор импульсов, счетчик, формирователи, группы веитилей, схему сборки, схему И, ключи и триггеры. В одном из иериодов сравнивается период контролируемой частоты с меньшим допуском (соответствуюпдим верхией частоте), а в следующем периоде - с большим допуском (соответствующим нижней частоте).

Наиболее близким по техгнической сущности к изобретению является частотный компаратор, содержащий счетчик импульсов, одни вход которого соединен с генератором импульсов, а другой через формирователи импульсов- со в;ходом компаратора, два триггера, первые выходы которых соедИНеньг с выходами устройства, а вторые через логический элемент И - с третьим выходом устройства, три логических элемента И-НЕ, выходы 1которых соедииены с соответствующими входами упОМянутьгх триггеров, причем один вход каждого из логических элементов И-НЕ связан с выходом входного формнрователя импульсов, а второй вход первого из этих элементов через инвертор соединен со вторым входом третьего логического элемента И-НЕ и подключен к входам уиравления счетчика

2. Такой компаратор ие обеспечивает достаточного быстродействия.

Нелью изобретения является новып1ение быстродействия. Поставленная цель достигается тем, что в компаратор введс-ны два блока сравнения кодов, логическ11И элемент ИЛИ, счетный триггер и лонолн11тел1Я1Ы1 1 логИЧеский элемент П-НЕ, npH4eNi одпи входы блоков сравне1И1я кодов соединены с источниками кодов, вторые входы поразрядно- с выходами счетчика, а входы управления-с выходами счетного триггера, выходы блоков сравиеиИЯ кодов подключены ко входам логического элемента НЛП, выход которого соединен с одним СЧСГНОГО Тр)1Ггера и одним входом доиолнитсльного логического элемента П-НЕ; второй вход этого элсмеита Н-НЕ соединен с иервЫМ выходом счетного триггера и третьнм входом первого логичеекого элe ;cнтa П-НЕ, при этом выход дополнительного логического элемента П-НЕ связаи со входами унравленИЯ счетчиком, второй вход счетного триггера-с формирователем ими}льсов. а его второй выХод--со вторым входом второго логического элемента Н-НЕ.

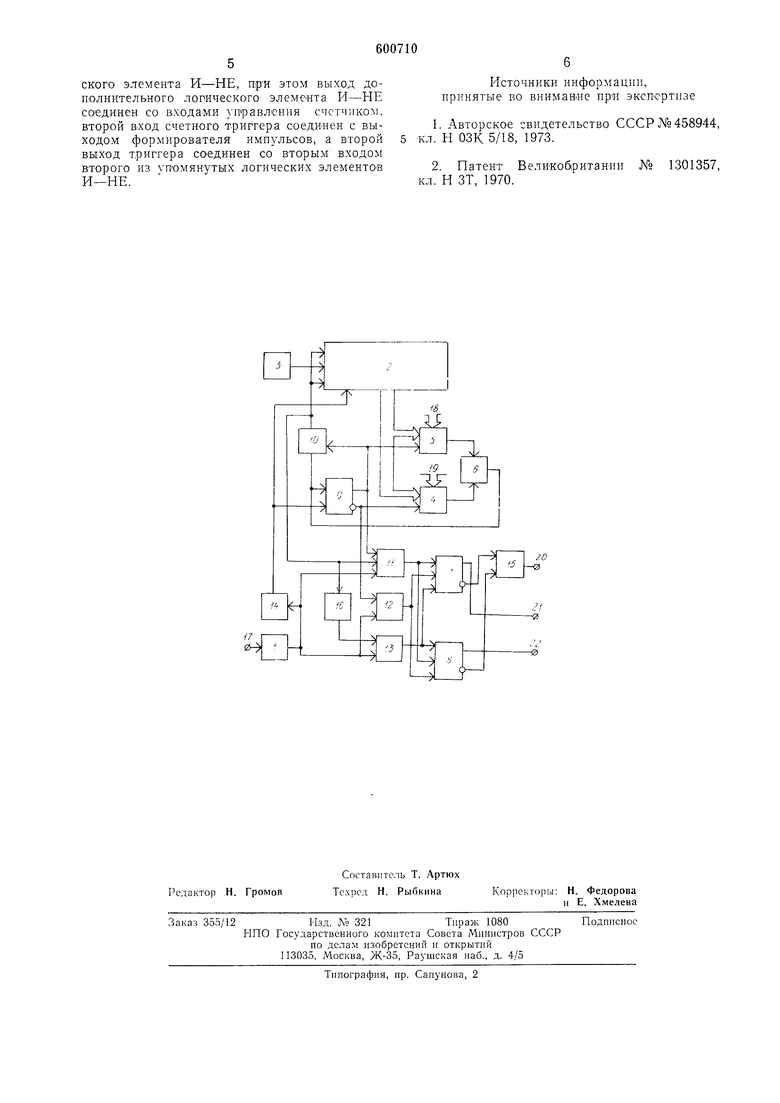

Структурная электрнчеекая схема нредлагаемого компаратора приведена на чертеже.

Комг аратор содержит входной формирователь 1, ечетчик имп льеов 2, генератор Импульсов 3, блоки сравнения кодов 4 5, ЛОгический элемент ИЛИ 6, триггеры 7 и 8, счетный триггер 9, логические элементы И-НЕ 10-13, формирователь имиульсов 14, логический элемент И 15 и инвертор 16. Входной сигнал подается на вход 17, а сигналы установки кодов-на входы 18 И 19. Выходные сипналы снимаются с выходов 20-22.

Работа устройства рассматривается для случая древышенИЯ контролируемой частоты FX значения верхнего доиуска. В момент окончания очередного периода контролирземой ча стоты FX счетчИК ИМлульсов 2 и счетный триггер 9 имнульсом с выхода формирователя 14 устанавливается в ноль, и начинается заполнение счетчика 2 имнульсами с выхода генератора 3. К мОМенту окончания следующего нериода частоты FX состояние счетного триггера 9 не меняется (так как число в счетчике 2 не достигает значения кода, соответствующего верхнему пределу частоты FX), и в момент окончания этого периода имлульс с выхода формирователя 1 поступает на логический элемент 12 И-НЕ, открытый разрещающим нотенциалом с нулевого выхода триггера 9, а импульс с выхода элемента 12 устанавливает тр-иггеры 7 и 8 (предыдущее состояние триггеров не рассматривалось) в ноль, в результате чего на выходе 20 лолического элемента 15 И, на входы iKOiTOporo поступают единичные сигналы с выходов триггеров 7 И 8, появляется сигнал «Больще, указывающий, что контролируемая частота FX иревыщает значение верхнего допуска. Если значение частоты F не меняется, то каждый раз в момент оконча.ния периода частоты FX импульсом с выхода логического элемента 12 И-НЕ подтверждается нулевое состояние триггеров 7 1И 8.

Когда значение частоты F ниже верхнего допуска di: , то до окончания периода понизившейся частоты FX на выходе блока 4 сравнения кодов появляется импульс, поступающий на вход логического элемента 6 ИЛИ и затем на вход счетного триггера 9, который по окончании постунившего импульса иереключается в единичное состояние, в результате чего разрещающий сигнал на выходе логического элемента 10 И-НЕ остается, логический элемент 12 И-НЕ запирается, а логический элемент 11 И-НЕ отпирается. В момент окончания периода частоты FX импульс с выхода логического элемента 11 И- НЕ устанавливает триггер 7 в единичное состояние и подтверждает нулевое состояние трИггера 8. Сигнал на выходе 20 исчезает и появляется на выходе 21. Это значит, что частота jp;v находится в диапазоне, ограниченном установленными допусками. Если значение частоты FX не меняется, то каждый раз в момент Окончания периода частоты FX импульсом с выхода логического элемента 11 и-НЕ и подтверждается единичное состояние триггера 7 и нулевое состояние триггера 8. Когда частота FX меньще нижнего допуска

dz: , то до окончания периода этой еще более низкой частоты FX сначала появляется импульс на выходе блока 4 сраВ|Нения кодов, переключающий счетный триггер 9 в единичное состояние, а затем при равенстве числа в счетчике импульсов 2 и значению кода нижнего допуска - единичный потенциал на выходе блока 5 сравнения кодо;в, который поступает на первый ВХод логического элемента

И-НЕ 10, открытого по второму входу разрешающим потенциалом с единичного выхода счетного триггера 9. На выходе элемента 10 устанавливается нулевой сигнал, в результате чего счетчик 2 запирается и на выходе блока 5 фиксируется единичный потенциал. Логический элемент И-НЕ 11 запирается, а логический элемент 13 И-НЕ отпирается сигналом с выхода инвертора 16. В момент окончания периода нового значения частоты FX

импульс с выхода элемента 13 устанавливает триггер 8 в единичное состояние, а триггер 7 - в нулевое. Сигнал на выходе 22 указывает, что частота FX меньше значения нижнего допуска.

При увеличении частоты FX изменение состояния триггеров 7 и 8 и переключение сигнала на выходах 20-22 происходит в обратном порядке.

Ф о р м у л а и 3 о б р е т е н и я

Частотно-импульсный дОПусковый компаратор, содержащий счетчик импульсов, один вход которого соединен с генератором импульсов, другой вход через формирователи

импульсов соединен со входом устройства, два триггера, первые выходы которых соединены с выходами устройства, а вторые выходы через логический элемент И соединены с третьим выходОМ устройства, три логических

элемента И-НЕ, (Выход каждого из которых соединен со входами упомянутых триггеров, причем один вход каждого и-з логических элементов И-НЕ соединен с входом входного формирователя импульсов, а второй

первого из этих логических элементов И-НЕ соединен со вторым входом третьего логического элемента И-НЕ через инвертор и подключен к входам управления счетчика, отличающийся тем, что, с целью повыщения быстродействия, в него введены два блока сраВ1нения кодов, логический элемент Р1ЛИ, счетный триггер и дополнительный логический элемент И-НЕ, причем одни входы блоков сравнения кодов соединены с источникамн сигналов кодов, вторые их входы соединены поразрядно с выходами счетчика, а входы управления бЛОков сравнения кодов соединены с выходами счетного триггера, выходы блоков сравнения кодов подключены ко

входам логического элемента ИЛИ, выход которого соединен с одним выходом счетного триггера и олним входом дополнительного логического элемента И-НЕ, второй вход которого соединен с первым выходом счетного

триггера и третьим входом первого логичеСКОРО элемента И-НЕ, прИ этом выход дополнительного лопического элеме«та И-НЕ соединен со входами управления счетчиком, второй В:ход счетного триггера соединен с выходом формирователя импульсов, а второй выход триггера соединен со вторым входом второго из упомянутых логических элементов И-НЕ.

6

Источники информации, принятые во виимаНИе ирИ экспертизе

1. Авторское свидетельство СССР №458944, кл. Н ОЗК 5/18, 1973.

№ 1301357,

2. Патент Великобритании кл. Н ЗТ, 1970.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля температуры погружного электродвигателя и давления на приеме насоса | 1989 |

|

SU1652525A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ОТКЛОНЕНИЯ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ | 1990 |

|

RU2029312C1 |

| СПОСОБ ИЗМЕРЕНИЯ СКОРОСТИ ВРАЩЕНИЯ ВАЛА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2017156C1 |

| Устройство для измерения частоты и периода | 1991 |

|

SU1824592A1 |

| Аналого-цифровой преобразователь с промежуточным преобразованием в частоту | 1989 |

|

SU1644382A1 |

| Устройство для защиты погружного электродвигателя от перегрузки и анормальных режимов | 1990 |

|

SU1777198A1 |

| Устройство допускового контроля временных интервалов | 1991 |

|

SU1798720A1 |

| Устройство определения временного положения импульсных сигналов | 1988 |

|

SU1596301A1 |

| Устройство для измерения времени установления выходного сигнала цифроаналогового преобразователя | 1979 |

|

SU790298A1 |

| Устройство для измерения температуры | 1987 |

|

SU1506298A1 |

Авторы

Даты

1978-03-30—Публикация

1976-03-03—Подача