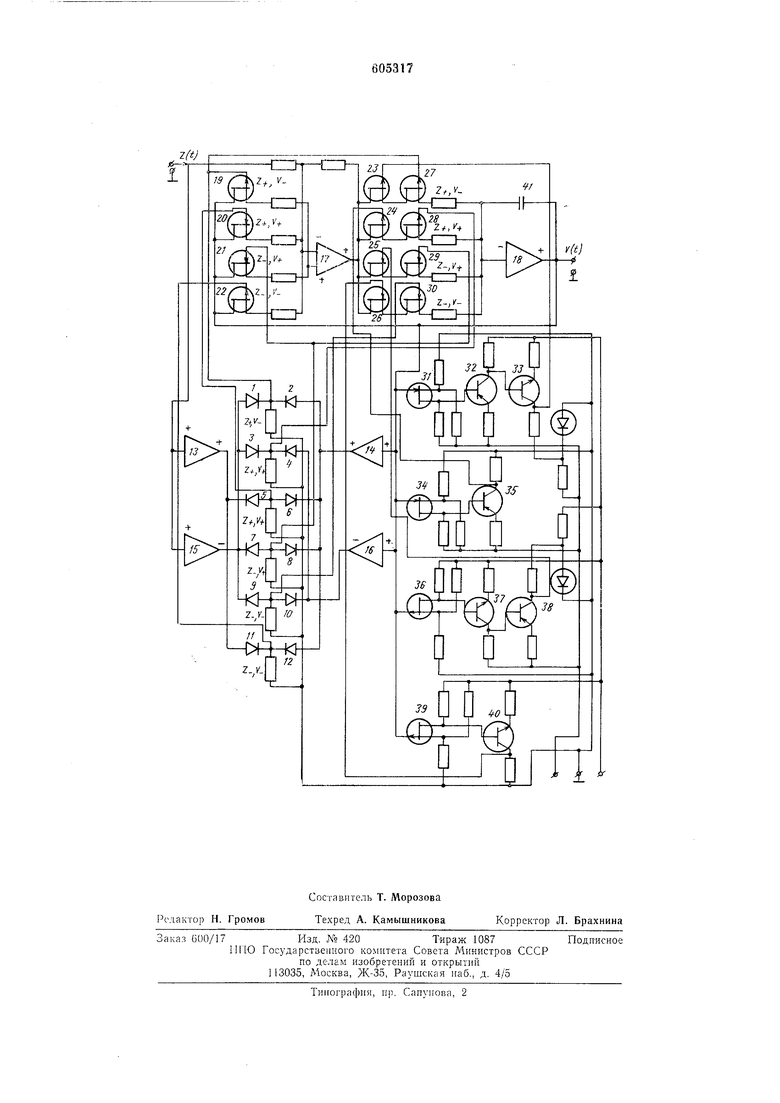

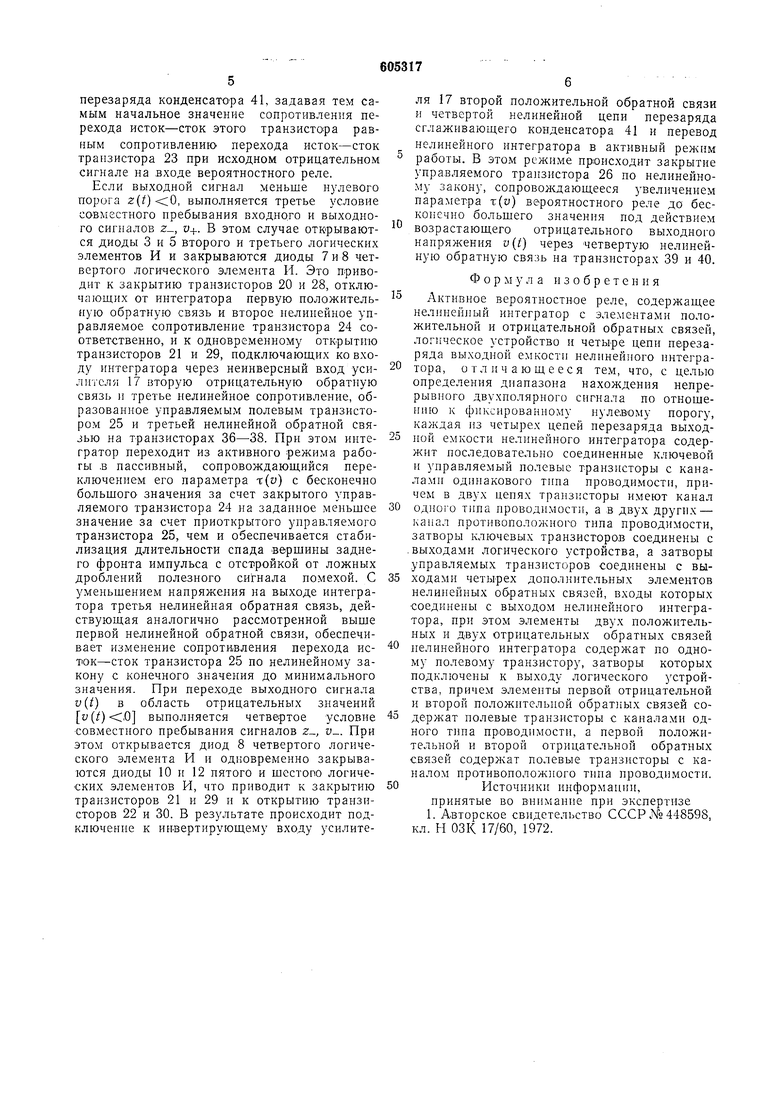

Устройство содержит логическое устройство, образованное шестью логическими элементами И на диодах 1 - 12, управлясдмых входным z(t) и выходным v(t) сигналами через неинвертирующие усилители ностоянного тока 13 и 14 и инвертирующие усилители постоянного тока 15 и 16. Кроме того, в схему реле входят усилитель постоянного тока 17 входного и выходного сигналов, нелинейный интегратор, собранный на усилителе постоянного тока 18, ключевые нолевые транзисторы 19-22, управляемые нолевые транзисторы 23-26, ключевые полевые транзисторы 27-30, транзисторы 31-40 и конденсатор 21.

Работа устройства основала на определении логическими элементами на диодах 1-12 зоны пребывания входного z(t) и выходного v(t) сигналов по отношению к нулевому порогу и подключении с помощью ключевых транзисторов 19-22 и 27-30 к интегратору цепи отрицательной или положительной обратных связей и соответствующей нелинейной цепи переразряда сглаживающего конденсатора 41. Обозначим через 2+ и Z- пребывание входного. сигнала z(t) выше z()0 и ниже z(i;)0 нулевого порога, а через w+, V- - пребывание выходного сигнала v(t) выше v(t)Q и ниже v(t).0 нулевого порога. При этом образуются следующие четыре области совместного пребывания входного z(t) и выходного v(t) сигналов по отношению к пулевому пороговому значению: г+, z+, v+; z, и+; z, и.

В исходном состоянии при наличии ла входе сигнала отрицательной полярности z(t)Z- конденсатор 41 заряжен до входного отрицательного напряжения. Ключевые полевые транзисторы 22 и 30 открыты нулевым потенциалом с выхода шестого и пятого логических элементов И из-за закрытых диодов 11, 12 и 9, 10, а другие ключевые полевые транзисторы 19-21 и 27-29 закрыты из-за открытых диодов 1, 3, 5, 4, 6 и 8 четырех других логических элементов И. Поэтому но входу интегратора через усилитель 17 подключены только вторая положительная обратная связь и управляемый полевой транзистор 26. Этот транзистор закрыт выходным напряжением интегратора через транзисторы 39 и 40 четвертой нелинейной обратной связи, вследствие чего значение параметра Т{У) интегратора бесконечно больщое. Поэтому выходное напрян ение нелинейного интегратора фиксируется на определенном отрицательном уровне, принимаемом за значение - 0,5. Это значение выходного напряжения через транзисторы 31-33 первой нелинейной обратной связи прикладывается к затвору управляемого полевого транзистора 23, задавая ему начальное сопротивление перехода исток-сток, соответствующее конечному значению параметра Т{У).

При поступлении на вход вероятностного реле положительного сигнала, превышающего нулевой порог, выполняется первое условие Z+, V-. совместного пребывания входного и выходного сигналов. При этом только первый элемент И логического устройства, образованный диодами 1 и 2, остается закрытым, а остальные диодные элементы И открыты. Поэтому к интегратору оказываются подключенными с помощью транзисторов 19 и 27 первая отрицательная обратная связь через неинвертирующий вход суммирующего усилителя постоянного тока 17 н первое нелинейное сопротивление, образованное сопротивлением перехода исток-сток транзистора 23 с соответствующей обратной связью на транзисторах 31-33. По мере роста напряжения

V (t) па выходе интегратора приоткрываются трапзисторы 31, 32 и 33 первой нелинейной обратной связи и уменьшается запирающий положительный потенциал на затворе транзистора 23. .При этом сопротивление его перехода исток-сток, а следовательно, и значение параметра т(и) вероятностного реле уменьшается по нелинейному закону с конечного значения до минимального. В момент превышения выходном напряжением v(t) интегратора нулевого порога выполняется второе условие z+, и+ совместного пребывания сигналов. Это приводит к открытию диодов 2, 10 и 12 .первого, пятого и шестого логических элементов И и к закрытию диодов 4 и 6 второго и третьего элементов И. В результате этого закрываются транзисторы 19 и 27 и открываются транзисторы 20 и 28, которые подключают ко входу интегратора первую полол :ительную обратную

связь через инвертирующий вход суммирующего усилителя 17 и второе нелинейное сопротивление, образованное переходом исток-сток полевого транзистора 24 и соответствующей обратной связью на транзисторах

34 и 35. Интегратор переходит в активный режим работы. Быстро растзщее его положительное выходное напряжение открывает полевой транзистор 34 и кремниевый транзистор 35. Положительный потенциал, снимаемый с коллектора транзистора 35, закрывает транзистор 24. Его сопротивление перехода исток-сток увеличивается до бесконечности, что приводит к увеличению значения параметра т(и) интегратора и фиксации выходного напряжения v(t) на определенном уровне, принимаемом за 0,5. Благодаря резкому возрастанию параметра T(U) интегратора при его выходном напряжении, близком к 0,5, схема становится нечувствительной к колебаПИЯМ входного напряжения, вызванным действием помех, и стабильно поддерживает выходное напряжение на этом уровне. При этом зиачении выходного сигнала интегратора полевой транзистор 36 третьей нелинейной обратной связи призакрыт за счет смещения с делителя на резисторах, следовательно, призакрыты и кремниевые транзисторы 37 и 38. Отрицательное напряжение, снимаемое с сопротивления нагрузки транзистора 33, призакрывает полевой транзистор 25 третьей цепи

перезаряда конденсатора 41, задавая тем самым начальное значение сопротивления нерехода исток-сток этого транзистора равным сопротивлению перехода исток-сток транзистора 23 при исходном отрицательном сигнале на входе вероятностного реле.

Если выходной сигнал меньше нулевого порога 2();0, выполняется третье условие совместного пребывания входного и выходного сигналов Z-, V+. В этом случае открываются диоды 3 и 5 второго и третьего логических элементов И и закрываются диоды 7 и 8 четвертого логического элемента И. Это приводит к закрытию транзисторов 20 и 28, отключающих от интегратора первую положительную обратную связь и второе нелинейное управляемое сопротивление транзистора 24 соответственно, и к одновременному открытию транзисторов 21 и 29, подключающих ко входу интегратора через неинверсный вход усилителя 17 вторую отрицательную обратную связь и третье нелинейное сопротивление, образованное управляемым полевым транзистором 25 и третьей нелинейной обратной связью на транзисторах 36-38. При этом интегратор переходит из активного режима работы ,в пассивный, сопровождающийся переключением его параметра т (и) с бесконечно большого значения за счет закрытого управляемого транзистора 24 на заданное меньщее значение за счет приоткрытого управляемого транзистора 25, чем и обеспечивается стабилизация длительности спада вершины заднего фронта импульса с отстройкой от ложных дроблений полезного сигнала помехой. С уменьшением напряжения на выходе интегратора третья нелинейная обратная связь, действующая аналогично рассмотренной выше первой нелинейной обратной связи, обеспечивает изменение сопротивления перехода исток-сток транзистора 25 по нелинейному закону с конечного значения до минимального значения. При переходе выходного сигнала v{t) в область отрицательных значений у (t) .0 выполняется четвертое условие совместного пребывания сигналов z-, v-. При этом открывается диод 8 четвертого логического элемента И и одновременно закрываются диоды 10 и 12 пятого и шестого логических элементов И, что приводит к закрытию транзисторов 21 и 29 и к открытию транзисторов 22 и 30. В результате происходит подключение к инвертирующему входу усилителя 17 второй положительной обратной связи и четвертой нелинейной цепи перезаряда сглаживающего конденсатора 41 и перевод нелинейного интегратора в активный режим работы. В этом режиме происходит закрытие управляемого транзистора 26 по нелинейному закону, сопровождающееся увеличением параметра т(и) вероятностного реле до бесконечно большего значения под действием возрастающего отрицательного выходного напряжения v{f} через четвертую нелинейную обратную связь на транзисторах 39 и 40.

Формула изобретения

Активное вероятностное реле, содержащее нелинейный интегратор с элементами положительной и отрицательной обратных связей, логическое устройство и четыре цепи перезаряда выходной.емкости нелинейного интегратора, отличающееся тем, что, с целью определения диапазона нахождения непрерывного двухполярного сигнала по отношению к фиксированному нулевому порогу, каждая из четырех цепей перезаряда выходной емкости нелинейного интегратора содержит последовательно соединенные ключевой и )правляемый полевые транзисторы с каналами одинакового типа проводимости, причем в двух цепях транзисторы имеют канал

одного типа проводимости, а в двух других -

канал противоположного типа проводимости,

затворы ключевых транзисторов соединены с

выходами логического устройства, а затворы

.управляемых транзисторов соединены с выходами четырех дополнительных элементов нелинейных обратных связей, входы которых соединены с выходом нелинейного интегратора, при этом элементы двух положительных и двух отрицательных обратных связей

нелинейного интегратора содержат по одному полевому транзистору, затворы которых подключены к выходу логического устройства, причем элементы первой отрицательной и второй положительной обратных связей содержат полевые транзисторы с каналами одного типа проводимости, а первой положительной и второй отрицательной обратных связей содержат полевые транзисторы с каналом противоположного типа проводимости.

Источники информации,

принятые во в-нимание при экспертизе 1. Авторское свидетельство СССР №448598, кл. Н ОЗК 17/60, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухпозиционное вероятностное реле(ЕгО ВАРиАНТы) | 1979 |

|

SU830649A1 |

| Активное вероятностное реле | 1978 |

|

SU675602A2 |

| Вероятностное реле на варикапах | 1978 |

|

SU752804A1 |

| Активное вероятностное реле | 1977 |

|

SU657632A2 |

| Помехозащищенное устройство для измерения амплитуды импульсных сигналов | 1977 |

|

SU690399A1 |

| Помехоустойчивый триггер | 1988 |

|

SU1688402A1 |

| Вероятностное реле | 1979 |

|

SU873412A1 |

| Устройство для оценки параметров сигналов и условиях действия помех | 1979 |

|

SU866741A1 |

| Устройство для автоматической регулировки усиления | 1978 |

|

SU748801A1 |

| Спектротрон с внешней обратной связью | 1985 |

|

SU1401572A1 |

Авторы

Даты

1978-04-30—Публикация

1976-03-09—Подача