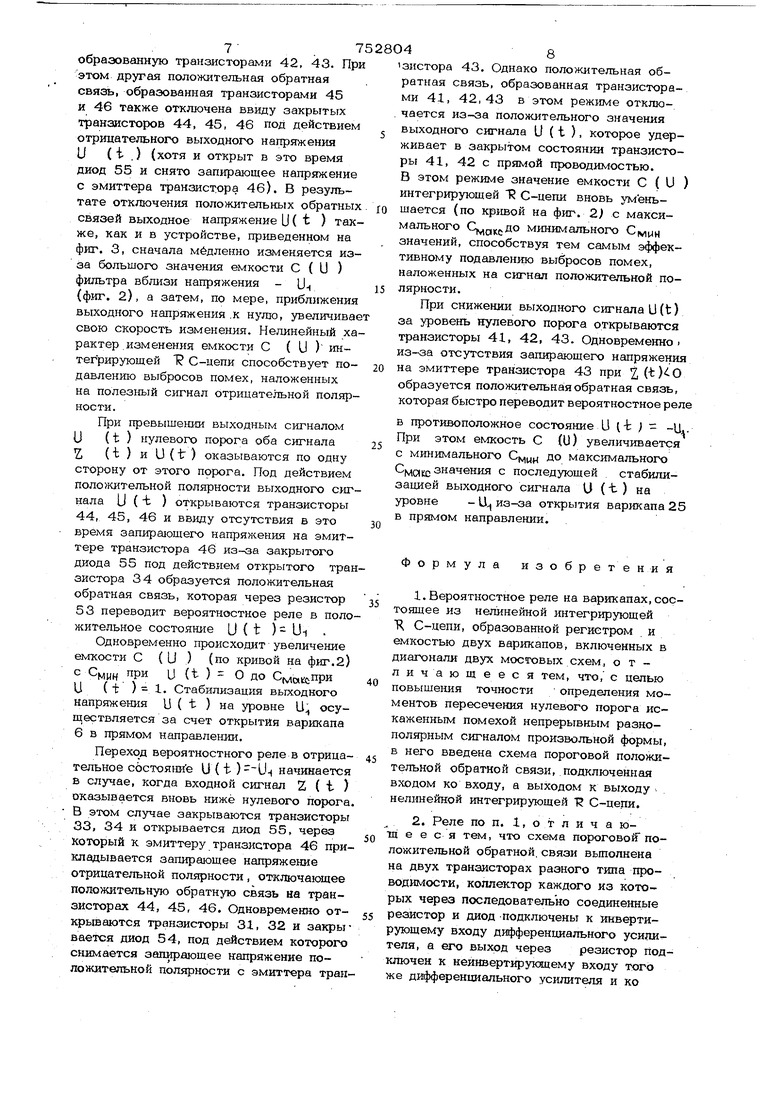

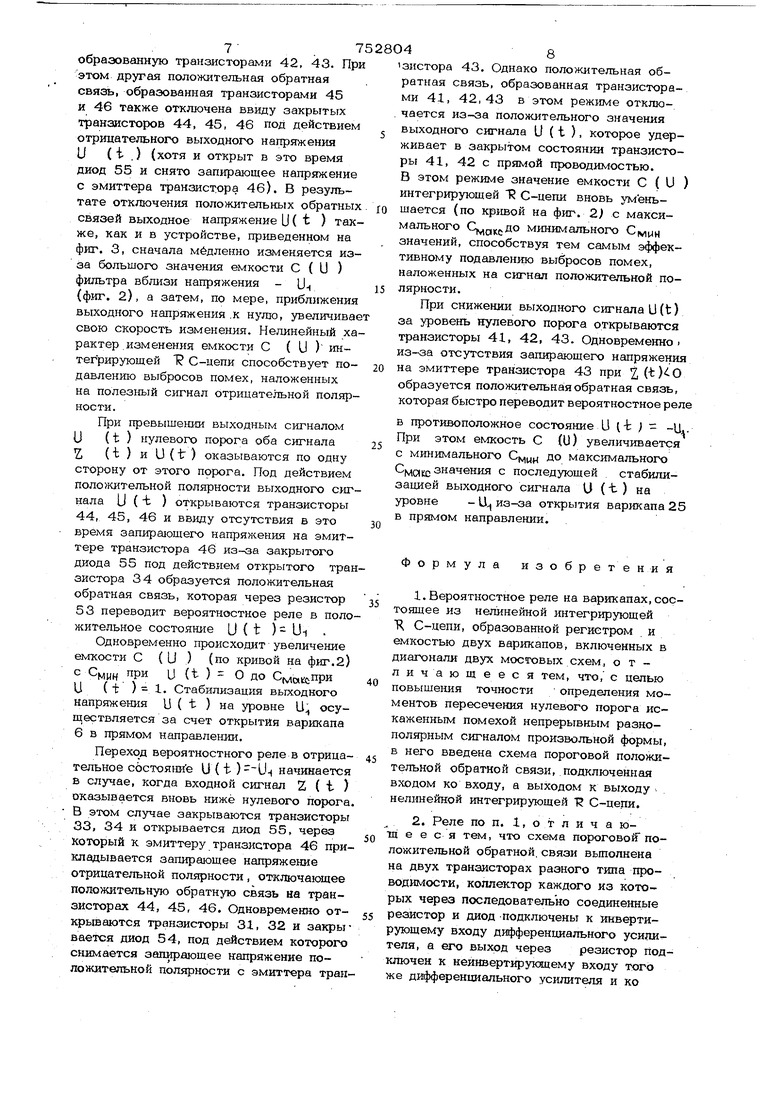

(54) ВЕРОЯТНСХ ТНСС РЕЛЕ НА ВАРИКАПАХ Изобретение относится к определению состояния искаженного помехой непрерывного или импульсного сигнала относительно заданного порога и может быть использовано в системах телеу1ехакики с модуляциями вида ВИМ, ШИМ, ЧИМ, КИМ в измерительной технике, радиолокации. Известно вероятностное реле, содержа щее интегратор на усилителе постоянного тока с попеременно подключенными логкческим устройством отрицательными и положительными .обратными связями, четыре цепи перезаряда сглаживающей емкости, вьшолненной на полевых транзисторах и четьфе нелинеЙ1ые обратные связи, выходы которых соединены с затворами полевых транзисторов цепей перезаряда емкости 1. И естно также вероятностное реле н варикапах, состоящее из нелинейн 5й 1ШтегрирующейТ С-Ч1епи, образованной рез стором и емкостью двух варикапов, шипоченных в диагонали двух мостовых схем 23. Известные схемы обладают небольшой точностью определения моментов пересечения нулевого, порога искаженным помехой непрерывным разнополярным сигналом произвольной формы. Цель изобретения повышение точности определения моментов пересечения нулевого порога искаженным помехой непрерывным разнополярным сигналом произвольной формы. Указанная цель дост11гается тем, что в вероятностное реле на варикапах, состоящее из нелинейной интегрирующей Т С-цепи, образованной резистором и емкостью двух варикапов, включенных в диагонали двух мостовых схем, введена схема пороговой положительной обратной связи, подключенная входом ко входу, а выходом к выходу нелинейной и интегрирующей Т Сцепи, схема пороговой положительной обратной связи вьтолнена на двух транзисторах разного Tima проводимости, коллектор /.аждого из которых через последовательно соединенные резистор и диод подключены к 11нтегр1ф-ующему входу дифференциального усилителя, а его выход через резистор подключен к неинверт1фующему входу того же дифференциального усияителя и ко входу нелкнеыной и интегрирующей R С-цепи, схема положительной обрагпоЛ связи выполнена на двух последовательно вклю ченных ключевых каскадах Hai транзисто рах разного типа проводимости, коллекторы которых через встречно включенны диоды подключены к эмиттерам транзисторов выходных усилителей, причем кол- j5 лекторы транзисторов выходных усилителей через резисторы подключены ко входу нелинейной интегрирующей Т С-цепи, а базы транзисторов выходшых усилителей через эмиттерный повторитель подключены к выходу нелинейной интегрирующей Т С-цепи. На фиг. 1 показана блок-схема вероятностного реле на варикапах, где нелинейная интегрирующая Т С-цепь 1, схема пороговой положительной обратной связи 2; на фиг. 2 - график изменения емкости нелинейной штегрирующей Т Сцепи; на фиг, 3 - принципиальная электрическая схема вероятностного реле на варшсапах диапазона 1ОО кГц - .10 МГц, транзисторы 3, 4, резистор нелинейной, интегрирующей R С-цепи 5, варикапы 6, 7, резисторы 8-11, ключевые транзисторы 12-13, резисторы 14-15, диоды 1617, дифференциальный усилитель 18, резисторы 19-20; на фиг. 4 - принципиаль ная электрическая схема вероятностного реле на варикапах, где транзисторы 21, 22, резисторы 23, 24, варикапы 25, 26

резисторы27-v30, транзисторы 31-34,

резисторы35-4О, транзисторы 41-46,

резисторы47-53, диоды 54-55, резистор 56.Вероятностное реле, приведенное на фиг. 3 . работает следующим образом.

Работа устройства основана-на нелинейном измерении параметра Т ( U ) ( и ) интегрирующей - R С-цепи за счет изменения суммарной емкости . С (У ) двух параллельно включенных варикапов 6, 7 по закону фиг. 2 в зависимости от значения и расположения входного Z (t ) и выходного и ( t ) сигналов по отношению к нулевому порогу с подключением положительной обратной связи в те моменты времени. 7

закрытого от этого напряжения диода 17 становится равным единице, что приводит к отключению положительной обратной связи. Поэтому выходное напряжение

5 и ( t ) сначала медленно нарастает из-за большого значения суммарной ем7СОСТИ С ( и ) варикапов б и 7 (максимального значения емкости варикапа 6, мини: 1ального значения емкости варикапа 7). Затем, по мере y Ieньщeшfя результирующей емкости С .(и ) (по кривой на фиг. 2), скорость нарастания выходного напряжения U (t ) увеличивается и достигает максимального значения вблизи

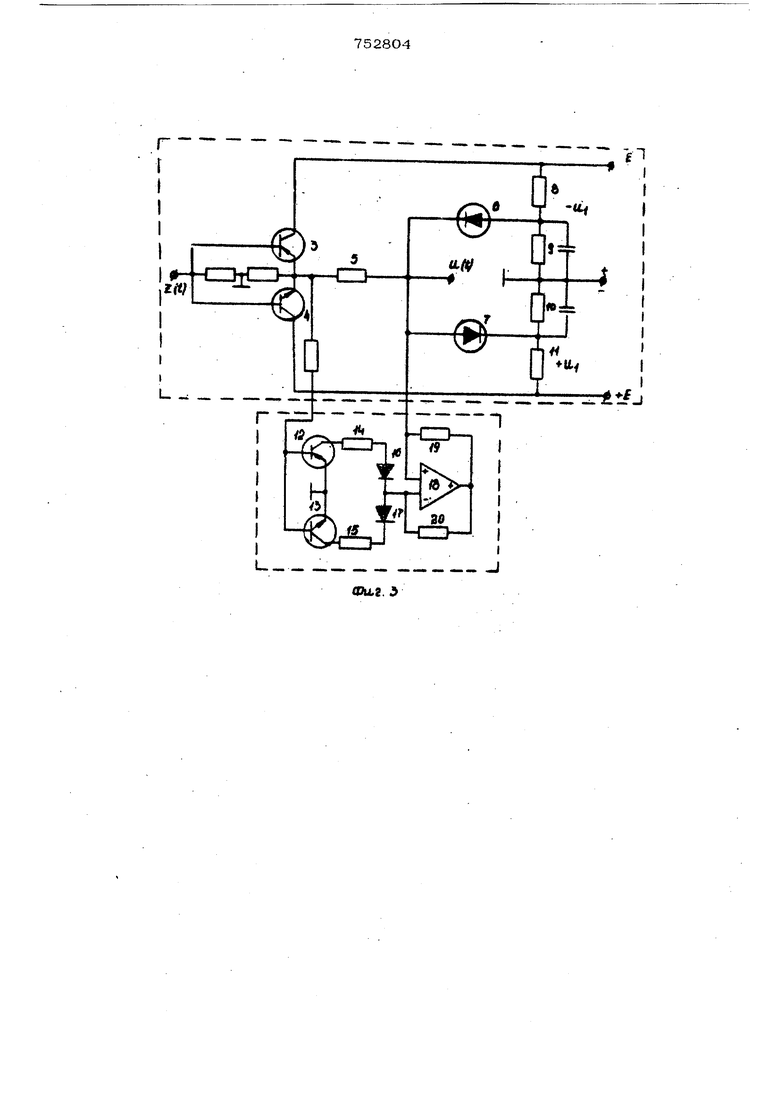

j порога. Такое нелинейное изменение емкости С и ), а следовательно, и параметра t ( U ) ( U ) интегрирующей 1 С-цепи способствует эффективному подавлению выбросов помех, на44когла входной Z (t ) ,4 ьходиой IJ( t , сигналы находятся по одну CToj5o;;y от нулевого порога. В исходном сос1хэяни)1 при действии на,входе устройства сигнала 2 ( Ь ) отрицательной полярности выходное напряжение и ( t ) равно значегшю запирающегю напряжения - U на варикапе 6 (пренебрегаем падением напряжения на самом варикапе). Под действием отрицательного сигнала Z (-t ) открыт ключевой транзистор 12 и закрыт другой ключевой транзистор 13. Ввиду подключения 1гавертиру1ощего входа дифференциального усилителя 18 к средней точке источника питания схемы за счет открытого ключевого транзистора 12 и наличия отрицательного напряжения U ( t ) на его неинвертирующем входе сигнал U (t ) усиливается с помощью дифференциального усилителя 18 в три раза и через резистор 19 вновь подается на выход устройства. В результате действия положительной обратной связи выходной сигнал U ( t ) удерживается в отрицательном состоянии и . Суммарная омкость обоих варикапов 6 и 7 в это время максимальна, т.е. С (U ) .при и ( t ) r-U-, (фиг.2). При переходе входного непрерывного сигнала 2 ( t ) в положительную область от нулевого порога начинает выполняться условие Z (t ) О K(l(t. )О. При этом закрывается ключевой транзистор 12 и открывается другой ключевой транзистор 13. Коэффициент передачи дифференциального усилителя в этом режиме работы из-за отрицательного значения выходного напряжения (J ( i ) и )1х на полезный сигнал, когда он находится ниже нулевого порога. В результате этого достигается высокая точ ность определе1шя моментов пересечения непрерывным полезным сигналом нулевог порога при переходе из отрицательной в положительную область. в модмент превышения выходным-сигналом и ( -fc ) нулевого порога оба сигнала Z(t) HU(t) оказываются по одну сторону (в полонштельной области) от этого порога, т.е. Z (t ) 7 О и и (t ) О. Смена полярности выходного сигнала U { i- ) с отрицательной на положительную и открытое в это время состояние ключевого транзистора 13 под действием входного положительного сигнала Z ( t ) способствует возрастанию коэффициента усиления дифференциаль ного усилителя 18 до значения, равного . Вследствие этого образуется положительная обратная связь через резистор 19, под действием которой вероятностное реле быстро переходит в положительное состояние и ( t ) U . Одновременно происходит увеличение значения парамет ра ft { и ) интегрирующей С-цепи (по кривой фиг.2) из-за увеличения ре( и ) варик зультирующей емкости С пов 6,7, со значения при U(t )до значения при U (t )-{, на котором затем и происходит стабилизация . выходного сигнала U (t ) за счет открытия варикапа 7 в прямом направлеПереход вероятностного реле в противоположное (отрицательное) состояние начинается в том случае, когда входной сигнал Z ( t ) вновь оказывается ниже уровня нулевого порога, т.е. начинает выполняться условие 2 (t ) 4 О п и ( i. ) О. В этом случае закрывается ключевой транзиоттор 13 и открывается другой ключевой транзистор 12. Коэффициент передачи дифференциального усилителя 18 из-за положительности выходного сигнала и ( Ь ) и закрытого от этого напряжения диода 16 становится равным единице, что приводит к отключению положительной обратной связи в этом режиме работы. Значение емкости С (U ) интегрирующей R С-цепи вновь умёньщается (по кривой на фиг. 2) от максимального Cfvvgj npH U (t )и до минимального мнн - значений, способствуя тем эффективному подавлению выбросов помех., наложенных ны полезный сигнал, когда он находится выше нулевого порога. В результате этого достигается высокая точность определения моменэхэв пересечения нулевого уровня непрерывным сигналом при его переходе из отрицательной области в положительную. В момент снижения выходного сигнала и (t) за нулевой уровень оба сигнала (t) ии( t ) оказываются по одну сторону (в отрицательной области) от нулевого порога, т.е. 7, ( i ) i.Q и ) (t) О. В этом режиме открытия диода 16 под действием отрицательного выходного сигнала U ( t ) и открытого ключевого транзистора 12 оТ отрицательного входного сигнала i ( i; ) коэффициент усиления дифференциального усилителя 18 вновь увеличивается до К-3. В результате этого образуется положительная обратная связь, под действием которой вероятностное реле быстро переходит в отрицательное состояние и ( t ) - - и. Одновременно происходит увеличение емкости С ( и ) с минимального при и (t ) -О до максимального при и (t ) - и значений с последующей стабилиза1щей выходного сигнала и ( t ) на уровне - из-за открытия варикапа 7 в прямом направлении. Вероятностное реле на варикапах (фиг.4) работает следующим образом. В исходном состоянии при наличш на входе устройства отрицательного сигнала 2i (i) выходное напряжение U ( t ) отрицательно и равно U ( t ) - - U-,, где U - запирающее (опорное) напряжение на варикапе 25. Транзисторы 31, 32, 41, 42, 43 и диод 55 открыты, а диод 54 закрыт. Выходной сигнал U(t), усиленный в три ре(за усилителем на транзисторах 42, 43 через резистор 52, вновь подается на вход устройства. В результате действия этой положительной обратной связи выходной сигнал U( t ) удерживается в отрицательном состоянии - U-1 При этом емкость С ( U ) максимальна. (фиг. 2). При переходе входного непрерывного сигнала 2. (t ) в положительную область закрываются транзисторы 21, 22 и открываются транзисторы 33, 34, что приводит к открытию диода 54 и закрытию диода 55. Под действием открытого диода 54 на эмиттер транзистора подается запирающее напряжение, которое отключает положительную обратную связь.

образованную транзисторами 42, 43. При этом другая положительная обратная связь, образованная транзисторами 45 и 46 также отключена ввиду закрытых транзисторов 44, 45, 46 под действием отрицательного выходного напряжения и (i .) (хотя и открыт в это время диод 55 и снято запирающее напряжение с эмиттера транзистора 46). В результате отключения положительных обратных связей выходное напряжение U ( t ) также, как и в устройстве, приведенном на фиг. 3, сначала медленно изменяется изза большого значения емкости С { U ) фильтра вблизи напряжения -

(фиг. 2), а затем, по мере, приближения выходного напряжения .к нулю, увеличивае свою скорость изменения. Нелинейный характер .изменения емкости С ( и ) интегрирующей 1 С-цепи способствует подавлению выбросов помех, наложенных на полезный сигнал отрицательной пол5фности.

При превышении выходным сигналом и (t ) нулевого порога оба сигнала

(t)HU(t) оказываются по одну сторону от этого порога. Под действием положительной пол51рности выходного сигнала и (t ) открываются транзисторы 44, 45, 46 и ввиду отсутствия в это

время запирающехх) напряжения на эмиттере транзистора 46 из-за закрытого диода 55 под действием открытого транзистора 34 образуется положительне1Я обратная связь, которая через резистор 53 переводит вероятностное реле в положительное состояние и ( t ) - Ui

Одновременно происходит увеличение емкости С ( и ) (по кривой на фиг.2) с С,„н при U (t ) О до С акспри и (t ) 1. Стабилизац1ш выходного напряжения U ( t ) на уровне Ц осуществляется за счет открытия варикапа 6 в прямом направлении.

Переход вероятностного реле в отрицательное состояние U( t ) начинается в случае, когда входной сигнал Z { t ) оказывается вновь ниже нулевого порога В этом случае закрываются транзисторы 33, 34 и открывается диод 55, через Который к эмиттеру транзистора 46 прикладывается запирающее напряжение отрицательной полярности, отключающее положительную обратную связь иа транзисторах 44, 45, 46. Одновременно открываются транзисторы 31, 32 и закрывается диод 54, под действием которого снимается запирающее напряжение положительной пол$фности с эмиттера транзистора 43. Однако положительная обратная связь, образованная транзисторами 41, 42,43 в этом режиме отключается из-за положительного значения выходного сигнала U (t ), которое удерживает в закрытом состоянии транзисторы 41, 42 с прямой проводимостью. В этом режиме значение емкости С { U ) интегрирующей 13 С-цепи вновь уменьшается (по на фиг. 2) с максимального (,до минимального С мин значений, способствуя тем самым эффективному подавлению выбросов помех, наложенных на сигнал положительной полярности.

При снижении выходного сигнала U(t) за уровень нулевого порога открываются транзисторы 41, 42, 43. Одновременно, из-за отсутствия запирающего напряжения на эмиттере транзистора 43 при 2 ()О образуется положительная обратная связь, которая быстро переводит вероятностное рел

в прютивоположное состояние U (-t U. При этом емкость С (U) увеличивается с минимального C до максимального -MOitc значения с последующей стабилизацией выходного сигнала U (t ) на уровне - Ц из-за открытия варикапа 25 в прямом направлении.

Формула изобретения

1.Вероятностное реле на варикапах, состоящее из нелинейной интегрирующей

Т С-цепи, образованной регистром и емкостью двух варикапов, включенных в диагонали двух мостовых схем, отличающееся тем, что, с целью повышения точности определения моментов пересечения нулевого порога искаженным помехой непрерывным разнополярным сигналом произвольной формы, в него введена схема пороговой положительной обратной связи, подключенная входом ко входу, а выходом к выходу нелинейной интегрирующей Т С-цепи.

2.Реле по п. 1, о г л и ч а ютц е е с я тем, что схема пороговой положительной обратной, связи выполнена на двух транзисторах разного типа проводимости, коллектор каждого из которых через последовательно соединенные резистор и диод подключены к инвертирующему входу дифференциального усилителя, а его выход через резистор подключен к неинвертируюшему входу того же дифференциального усилителя и ко х9.7 входу нелинейной интегрирующей R Сцепи. 3. Реле по п. 1,отличающе6 с я тем, что схетла пороговой положитель ной обратной связи вьтолнена на двух последовательно включенных ключевых каскадах на транзисторах разного типа проводимости коллекторы которых через встречно включенные диоды подключены к эмиттерам транзисторов выходных усилителей, гфичем коллекторы транзисторов выходных усилителей через резисторы подключены ко входу нелнней4.10 ной интегрирующей Ц С-цепи, а базы транзисторов выходных усилителей через эмиттернЫй повторитель подключены к выходу нелинейной интегрируют ей RCцепи. Источники информации, прик5ггые во внимание при экспертизе 1. Авторское свидетельство СССР №6О5317.кл.НОЗК 17/6О,09.ОЗ:76. 2.ТГвторское свидетельство СССН NO 4ОЗО38 Н ОЗ К 5/О8, 7.12.7О (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Помехоустойчивый триггер | 1988 |

|

SU1688402A1 |

| Двухпозиционное вероятностное реле(ЕгО ВАРиАНТы) | 1979 |

|

SU830649A1 |

| Активное вероятростное реле | 1976 |

|

SU605317A1 |

| Активное вероятностное реле | 1977 |

|

SU657632A2 |

| Активное вероятностное реле | 1978 |

|

SU675602A2 |

| Следящий аналого-цифровой преобразователь | 1983 |

|

SU1181116A1 |

| Реле времени | 1975 |

|

SU657476A1 |

| Помехозащищенное устройство для измерения амплитуды импульсных сигналов | 1977 |

|

SU690399A1 |

| Устройство для оценки параметров сигналов и условиях действия помех | 1979 |

|

SU866741A1 |

| Аналого-цифровой интегратор | 1977 |

|

SU732905A1 |

Фи.г.-/

Авторы

Даты

1980-07-30—Публикация

1978-07-17—Подача