1

Изобретение относится к импульсной теяНике.

Известен счетчик с исправлением ложных срабатываний, содержащий счетные ячейки, в котором с помощью схем совпадения на входе ячейки анализируют состояние всех предыдущих ячеек счетчика, задерживают сигнал с выхода триггера при его ложном срабатывании, происщедшем до установки всех предыдущих ячеек в единичные состояния и подают сигнал по цепи обратной связи на вход триггера для возвращения его в исходное состояние. Для предотвращения повторного срабатывания цепь обратной связи временно размыкают (I).

В данном счетчике не могут быть исправлены сбои, происходящие в такте-, когда сигналы со схем совпадения запирают цепи обратной связи.

Наиболее близким по технической сущности к предлагаемому является счетчик, содержащий формирователь импульсов, два выхода которого соединены с входами двух регистров на N триггерах, а третий выход - с одним из входов входного логического элемента И, второй вход которого связан с выходом логического элемента ИЛИ, причем установочные входь1. триггеров, кроме первого, первого регистра

соединеиы с нулевыми выходами триггеров второго регистра, установочный вход первого триггера второго регистра соединен с прямым выходом первого триггера первого регистра, и логические элементы И 2).

Недостатком данного счетчика является отсутствие коррекции кода, искаженного в результате сбоя.

Целью изобретения является введение коррекции кода, искаженного в результате сбоев. Поставленная цель достигается тем, что в двоичный счетчик, содержащий формирователь импульсов, два выхода которого соединены с входами двух регистров на N триггерах, а гретий выход - с одним из входов входного ло 5 гического элемента И, второй вход которого связан с выходом логического элемента ИЛИ, причем установочные входы триггеров, кроме первого, первого регистра соединены с нулевыми выходами триггеров второго регистра, установочный вход первого триггера второго регистра соединен с прямым выходом первого триггера первого регистра и логические элементы И, введены N-1 блоков коммутации и N полусумматоров, причем блоки коммутации включены между выходами логических ; лемеитов И и соответствующими выходами триггеров, кроме первого, первого регистра и входами соответствующих триггеров второго регистра, входы полусумматоров соединеиы с выходами соответствующих триггеров первого и второго регистров, а выходы полусумматоров соединены со входами упомянутого логического элемента ИЛИ.

Причем блок коммутации содержит два логических элемента И, логический элемент ИЛИ и инвертор.

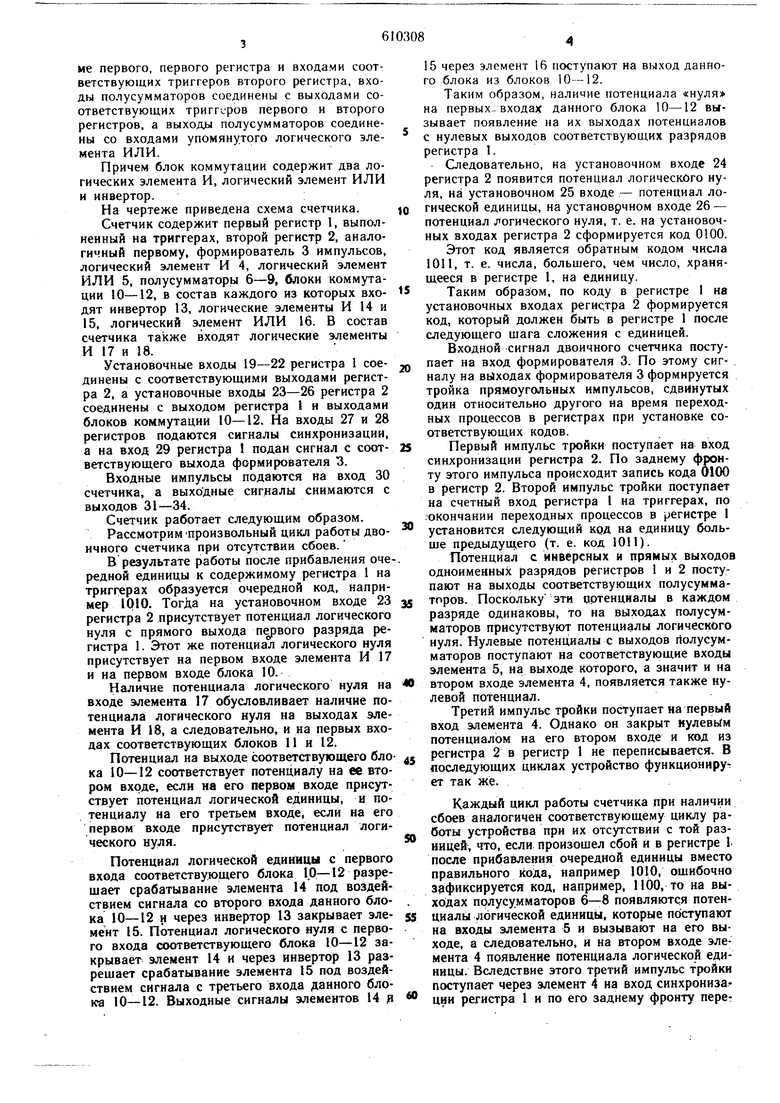

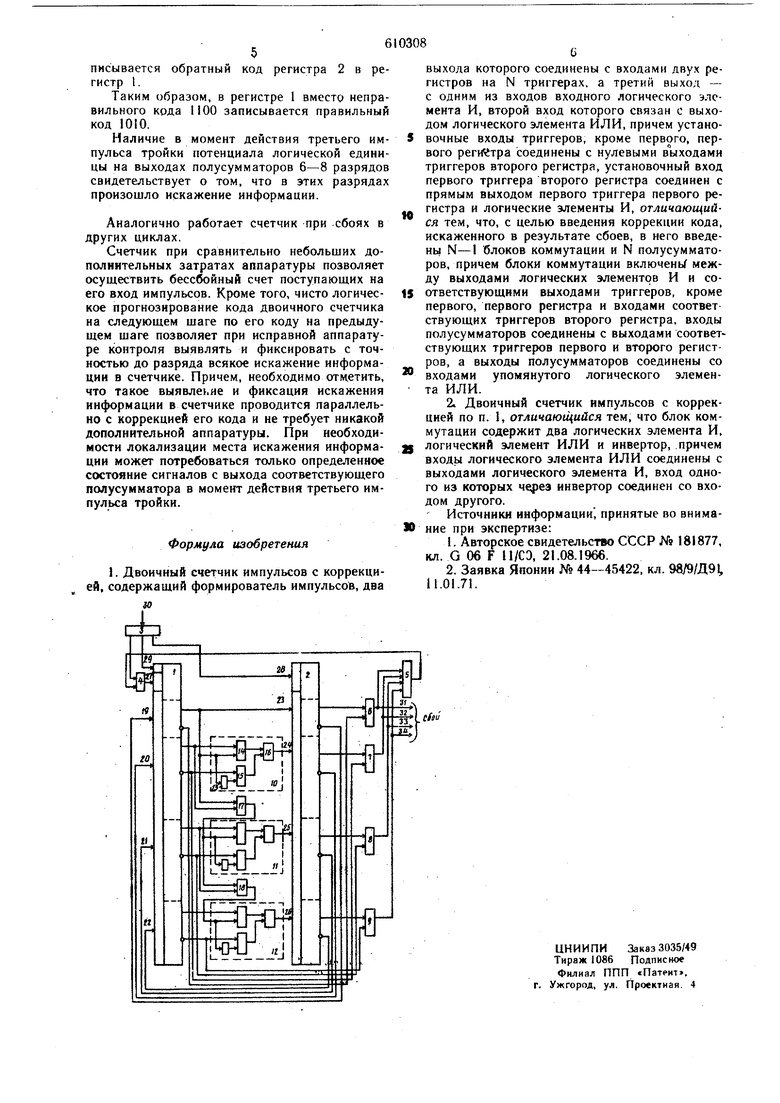

На чертеже приведена схема счетчика.

Счетчик содержит первый регистр 1, выполненный на триггерах, второй регистр 2, аналогичный первому, формирователь 3 импульсов, логический элемент И 4, логический элемент ИЛИ 5, полусумматоры 6-9, блоки коммутации 10-12, в состав каждого из которых входят инвертор 13, логические элементы И 14 и 15, логический элемент ИЛИ 16. В состав счетчика также входят логические элементы И 17 и 18.

Установочные входы 19-22 регистра 1 соединены с соответствующими выходами регистра 2, а установочные входы 23-26 регистра 2 соединены с выходом регистра 1 и выходами блоков коммутации 10-12. На входы 27 и 28 регистров подаются сигналы синхронизации, а на вход 29 регистра 1 подан сигнал с соответствующего выхода формирователя 3.

Входные импульсы подаются на вход 30 счетчика, а выходные сигналы снимаются с выходов .

Счетчик работает следующим образом.

РассмотримПроизвольный цикл работы двоичного счетчика при отсутствии сбоев.

В результате работы после прибавления оче редной единицы к содержимому регистра 1 на триггерах образуется очередной код, например 1010. Тогда на установочном входе 23 регистра 2 присутствует потенциал логического нуля с прямого выхода первого разряда регистра 1. Этот же потенциал логического нуля присутствует на первом входе элемента И 17 и на первом входе блока 10.

Наличие потенциала логического нуля на входе элемента 17 обусловливает наличие потенциала логического нуля на выходах элемента И 18, а следовательно, и на первых входах соответствующих блоков 11 и 12.

Потенциал на выходе соответствующего блока 10-12 соответствует потенциалу на ее втором входе, если на его первом входе присутствует потенциал логической едииицы, и потенциалу на его третьем входе, если на его первом входе присутствует потенциал логического нуля.

Потенциал логической единицы с первого входа соответствующего блока 10-12 разрешает срабатывание элемента 14 под воздействием сигнала со второго входа данного блока 10-12 и через инвертор 13 закрывает элемент 15. Потенциал логического нуля с первого входа соответствующего блока 10-12 закрывает элемент 14 и через инвертор 13 разрешает срабатывание элемента 15 под воздействием сигнала с третьего входа данного блока 10-12. Выходные сигналы элементов 14 р

15 через элемент 16 поступают на выход данного блока из блоков 10-12.

Таким образом, наличие потенциала «нуля на первых-входах данного блока 10-12 вызывает появление на их выходах потенциалов с нулевых выходов соответствующих разрядов регистра 1.

Следовательно, на установочном входе 24 регистра 2 появится потенциал логического нуля, на установочном 25 входе - потенциал логической единицы, на установрчном входе 26 - потенциал логического нуля, т. е. на установочных входах регистра 2 сформируется код 0100.

Этот код является обратным кодом числа 1011, т. е. числа, большего, чем число, хранящееся в регистре 1, на единицу.

Таким образом, по коду в регистре 1 на установочных входах регистра 2 формируется код, который должен быть в регистре 1 после следующего шага сложения с единицей.

Входной сигнал двоичного счетчика поступает на вход формирователя 3. По этому сигналу на вь ходах формирователя 3 формируется тройка прямоугольных импульсов, сдвинутых один относительно другого на время переходных процессов в регистрах при установке соответствующих кодов.

Первый импульс тройки поступает на вход синхронизации регистра 2. По заднему фроиту этого импульса происходит запись кода 0100 в регистр 2. Второй импульс тройки поступает на счетный вход регистра 1 на триггерах, по окончании переходных процессов в (егистре 1 установится следующий крд на единицу больше предыдущего (т. е. код 1011).

Потенциал с инверсных и прямых выходов одноименных разрядов регистров 1 и 2 поступают на выходы соответствующих полусумматоров. Поскольку эти иотенциалы в каждом разряде одинаковы, то на выходах полусумматоров присутствуют потенциалы логического нуля. Нулевые потенциалы с выходов полусумматоров поступают на соответствующие входы элемента 5, на выходе которого, а значит и на втором входе элемента 4, появляется также нулевой потенциал.

Третий импульс тройки поступает на первый вход элемента 4. Однако он закрыт кулевым потенциалом на его втором входе и код из регистра 2 в регистр 1 не переписывается. В последующих циклах устройство функционирую ет так же.

Каждый цикл работы счетчика при наличии сбоев аналогичен соответствующему циклу работы устройства при их отсутствии с той разницей, что, если произошел сбой и в регистре 1 после прибавления очередной единицы вместо правильного кода, например 1010, ошибочно зафиксируется код, например, 1100, то на выходах полусумматоров 6--8 появляются потенциалы логической единицы, которые поступают на входы элемента 5 и вызывают на его выходе, а следовательно, и на втором входе элемента 4 появление потенциала логической единицы. Вследствие этого третий импульс тройки поступает через элемент 4 на вход синхронизации регистра 1 и по его заднему фронту пере

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор последовательности импульсов | 1988 |

|

SU1539972A1 |

| Устройство для ввода информации (его варианты) | 1985 |

|

SU1290286A1 |

| Пересчетное устройство с контролем | 1977 |

|

SU674220A1 |

| Устройство для сортировки информации | 1985 |

|

SU1278834A1 |

| Шифратор | 1985 |

|

SU1298802A2 |

| Устройство для ввода информации | 1984 |

|

SU1200274A2 |

| Устройство для счета импульсов | 1979 |

|

SU797078A1 |

| Устройство ввода поправок в хранитель времени | 1984 |

|

SU1173382A2 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Арифметическое устройство | 1977 |

|

SU734680A1 |

Авторы

Даты

1978-06-05—Публикация

1976-04-05—Подача