Изобретение относится к автоматике и вычислительной технике и может быть использовано в специализированных цифровых устройствах для обработки данных.

Цель изобретения - увеличение достоверности работы.

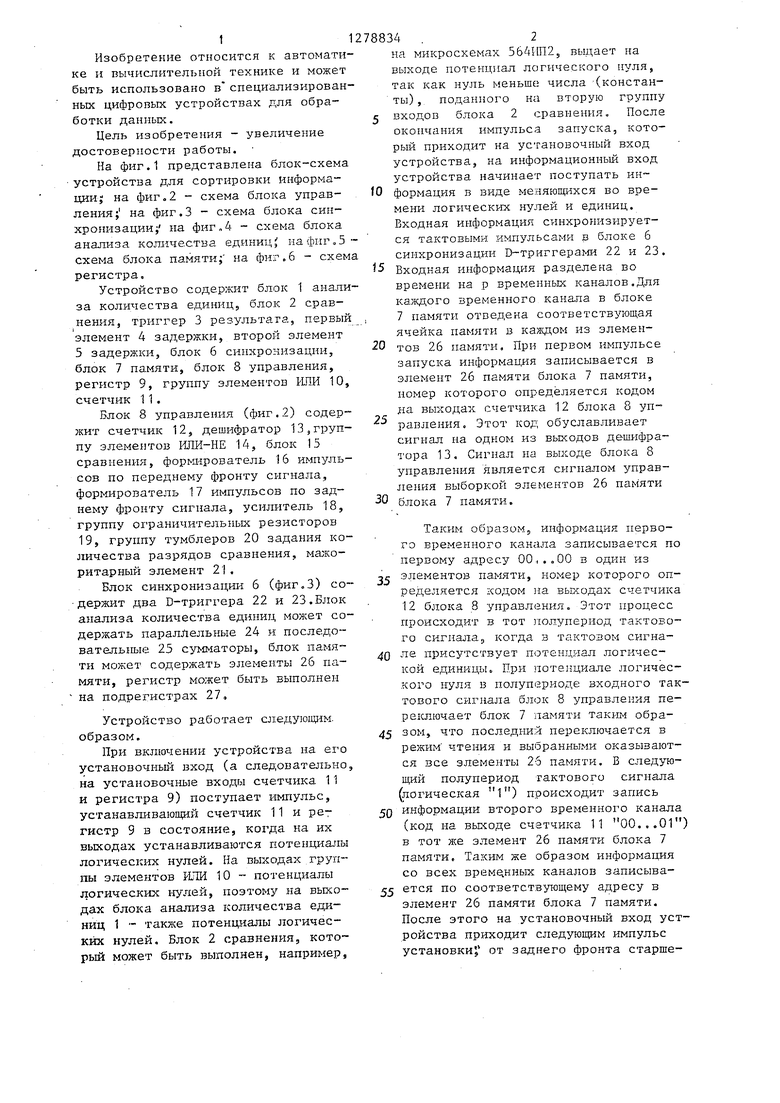

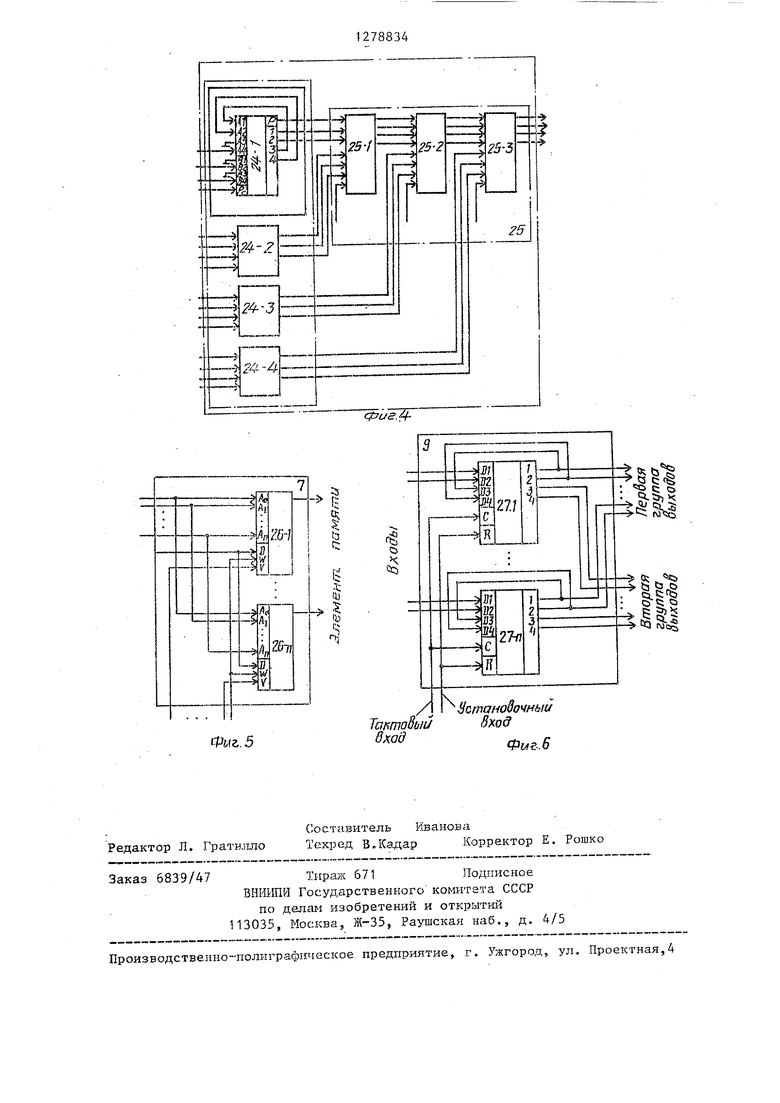

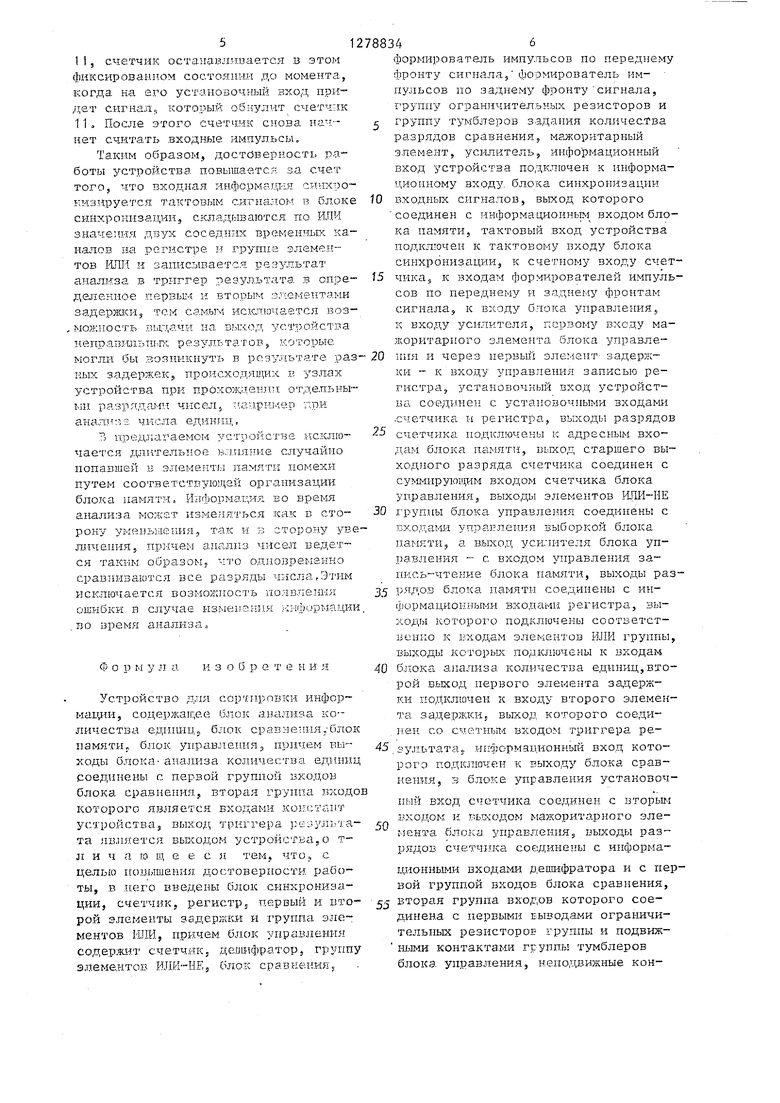

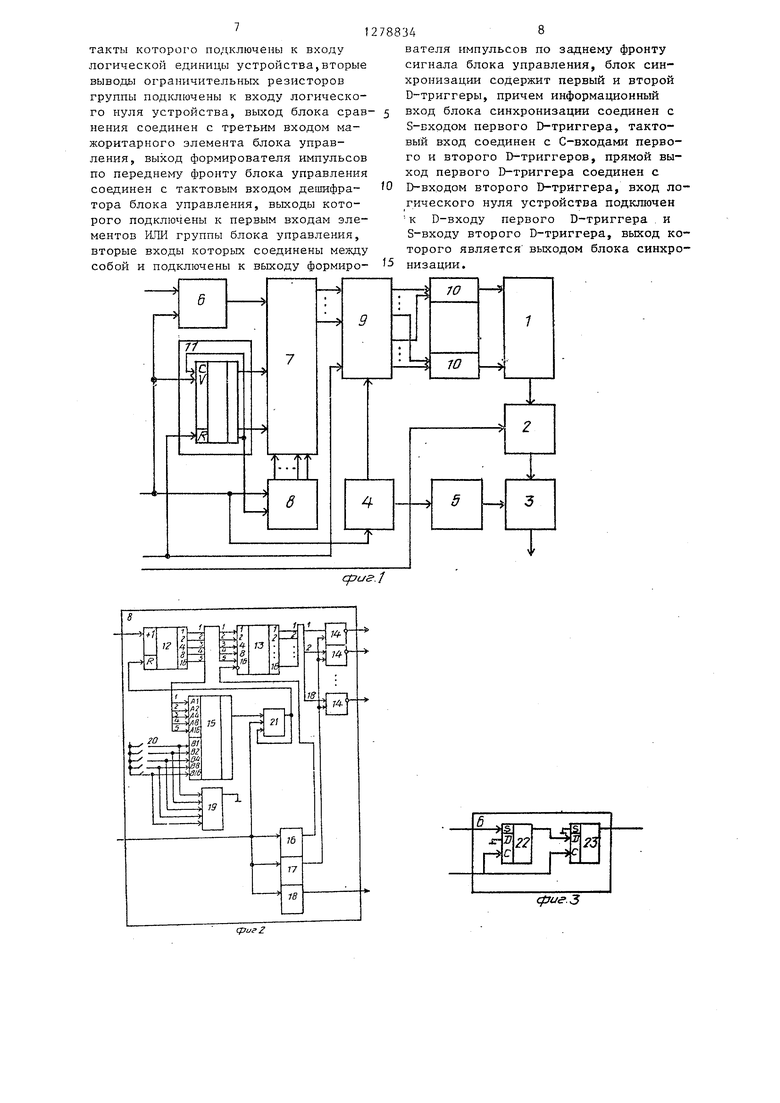

На фиг.1 представлена блок-схема

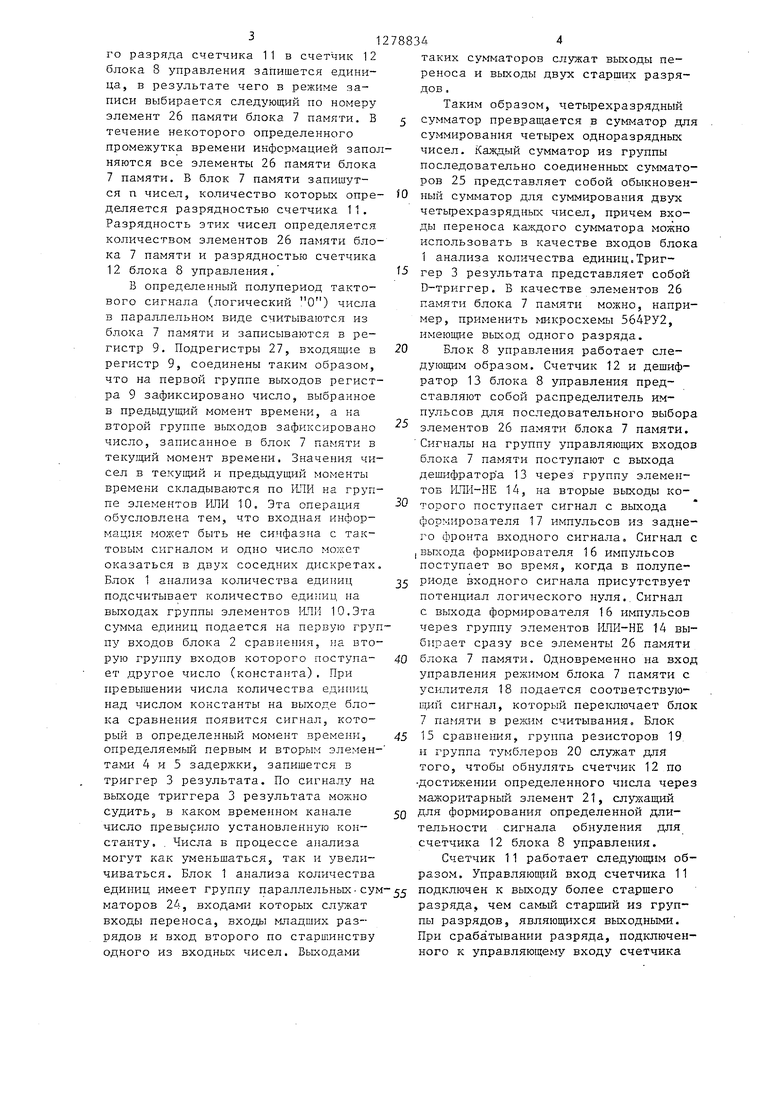

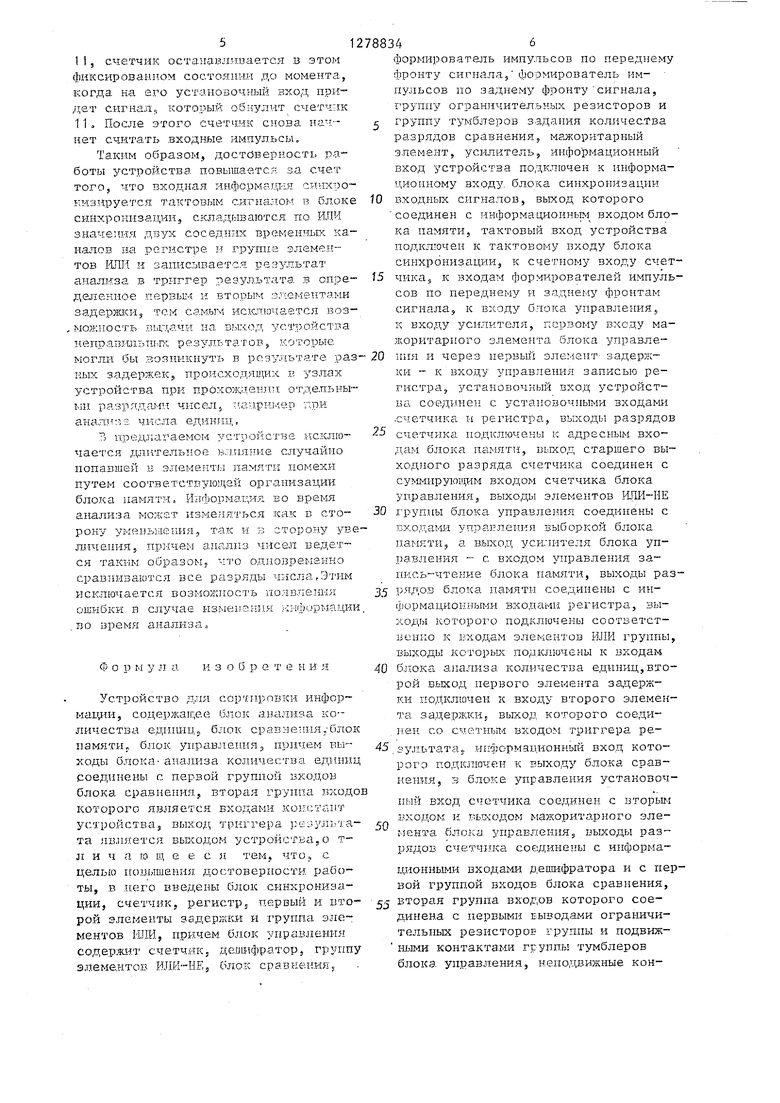

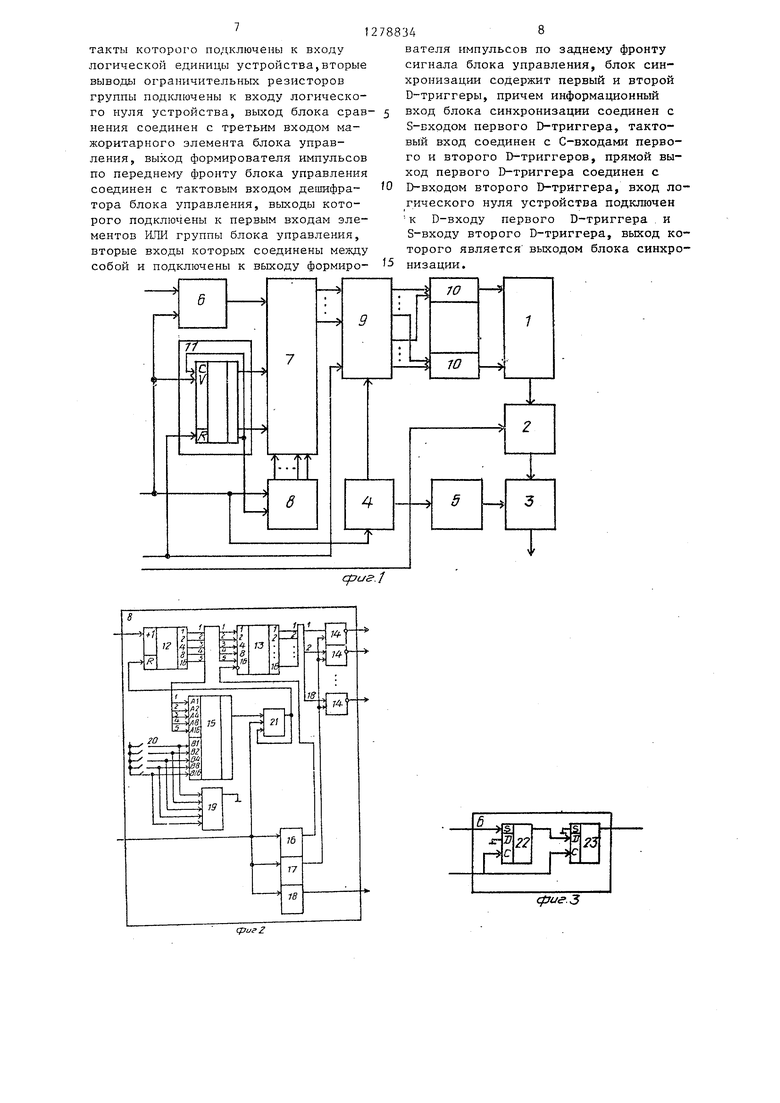

устройства для сортировки информации; на фиг о 2 - схема блока управления; на фиг.З - схема блока синхронизации; па фиг„4 - схема блока анализа количества единицJ на фиг.З схема блока памяти; на фиг.6 - схем регистра.

Устройство содержит блок 1 анализа количества единиц, блок 2 сравнения, триггер 3 результата, первый элемент 4 задержки, второй элемент 5 задержки, блок б синхронизации, блок 7 памяти, блок 8 управления, регистр 9, группу элементов РШИ 10, счетчик 11,

Блок 8 управления (фиг.2) содержит счетчик 12, дешифратор 13,группу элементов ИЛИ-НЕ 14, блок 15 сравнения, формирователь 16 импульсов по переднему фронту сигнала, формирователь 17 импульсов по заднему фронту сигнала, усилитель 18, группу ограничительных резисторов 19, группу тумблеров 20 задания количества разрядов сравнения, мажоритарный элемент 21.

Блок синхронизации б (фиг.З) содержит два D-триггера 22 и 23.Блок анализа количества единиц может содержать параллельные 24 и последовательные 25 сумматоры, блок памяти может содержать эле1 1енты 26 памяти, регистр может быть выполнен на подрегистрах 27,

Устройство работает следующим. образом.

При включении устройства на его установочньш: вход (а следовательно, на установочные входг:. счетчика 11 и регистра 9) поступает импульс, устанавливающий счетчик 11 и регистр 9 в состояние, когца на их выходах устанавливаются потенциалы логических нулей. На выходах группы элементов ИЛИ 10 - потенциалы логических иу.гшй, поэтому на выходах блока анализа количества единиц 1 - также потенциалы логических нулей. Блок 2 сравнения, который может быть выполнен, например.

на микросхемах Sb IfflZ, выдает на выходе потенциал логического нуля, так как нуль меньше числа (константы) , поданного на вторую группу

входов блока 2 сравнения. После окончания импульса запуска, который приходит на установочный вход устройства, на информационный вход устройства начинает поступать ин

формация в виде меняющихся во времени логических нулей и единиц. Входная информация синхронизируется тактовыми импульсами в блоке б синхронизации В триггерами 22 и 23.

Входная информац ш разделена во времени на р временных каналов.Для каждого временного канала в блоке 7 памяти отведена соответствующая ячейка памяти в каждом из злементов 26 памяти. При первом импульсе запуска информация записывается в элемент 26 памяти блока 7 памяти, номер которого определяется кодом да выходах счетчика 12 блока 8 уп

равления, Этот код обуславливает сигнал на одном из выходов дешифратора 13, Сигнал на выходе блока 8 управления является сигпалом управления выборкой элементов 26 памяти блока 7 памяти.

Таким обрггзом, информация первого временного канала записывается по первому адресу 00,.,00 в один из

элементов памяти, номер которого определяется иа выходах счетчика 12 блока В управления. Этот процесс происходит в тот полупериод тактового сигнала, когда в тактовом сигнале присутствует потенциал логической единицы. При потенциале логического нуля в полупериоде входного тактового сигнала блок 8 управления переключает блок 7 памяти таким образом, что последний переключается в режим чтения и выбранными оказываются все элементы 26 памяти. В следующий полупериод тактового сигнала (логическая 1) происходит запись

информации второго временного канала (код па выходе счетчика 11 00...01) в тот же элемент 26 памяти блока 7 памяти. Таким же образом информация со всех врем(нных каналов записывается по соответствующему адресу в элемент 26 памяти блока 7 памяти. После этого на установочный вход устройства приходит следующим импульс установкиJ от заднего фронта старшего разряда счетчика 11 в счетчик 12 блока 8 управления запишется единица, в результате чего в режиме записи выбирается следующий по номеру элемент 26 памяти блока 7 памяти. В течение некоторого определенного промежутка времени информацией заполняются все элементы 26 памяти блока 7 памяти. В блок 7 памяти запишутся п чисел, количество которых определяется разрядностью счетчика 11. Разрядность этих чисел определяется количеством элементов 26 памяти блока 7 памяти и разрядностью счетчика 12 блока 8 управления.

В определенный полупериод тактового сигнала (логический О) числа в параллельном виде считываются из блока 7 памяти и записываются в регистр 9, Подрегистры 27, входящие в регистр 9, соединены таким образом, что на первой группе выходов регистра 9 зафиксировано число, выбранное в предыдущий момент времени, а на второй группе выходов зафиксировано число, записанное в блок 7 памяти в текущий момент времени. Значения чисел в текуцщй и предьщущий моменты времени складываются по 1ШИ на группе элементов ИЛИ 10. Эта операция обусловлена тем, что входная информация может быть не синфазна с тактовым сигналом и одно число может оказаться в двух соседних дискретах Блок 1 анализа количества единиц подсчитывает количество едиггиц на выходах группы элементов ПИ 10,Эта сумма единиц подается на первую rpi n пу входов блока 2 сравнения, на вторую группу входов которого поступает другое число (константа). При превышении числа количества единиц над числом константы на выходе блока сравнения появится сигнал, который в определенный момент времени, определяемый первым и вторым элементами 4 и 5 задержки, запишется в триггер 3 результата. По сигналу на выходе триггера 3 результата можно судитьJ в каком временном канале число превысило установленную константу. , Числа в процессе анализа могут как уменьшаться, так и увеличиваться. Блок 1 анализа количества

единиц имеет группу параллельных-сум-55 подключен к выходу более старшего маторов 24, входами которых служат разряда, чем самый старший из груп входы переноса, входы младших разрядов и вход второго по старшинству одного из входных чисел. Выходами

пы разрядов, являющихся выходными. При срабатывании разряда, подключе ного к управляющему входу счетчика

таких сумматоров служат выходы переноса и выходы двух старших разрядов.

Таким образом, четырехразрядный

сумматор превращается в сумматор для суммирования четырех одноразрядных чисел. Каждый сумматор из группы последовательно соединенных сумматоров 25 представляет собой обыкновен0 ный сумматор для суммирования двух четырехразрядных чисел, причем входы переноса каждого сумматора можно использовать в качестве входов блока 1 анализа количества единиц.Триг5 гер 3 результата представляет собой D-триггер. В качестве элементов 26 памяти блока 7 памяти можно, например, применить микросхемы 564РУ2, имеющие выход одного разряда.

0 Блок 8 управления работает следующим образом. Счетчик 12 и дешифратор 13 блока 8 управления представляют собой распределитель импульсов для последовательного выбора

5 элементов 26 памяти блока 7 памяти. Сигналы на группу управляющих входов блока 7 памяти поступают с выхода дешифратор а 13 через группу элементов РШИ-НЕ 14, на вторые выходы которого поступает сигнал с выхода формирователя 17 импульсов из заднего фронта входного сигнала. Сигнал с Iвькода формирователя 16 импульсов поступает во время, когда в полупе5 риоде входного сигнала присутствует потенциал логического нуля,.Сигнал с выхода формирователя 16 импульсов через группу элементов 1 ШИ-НЕ 14 выбирает сразу все элементы 26 памяти

0 блока 7 памяти. Одновременно на вход управления режимом блока 7 памяти с усилителя 18 подается соответствующий сигнал, который переключает блок 7 памяти в режим считывания. Блок

5 15 сравне1шя, группа резисторов 19. и группа тумблеров 20 служат для того, чтобы обнулять счетчик 12 по достижении определенного числа через мажоритарный элемент 21, служащий

0 для формирования определенной длительности сигнала обнуления для счетчика 12 блока 8 управления.

Счетчик 11 работает следующим образом. Управляюпщй вход счетчика 11

0

подключен к выходу более старшего разряда, чем самый старший из груп

пы разрядов, являющихся выходными. При срабатывании разряда, подключенного к управляющему входу счетчика

I I, счетчик останавлипается в этом фиксирован1 ом состоянии до момента, когда на его устаиовочный вход придет сигнаЛд который обнул /гг счетчик 11„ После этого счетчик снова начнет считать входные импульсы.

Таким образом, достоверность работы устройства повышается за счет того, что входная информацЕЯ синхронизируется тактовым сигнале)-. в блоке синхронизац.ии, складываются по ИЛИ значения двух соседних временных каналов на регистре и группе элементов 1ШИ и записывается результат анализа в триггер результата в определенное первы;.- и вторым з. - .емептами задеряжи, тем самым исклю- Ш-втся воз- мол-аюсть зьг.гачи на ., устр Ойства неправгахьньп:; результггтов, которые

25

30

могли бы },озникнуть в результате раз- 20 ния и через первый элемент задерж- НЫ5С задержек, происходящих в узлах устройства при прОхож,цен1П1 отдельными разрядш-м чиселJ иаириГ ер при aiianj-nvs, числа единиц,

предлагаемом устройстве исключается дл гтель юе влияние случайно попавшей в элементь; памят.и помехи путем со отв е т с Т В ор г аниз адии блока памяти. Информация во время анализа может изме 1яться как в сторону уменгл 1ег1ия, так и в сторону увеличения, npiixie.M анализ чисел ведется таким образому что одновременно сравниваются все разряды числа,Этим исключается возможность появле нкя ошибки в случае изменения ;.;1-1фор -5ации, .во время анализа

Ф о р м у л а и зоб р е т е н и я

Устройство дл;1 сортировки информации, содержащее блок анализа ко-- личества едипид блок сравнения блок памяти,, блок управлен.ияз при-чем выходы блока- ана.п-1за количества еддп-пщ соединены с первой группой входов блока сравненияJ вторая группгг входов которого является входами констант устройства J выход триггера };езульта- та является выходом устройства,о т л и ч а .га щ е е с я тем, что, с целью повышения достовер1.ости работы, в .него введены блок синхронизаки к входу управления записью регистра, установочный вход устройства соединен с установочными входами .счетчика и регистра, выходы разрядо счетчика подключены к адресным входам блока памяти, выход старшего вы ходного разряда, счетчика соединен с суммируюнщм входом счетчика блока управления, выходы элементов ИЛИ-НЕ группы блока управления соединены с входами управления выборкой блока памяти,, а выход уси. 1ителя блока уп- рав, .ения - с входом управления за- Г1ксь чтен.р$е блока памяти, выходы ра

35 блока пам.ятн соединены с ин- (рормадионными входа м.и регистра, выходы которого подключены соответственно к вхо74ам элементов ИЛИ группы выходы которых подключены к входам

40 б.гиока а.)1ализа количества единид,вто рой выход .первого элемента задержки гю.дключен к входу второго элемен та задержки,, выход которого соединен со счетньга входом триггера ре45 зультата.; информационный вход которого подключен к выходу бло.ка сравнения, 3 б.локе управления установоч

50

Н.Ы.Й вход, счетчика соединен с вторьш входом и пькодом мажоритарного элемента блока управления, выходы разрядов счетчзпса соединены с информащ-юнными входами дешифратора и с пе вой группой входов блока сравнения.

ции, счетчик, регистр; первый и вто- 55 торая группа входов которого соерой элементы задерлсгси: и группа элементов ШШ, причем блок управления coAep-iRiJT счетчик, деццтфратор, rpi/.viny элеме.нто.в ИЛИ-НЕ, блок сравнен.ия5

формирователь импульсов по переднему фронту сигнала, формирователь им- пульсов по заднему фронту сигнала, групп у ограничительных резисторов и

группу тумблеров задания количества рэ.зрядов сравнения, мажоритарный элемент, усилитель, инфо рмационный вход устройства подключен к информационному входу, блока синхронизации

входных сигналов, выход которого

соединен с информационньм входом блока памяти, тактовый вход устройства подключен к тактовому входу блока сргнхронизадии, к счетному входу счетчика, к входам формирователей импульсов по переднему и заднему фронтам сигнала, к входу блока управления, к входу усилителя, первому входу ма- лсоритарного элемента блока управле

ния и через первый элемент задерж-

ки к входу управления записью регистра, установочный вход устройства соединен с установочными входами .счетчика и регистра, выходы разрядов счетчика подключены к адресным входам блока памяти, выход старшего выходного разряда, счетчика соединен с суммируюнщм входом счетчика блока управления, выходы элементов ИЛИ-НЕ группы блока управления соединены с входами управления выборкой блока памяти,, а выход уси. 1ителя блока уп- рав, .ения - с входом управления за- Г1ксь чтен.р$е блока памяти, выходы разР- ДОз блока пам.ятн соединены с ин- (рормадионными входа м.и регистра, выходы которого подключены соответственно к вхо74ам элементов ИЛИ группы, выходы которых подключены к входам

б.гиока а.)1ализа количества единид,второй выход .первого элемента задержки гю.дключен к входу второго элемента задержки,, выход которого соединен со счетньга входом триггера результата.; информационный вход которого подключен к выходу бло.ка сравнения, 3 б.локе управления установоч50

Н.Ы.Й вход, счетчика соединен с вторьш входом и пькодом мажоритарного элемента блока управления, выходы разрядов счетчзпса соединены с информащ-юнными входами дешифратора и с первой группой входов блока сравнения.

динена с первыми выводами ограничительных резнстороЕ группы и подвиж- 1ШМИ контакта.ми группы тумблеров блока, управления, неподвижные кон 1

такты которого подключены к входу логической единицы устройства,вторые выводы ограничительных резисторов группы подключены к входу логического нуля устройства, выход блока срав нения соединен с третьим входом мажоритарного элемента блока управления, выход формирователя импульсов по переднему фронту блока управления соединен с тактовым входом дешифратора блока управления, выходы которого подключены к первым входам элементов ИЛИ группы блока управления, вторые входы которых соединены между собой и подключены к выходу формиросриг.1

5

788348

вателя импульсов по заднему фронту сигнала блока управления, блок синхронизации содержит первый и второй D-триггеры, причем информационный вход блока синхронизации соединен с S-вхрдом первого D-триггера, тактовый вход соединен с С-входами первого и второго D-триггеров, прямой выход первого D-триггера соединен с D-входом второго D-триггера, вход логического нуля устройства подключен к D-входу первого D-триггера и S-входу второго D-триггера, выход которого является выходом блока синхронизации.

fO

15

(pueZ

cpi/е.З

t3

r-5

Фмг. 5

Редактор Л. FpaTHJUio

Составитель Иванова

Техред В.КздарКорректор Е. Рошко

6839/47

Тнршк 671Подписное

ВНШШИ Государственного комитета СССР

по дехиш изобретений и открытий 13035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная,4

4-

Ei

IP

-

&e

Ig1

Ci

§

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сортировки информации | 1986 |

|

SU1386989A2 |

| Многоканальное устройство для сбора и обработки информации | 1988 |

|

SU1524078A1 |

| Устройство формирования сигнала прерывания | 1983 |

|

SU1112365A1 |

| Устройство для индикации | 1989 |

|

SU1667150A1 |

| Трехканальное резервированное запоминающее устройство | 1984 |

|

SU1215133A1 |

| Устройство для контроля срабатывания клавиш наборного поля | 1985 |

|

SU1297050A1 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

| Распределенная система для программного управления с мажоритированием | 1990 |

|

SU1727112A1 |

| Устройство для сортировки двоичных чисел | 1982 |

|

SU1049900A1 |

| Трехканальная резервированная микропроцессорная система | 1985 |

|

SU1378287A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в специализированных: цифровых устройствах для обработки данных. Цель изобретения - увеличение достоверности работы. Устройство содержит блок анализа количества единиц,блок сравнения, триггер результата, два элемента задержки, блок синхронизации, блок памяти, блок управления,, ре гистр, группу элементов ШШ и счетчик. Входная информация в виде менягаищхся во времени логических единиц и нулей синхронизируется и делится во времени на р временных каналов. Для каждого временного канала в блоке памяти отведена соответствующая ячейка памяти. .В блок памяти записывается п чисел, разрядность которых определяется разрядностью счетчика. Числа в параллельном виде считываются из блока памяти в регистр. Значения чисел в текупц-1Й и предыдущий моменты времени складываются по ИЛИ и поступают на блок анализа количества единиц.Сумма единиц сравнивается с константой в блоке сравнения и результат записывает-- ся в пример результата, который отмечает, в каком временном канале число превысило установленную константу. 6 ил. с е

| Устройство для сортировки чисел | 1980 |

|

SU943707A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для сортировки и выборки информации | 1983 |

|

SU1087986A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-23—Публикация

1985-05-12—Подача