Изобретение относится к вычислительной технике, может применяться в автоматизированных системах управления, контроля и обработки информации и является усовершенствованием изобретения по авт. св. № 590825.

Цель изобретения - расширение функциональных возможностей шифратора, а именно преобразование в код состояния периодических импульсных последовательностей, как-то: наличие, отсутствие и сбои в виде пропадания единичного импульса из последовательности или появления лишнего импульса.

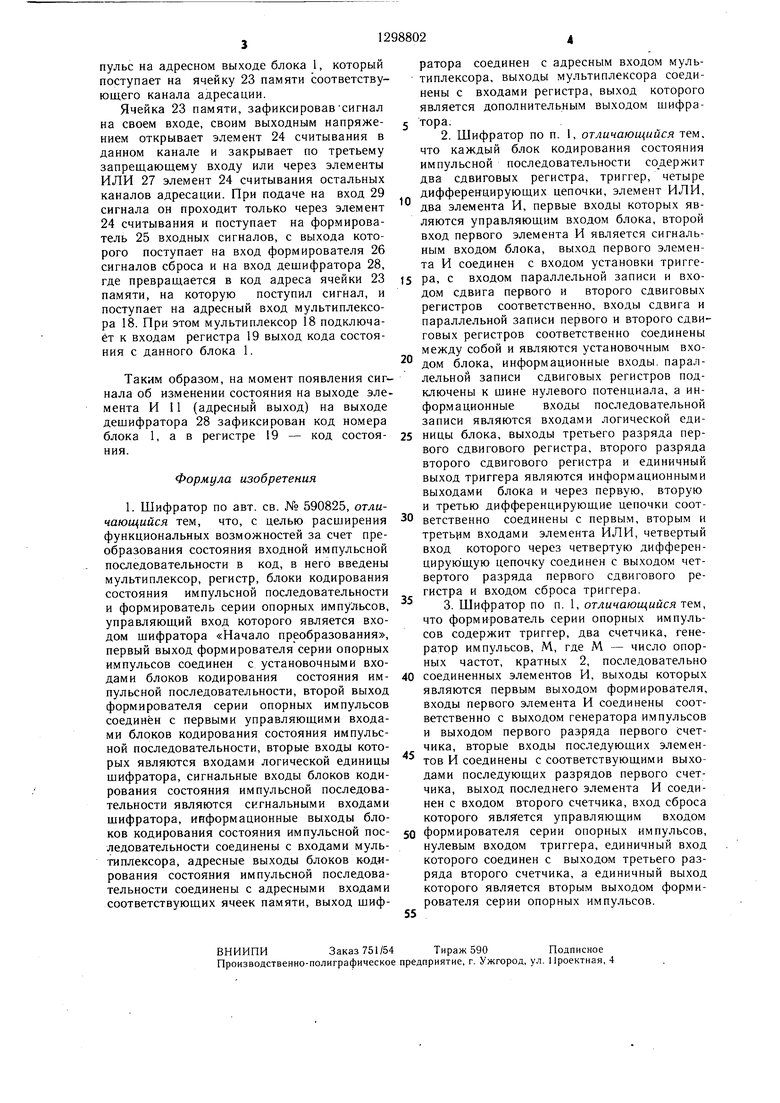

На чертеже представлена схема шифратора.

Шифратор содержит блоки Р, F, ..., 1 кодирования состояния импульсной последовательности по числу ячеек памяти, каждый из которых содержит сдвиговые регистры 2 и 3, дифференцируюшие цепочки 4-7, триггер 8, элемент ИЛИ 9, элементы И 10 и 11, сигнальную шину устройства И 12; формирователь серии опорных импульсов, состояший из генератора 13 импульсов, счетчика 14, элементов 15, 15, ... ..., 15, где М число серии опорных частот, кратных 2, второго счетчика 16 и триггера 17; мультиплексор 18; регистр 19; адресный блок 20, содержаШ.ИЙ N каналов 21, 22, ..., (где N - число ячеек памяти) адресации, причем каждый канал состоит из ячейки 23 памяти, элемента 24 считывания, формирователя 25 входных сигналов, формирователя 26 сигналов сброса, а все каналы, кроме первого, содержат элемент ИЛИ 27, дешифратор 28 и входную шину «Разрешение считывания 29 и входную шину «Начало преобразования 30.

Шифратор работает следующим образом

Формирователь серии опорных импульсов с помощью счетчика 14 и элементов 15 -15 и формирует на выходах последних из импульсной последовательности генератора 13 импульсов набор импульсных последовательностей, частоты Ьледования которых отличаются друг от друга в два раза. Таким образом обеспечивается возможность выбора опорной импульсной последовательности для блока 1, чтобы период следования сигнала (Т) на входных шинах устройства был больше периода следования опорной последовательности (То), но не более, чем в два раза, тогда в любом интервале времени, равном Т., при отсутствии сбоев могут появиться не более двух импульсов опорной последовательности. На этом соотношении основана работа блоков 1.

При поступлении на шину 30 сигнала «Начало преобразования счетчик 16 и триггер 17 устанавливаются в исходное состояние, после чего счетчик 16 начинает счет импульсов опорной последовательности

с максимальным используемым периодом следования.

После отсчета четвертого импульса сигнал с выхода счетчика 16 устанавливает триггер 17 в единичное состояние, на выходе его и, следовательно, на управляющих входах блока 1 появляется сигнал «Разрешение преобразования, разрешающий прохождение входного сигнала через элемент И 10 и сигнала изменения состояния через элемент И 11 блока 1. При прохождении четырех импульсов регистры 2 и 3 всех блоков 1 гарантированно устанавливаются в исходное состояние, соответствующее наличию сигнала на выходах третьего и четвертого разрядов .регистра 2, что обозначает отсутствие входного сигнала, и отсутствие сигналов с выходов регистра 3.

Поскольку входы последовательной записи регистров 2 и 3 подключены к положительному потенциалу, а входы параллельной записи - к нулевому, то каждый приходящий импульс опорной последовательности, поступающий на установочный вход в регистре 3 записывает все нули, в регистре 2 записывает и сдвигает единицу в последующий разряд, а каждый импульс сигнальной последовательности в регистре 2 записывает все нули, в регистре 3 записывает и сдвигает единицу. Таким образом, если в сигнальной последовательности отсутствуют сбои, на задействованных выходах регистров 2 и 3 сигналы отсутствуют. Прохождение подряд трех опорных импульсов обозначает, что пропал импульс в сигнальной последовательности, при этом единица в регистре 2 сдвигается до третьего разряда, следующий опорный импульс вызывает появление сигнала и на четвертом разряде, что идентифицируется как снятие сигнальной последовательности, так как сбой в виде пропадания двух имлульсов подряд маловероятен.

Прохождение подряд двух сигнальных импульсов вызывает появление сигнала на выходе второго разряда регистра 3 и идентифицируется как сбой в сигнальной последовательности в виде появления лишнего импульса так как в контрольно-поверочной аппаратуре могут быть использованы известные способы обеспечения малой вероятности сбоев.

Сигнал о наличии сигнальной последовательности формируется на выходе триггера 8, который взводится первым сигнальным импульсом с выхода элемента И 10 и сбрасывается сигналом с четвертого разряда регистра 2.

В момент появления соответствующего сигнала о состоянии на выходах регистров 2 и 3 и триггера 8, а следовательно, на выходах кода состояния блока с помощью дифференцирующих цепочек 4-7, элемента ИЛИ 9 и элемента И 11 формируется импульс на адресном выходе блока 1, который поступает на ячейку 23 памяти соответствующего канала адресации.

Ячейка 23 памяти, зафиксировав сигнал на своем входе, своим выходным напряжением открывает элемент 24 считывания в данном канале и закрывает по третьему запрещающему входу или через элементы ИЛИ 27 элемент 24 считывания остальных каналов адресации. При подаче на вход 29 сигнала он проходит только через элемент 24 считывания и поступает на формирователь 25 входных сигналов, с выхода которого поступает на вход формирователя 26 сигналов сброса и на вход дешифратора 28, где превращается в код адреса ячейки 23 памяти, на которую поступил сигнал, и поступает на адресный вход мультиплексора 18. При этом мультиплексор 18 подключает к входам регистра 19 выход кода состояния с данного блока 1.

Таким образом, на момент появления сигнала об изменении состояния на выходе элемента И 11 (адресный выход) на выходе дешифратора 28 зафиксирован код номера блока 1, а в регистре 19 - код состояния.

Формула изобретения

1. Шифратор по авт. св. № 590825, отличающийся тем, что, с целью расширения функциональных возможностей за счет преобразования состояния входной импульсной последовательности в код, в него введены мультиплексор, регистр, блоки кодирования состояния импульсной последовательности и формирователь серии опорных импульсов, управляющий вход которого является входом шифратора «Начало преобразования, первый выход формирователя серии опорных импульсов соединен с установочными входами блоков кодирования состояния импульсной последовательности, второй выход формирователя серии опорных импульсов соединён с первыми управляющими входами блоков кодирования состояния импульсной последовательности, вторые входы которых являются входами логической единицы шифратора, сигнальные входы блоков кодирования состояния импульсной последовательности являются сигнальными входами шифратора, информационные выходы блоков кодирования состояния импульсной последовательности соединены с входами мультиплексора, адресные выходы блоков кодирования состояния импульсной последовательности соединены с адресными входами соответствующих ячеек памяти, выход шифВНИИПИЗаказ 751/54Тираж 590Подписное

Производственно-по.лиграфическое предприятие, г. Ужгород, ул. Проектиая, 4

ратора соединен с адресным входом муль- типлексора, выходы мультиплексора соединены с входами регистра, выход которого является дополнительным выходом шифра- тора.

2.Шифратор по п. 1, отличающийся тем, что каждый блок кодирования состояния импульсной последовательности со держит два сдвиговых регистра, триггер, четыре дифференцирующих цепочки, элемент ИЛИ, два элемента И, первые входы которых являются управляющим входом блока, второй вход первого элемента И является сигнальным входом блока, выход первого элемента И соединен с входом установки тригге5 ра, с входом параллельной записи и входом сдвига первого и второго сдвиговых регистров соответственно, входы сдвига и параллельной записи первого и второго сдвиговых регистров соответственно соединены между собой и являются установочным вхо- дом блока, информационные входы, параллельной записи сдвиговых регистров подключены к щине нулевого потенциала, а информационные входы последовательной записи являются входами логической еди5 ницы блока, выходы третьего разряда первого сдвигового регистра, второго разряда второго сдвигового регистра и единичный выход триггера являются информационными выходами блока и через первую, вторую и третью дифференцирующие цепочки соот0 ветственно соединены с первым, вторым и третьим входами элемента ИЛИ, четвертый вход которого через четвертую дифферен- цирую щую цепочку соединен с выходом четвертого разряда первого сдвигового регистра и входом сброса триггера.

3.Шифратор по п. 1, отличающийся тем, что формирователь серии опорных импульсов содержит триггер, два счетчика, генератор импульсов, М, где М - число опорных частот, кратных 2, последовательно

0 соединенных элементов И, выходы которых являются первым выходом формирователя, входы первого элемента И соединены соответственно с выходом генератора импульсов и выходом первого разряда первого Счетчика, вторые входы последующих элементов И соединены с соответствующими выходами последующих разрядов первого счетчика, выход последнего элемента И соединен с входом второго счетчика, вход сброса которого явля ется управляющим входом

0 формирователя серии опорных импульсов, нулевым входом триггера, единичный вход которого соединен с выходом третьего разряда второго счетчика, а единичный выход которого является вторым выходом формирователя серии опорных импульсов.

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор псевдослучайной М-последовательности | 1985 |

|

SU1264317A2 |

| Устройство кодирования и декодирования сигналов звукового вещания | 1987 |

|

SU1711331A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Устройство для сопряжения датчиков с ЭВМ | 1983 |

|

SU1129600A1 |

| Формирователь кодов для рельсовой цепи | 1990 |

|

SU1753598A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА ИНФОРМАЦИИ | 1991 |

|

RU2018970C1 |

| Цифровой синтезатор частоты | 1984 |

|

SU1252939A1 |

| СПОСОБ УПРАВЛЕНИЯ ОПТОЭЛЕКТРОННЫМ ЗАМКОМ, КЛЮЧ И ОПТОЭЛЕКТРОННЫЙ ЗАМОК | 1993 |

|

RU2081281C1 |

| СИСТЕМА ЦИФРОВОГО ЦВЕТНОГО ТЕЛЕВИДЕНИЯ | 1993 |

|

RU2103839C1 |

| Устройство для контроля цифровых узлов | 1990 |

|

SU1756894A1 |

Изобретение относится к автоматике и вычислительной технике, может иснользо- ваться в автоматизированных системах управления и контроля. Целью изобретения является расширение функциональных возможностей шифратора - преобразование состояния входного параметра типа непрерывной импульсной последовательности в код, содержаш,ий информацию о наличии (отсутствии) последовательности и сбоях. Поставленная цель достигается тем, что в устройство вводятся мультиплексор 18, регистр 19, блоки кодирования состояния, каждый из которых состоит из двух сдвиговых регистров 2 и 3, триггера 8, четырех дифференциальных цепочек 4-7, элемента ИЛИ 9, двух элементов И 10 и 11,и формирователь серии опорных импульсов, состоя- ш,ий из триггера 17, двух счетчиков 14 и 16, Мэлементов И 15-15 и генератора импульсов 13. Изобретение позволяет сократить ресурсы вычислительных средств, требуемых для обработки без уменьшения достоверности контроля, повысить скорость реакции системы, обеспечить непрерывность контроля за счет аппаратной реализации слежения. 2 3. п. ф-лы, 1 ил. I (Л 1С UD 00 00 о 1C NJ

| Шифратор | 1975 |

|

SU590825A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-03-23—Публикация

1985-10-22—Подача