I

Изобретение относится к импульсной технике.

Известны делители частоты, выполненные на основе последовательно соединенных цепочек на триггерах с импульсным счетным и, раздельным управлением, с цепями обратной связи со старших разрядов на младшие (Ij. Недостатком таких делителей частоты является возможность сбоев, обусловленных различием скоростей и порогов срабатывания транзисторов триггеров, входящих в состав делителя частоты.

Наиболее близким по технической сущности к предлагаемому является делитель частоты, содержащий п ч- 2 каскада, где п 2,3,4,..., выполненные на счетных триггерах с раздельным управлением, причем единичиые выходы триггеров с первого по п-й соединены со счетными входами соотве- ствующих последующих триггеров (2). Однако такие делители частоты также имеют недостаточную надежность из-за возможности сбоев.

Цель изобретения - повышение надежности делителя частоты.

Указанная цель достигается тем, что в предлагаемом делителе частоты нулевой выход первого триггера соединен с нулевым входом п -f 2 - го триггера, нулевой выход п -Ь i - го триггера - с единичным входом п + 2 - го триггера, д нулевой выход п -f 2 - го триггера с нулевыми входами триггеров со второго по п-й.

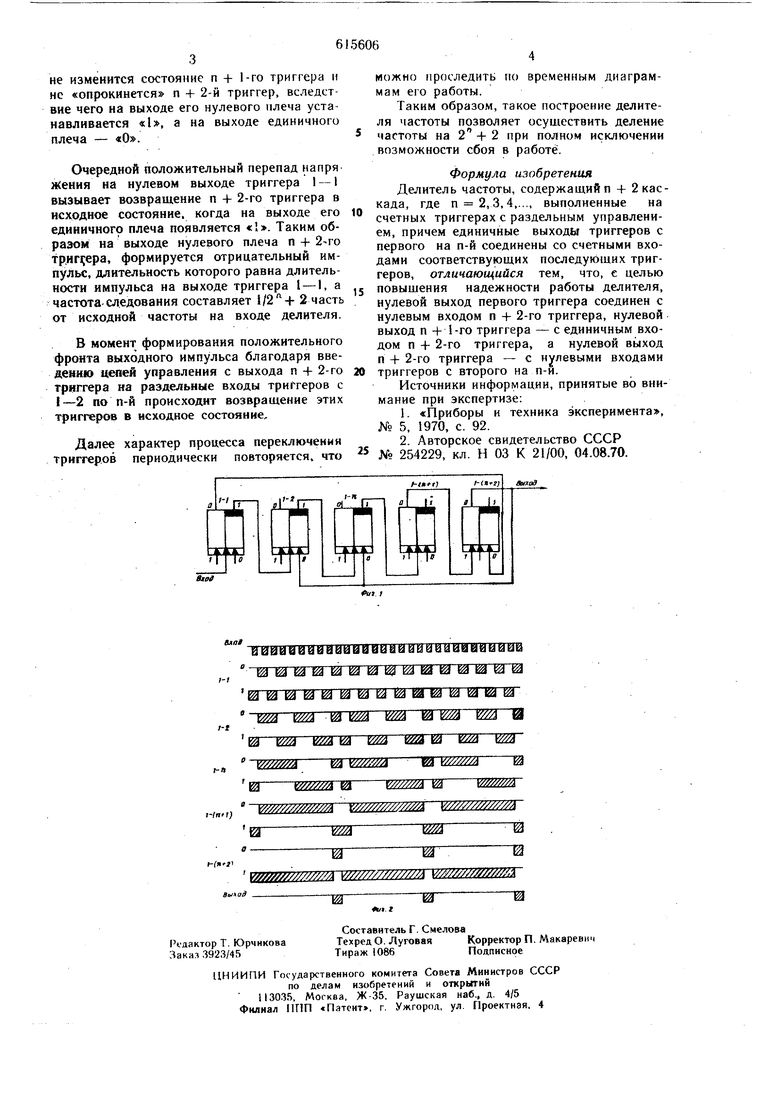

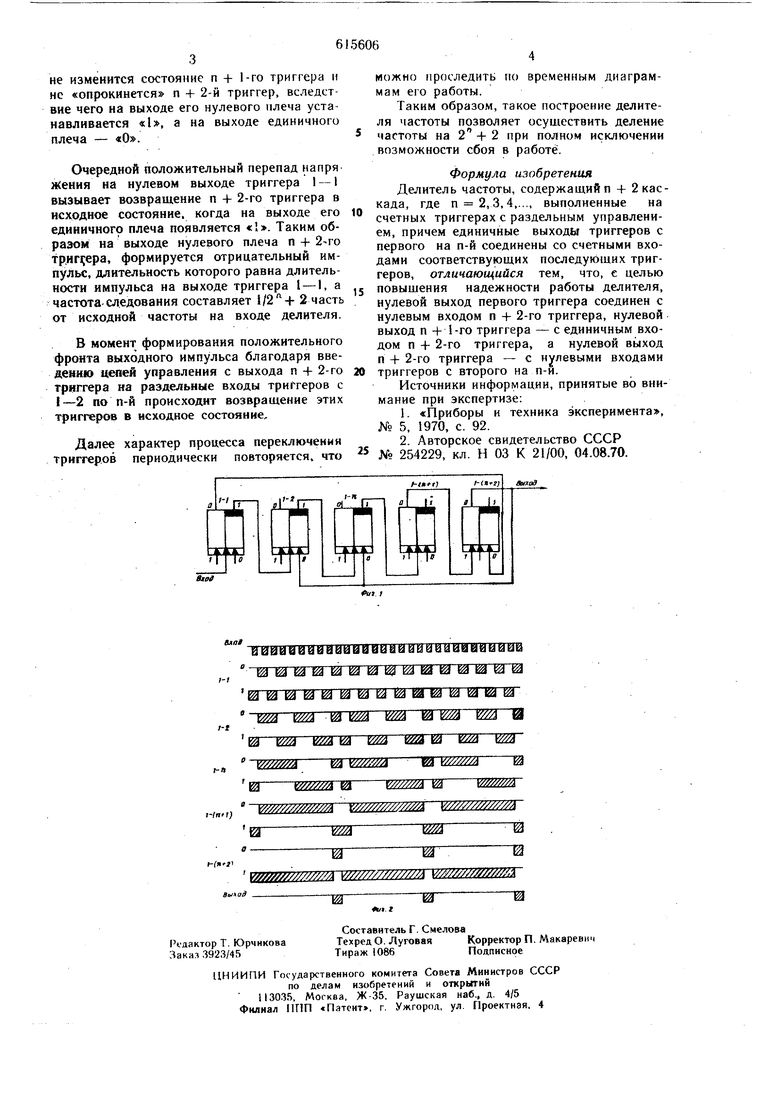

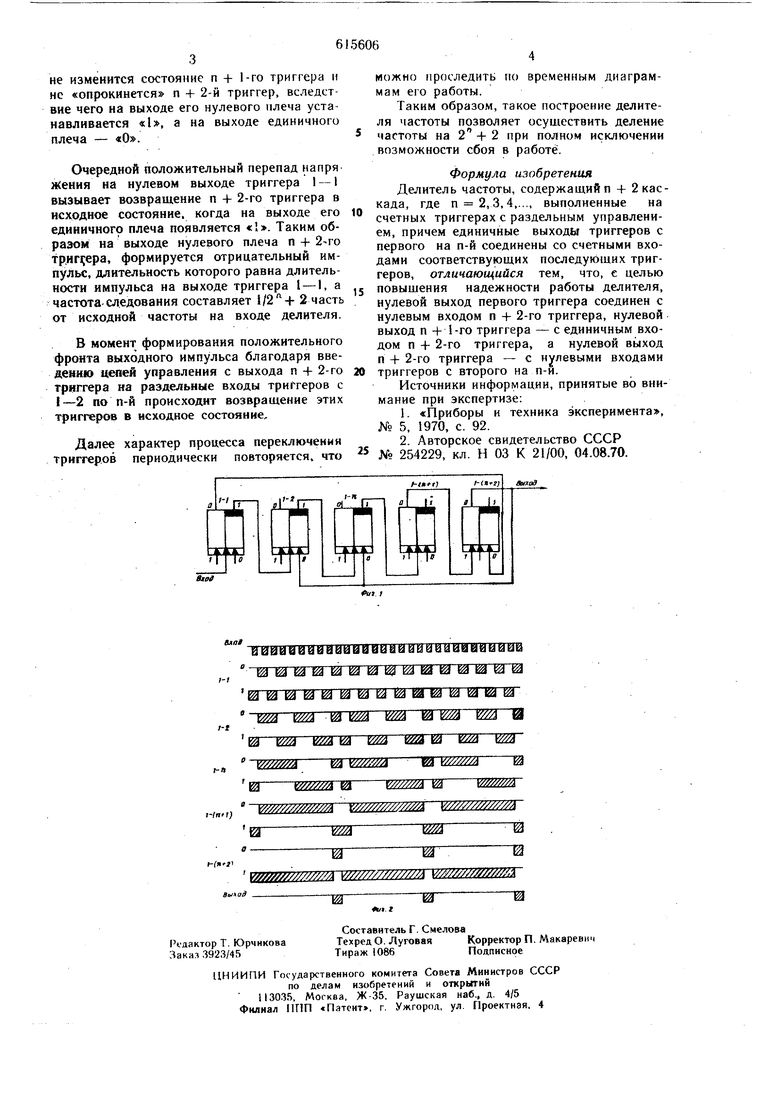

На фиг. I представлена структурная электрическая схема делителя частоты; на фиг. 2 изображены временные диаграммы, поясняющие его работу для случая п 3.

Делитель частоты на 2 -f 2 состоит из п 2 каскада на счетных триггерах 1 - 1, 1-2, ..., 1 - (п-f 2) с раздельным управлением.

Делитель частоты при п 3 работает следующим образом.

Напряжение исходной частоты подается на счетный вход триггера 1 - 1. Под дейст-вием положительного перепада входного напряжения триггер 1 - 1 «опрокидывается) не изменяя состояь ня п + 2-го триггера,)по скольку единичное плечо этого триггера находится в единичном (по выходу) состоянии.

По цепи триггеров с первого по п -f jrfi

начинается последовательный двоичный пересчет. Этот процессдлится дотех пор, пока

не изменится состояние п + 1-го триггера и НС «опрокинется п + 2-й триггер, вследствие чего на выходе его нулевого плеча устанавливается «1, а на выходе единичного плеча - «О.

Очередной положительный перепад напря Жения на нулевом выходе триггера 1 - 1 вызывает возвращение п + 2-го триггера в исходное состояние, когда на выходе его единичиого плеча появляется «. Таким образом на выходе нулевого плеча п + 2Го тр1ИГ ера, формируется отрицательный импульс, длительность которого равна длительности импульса на выходе триггера 1 - I, а частота-следования составляет 2 часть от исходной частоты на входе делителя.

В момент формирования положительного фронта выходного импульса благодаря введению цепей управления с выхода п -f 2-го триггера на раздельные входы триггеров с I-2 по п-й происходит возвращение этих триггеров в исходное состояние.

Далее характер процесса переключения триггеров периодически повторяется, что

можно проследить по временным диаграммам его работы.

Таким образом, такое построение делителя частоты позволяет осуществить деление частоты на 2 + 2 при полном исключении возможности сбоя в работе.

Формула изобретения Делитель частоты, содержащий п 4- 2 каскада, где п 2,3,4,..., выполненные на счетных триггерах с раздельным управлением, причем единичные выходы триггеров с первого на п-й соединены со счетными входами соответствующих последующих триггеров, отличающийся тем, что, е целью повыщения надежности работы делителя, нулевой выход первого триггера соединен с нулевым входом п + 2-го триггера, нулевой выход п -f i-ro триггера - с единичным входом п 4- 2-го триггера, а нулевой выход п + 2-го триггера - с нулевыми входами триггеров с второго на п-и.

Источники информации, принятые во внимание при экспертизе:

1.«Приборы и техника эксперимента, № 5, 1970, с. 92.

2.Авторское свидетельство СССР Ко 254229, кл. Н 03 К 21/00, 04.08.70.

| название | год | авторы | номер документа |

|---|---|---|---|

| СЧЕТЧЙК ИМПУЛЬСОВ | 1971 |

|

SU294256A1 |

| Генератор импульсов | 1983 |

|

SU1088101A1 |

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1986 |

|

SU1383497A1 |

| Делитель частоты следования импульсов с нечетным коэффициентом деления | 1980 |

|

SU930686A1 |

| Устройство для ввода информации | 1986 |

|

SU1397924A1 |

| Счетчик импульсов | 1973 |

|

SU496682A1 |

| Делитель частоты | 1972 |

|

SU472463A1 |

| Устройство формирования тестовых сигналов | 1986 |

|

SU1324030A1 |

| Преобразователь код-момент времени | 1981 |

|

SU970685A1 |

| Устройство для дробления стружки на станках с ЧПУ | 1983 |

|

SU1085685A2 |

Авторы

Даты

1978-07-15—Публикация

1972-08-09—Подача