Изобретение относится к импульсгной технике, а именно к преобразователям кода в непрерывную величину, и может быть использовано,.в частности при обработке сигналов в измерительных системах импульсной локации и дальнометрии .

Известен .преобразователь код-временной интервал, содержащий генератор эталонной частоты, триггер, два элемента И, схему совпадения, кодирующее устройство, элемент задержки и счетчик единичных приращений 1.

Данный преобразователь основан на суммировании приращений счетчиком, в которлй предварительно вводится код, обратный преобразуемому. Временной интервал формируется от момента началу счета до момента достижения счетчиком определенного состояния, например нулевого.

Однако данное устройство обладает ограниченными функциональными возможностями и не позволяет получить на выходе серию взаимосвязгшных временных интервалов из-за затрат времени на ввод в счетчик кода между цикла и.

Известен преобразователь кода во временной интервал,-содержащий генератрр эталонной частоты, счетчик единичных приращений, регистр преобразуемого кода и кодовый компаратор, входы которого подключены к соответствукицим выходс1М счетчика и регистра, а выход - к первому входу первого элемента И и R-входу RS-триггера, выход которого соединен с первым входом второго элемента И, вто10рой вход которого подключен к выходу генератора и второму входу первого элемента И, а выход - к счетному входу счетчика С2.

Недостатком известного устройст15ва является низкая надежность работы при широкодиапазонных преобразованиях кодов большой разрядности, которая обусловлена тем, что момент времени, соответствующий концу форми20руемого интервала, выделяется путем одновременного во всех разрядах сравнения текущего кода с заданным. Для исключения возможности появления на выходе кодового компа25ратора ложных сигналов счетчик единич ных приращений должен быть выполнен полностью синхронным. Однако реализация СИ12ХРОННОГО счетчика большой разрядности сопряжена с его зна-.

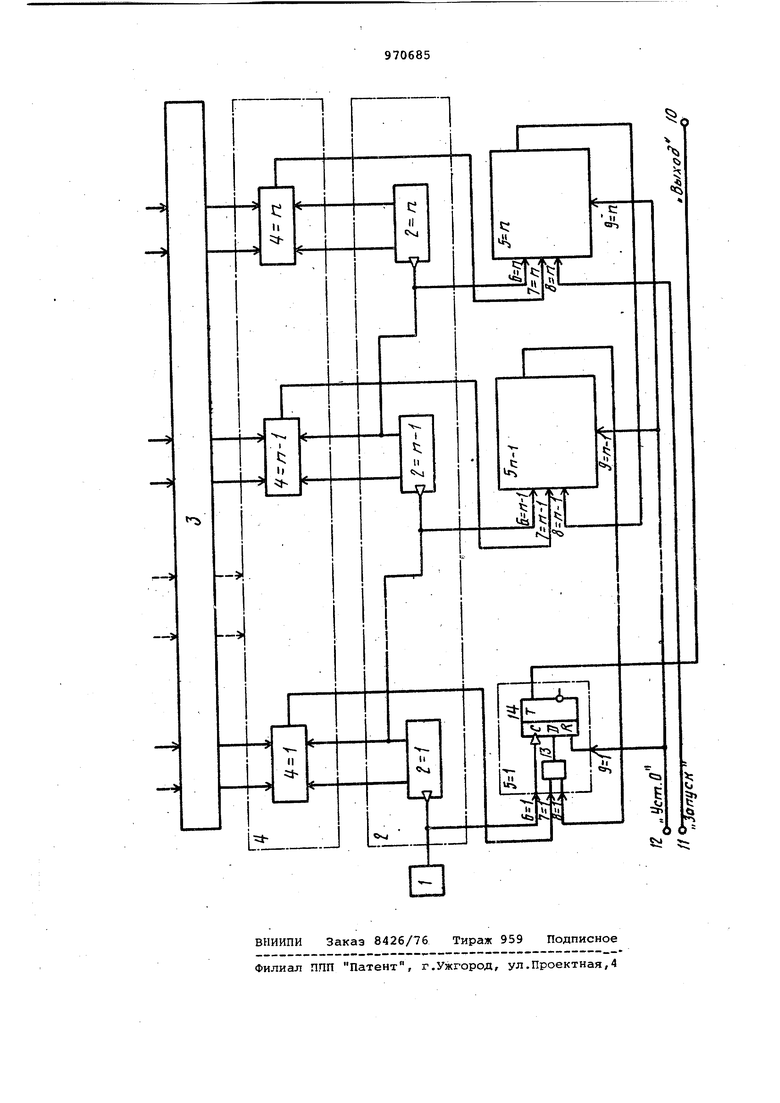

30 чительным усложнением и возрастанием объема оборудования, что повышает вероятность отказа какого-либо эле та и сбоев в работе. Кроме того, синхронный счетчик должен быть выполнен на однородных по быстродействию элементах, что также усложняет его реализацию, в результате чего снижается надежность работы преобразователя в целом. Цель изобретения - повышение на дежности преобразования. Поставленная цель достигается т что в преобразователь код-момент времени, содержащий генератор эталонной частоты, п-каскадный счетчи единичных приращений, регистр кода и выполненный на п блоках сравнения кодовый компаратор, входы кото рого соединены соответственно с вы ходами счетчика единичных приращений и регистра кода, дополнитель но введены п блоков фиксации совпа дения кодов, при этом выход генератора эталонной частоты соединен с входом первого счетного каскада счетчика единичных, приращений и первым входом первого блока фиксац совпадения кодов, первые входы остальных блоков фиксации совпадения кодов соединены с входами соответствующих каскадов счетчика единич. ных приращений, вторые входлл блоко фиксации совпадения кодов подключены к выходам соответствующих бло ков сравнения кодового компаратора третий вход п-го блока фиксации со ладения кодов соединен с шиной запуска, третьи входы остальных блоков фиксации совпадения кодов соединены с выходами последующих блоков фиксации совпадениякодов, 7 ч вертые входы блоков фиксации совпа дения кодов подключены к шине уста новки исходного состояния. Причем блок фиксаций совпадения кодов содержит последовательно включенные элемент И и D-триггер, информационный D-вход которого соединен с выходом элемента И, входы которого подключены соответственно к второму и третьему входам блока фиксации совпадения кодов, первый и четвертый входы которого соединены соответственно с С- и R-входами D-триггера, выход которого подключен к выходу блока фиксации совпадения кодов. При введении упомянутых отличительных признаков счетчик единичных приращений выполняется в виде после довательно включенных счетных каскадов, т.е. по принципу асинхронной связи синхронных каскадов ограниченной разрядности. При этом каскадьа, функционирующие на более низкой частоте счета могут быть выполнены на элементах более низкого быстродействия. Все это в целом повышает надежность работы устройства при практическом отсутствии ограничений на разрядность преобразуемых кодов. На чертеже представлена структурная схема предлагаемого преобразователя. Преобразователь код-момент времени содержит генератор 1 эталонной частоты, счетчик 2 единичных приращений, регистр 3 преобразуемого кода, кодовый компаратор 4 и п блоков фиксации совпадения кодов. Счетчик 2 единичных приращений в виде п последовательно соединенных счетных каскадов , а кодовый компаратор 4 выполнен в виде п блоков сравнения. Выход генератора 1 эталонной частоты подключен к входу первого каскада счетчика 2. Выходы каскадов счетчика 2 соединены с входами соответствующих блоков . кодового компаратора 4,к другим входам которых подключены выходы регистра 3 преобразуемого кода. Первые входы блоков фиксации совпадения кодов подключены соответственно к входам счетных каскадов вторые входы блоков фиксации совпадения кодов подключены соответственно к выходам блоков сравнения кодового компаратора 4, выход блока фиксации совпадения кодов соединен с выходной шиной 10 преобразователя, выходы блоков фиксации совпадения кодов подключены соответственно к третьим входам блоков , третий вход блока соединен с шиной 11 запуска, четвертые входы блоков соединены с шиной 12 установки в. исходное нулевое состояние. Каждый из блоков фиксации совпадения кодов содержит соединенные последовательно элемент И 13 и D-триггер 14 ,выход элемента И 13 подключен к информационному D-входу триггера 14, С-вход синхронизации триггера 14 образует первый вход 6 блока 5, входы элемента И 13 образуют соответственно второй вход 7 и третий вход 8 блока 5, R-вход триггера 14 образует четвертый вход 9 блока 5, а выход D-триггера 14 является выходом блока 5. Преобразователь работает следующим образом.. В исходном состоянии сигналы с выхода генератора 1 эталонной частоты поступают на вход соединенной последовательно цепочки счетный каскадов счетчика 2 единичных приращений. Счетчик 2 непреривно подсчитывает число поступивших на его вход импульсов, причем в каждом его каскаде осуществляется синхронный счет,связь между каскадами - ас хронная. В результате непрерывноциклического счета импульсов с эталонной частотой повторения на выходах каждого каскада счетчика 2 формируется квантованная шкапа текущего времени заданная, например в натурашьном двоичном коде. Началу преобразования код - момент времени предшествует установка в исходное нулевое состояние D-триг геров 14 блоков фиксации совпадения кодов. Затем в регистр 3 вводится код, которого в каждой из групп его разрядов, подаваемых на соответствующие блоки 4 1-4 п-1 срав нения, старший разряд группы имеет значение, инверсное по от ношению к значению соответствующего разряда кодового эквивалент воспроизводимого момента времени пр его задании в натуральном двоичном коде. Преобразование начинается при подаче на шину 11 запуска , которая, поступая на вход блока дает разрешение в этот блок на фиксацию сигнала о совпадении кодов формируемого блоком кодового компаратора 4 при установлении на в ходах счетного каскада кода сов падающего с кодом в соответствующей группе разрядов регистра 3. Разрешение на фиксацию сигнала о совпадении кодов означает подачу с входа 8 блока 5 на один из входов элемента И 13, в результате чего элемент И 13 подготавливается пропусканию сигнала i о совпаде нии кодов с входа 7 блока 5 на информационный D-вход триггера 14. Пр появлении на выходе блока сравн ния сигнала о совпадении кодов в ви де , длительностью равной периоду частоты счетного сигнала на входе каскада и поступающего далее на вход блока , производится его фиксация в блоке положительным фронтом входного для каскада счетного сигнала, подаваемого также на вход блока . Фиксация сигнала о совпадении ко дов, формируемого блоками сравнения, производится положительным фронтом того счетного сигнала, по отрицательному фронту которого, перектпочаются (изменяют свое кодовое состояние) соответствующие счетные каскады . результате этого момент фиксации сигнала о совпадении кодов, всегда приходится на устойчивые состояния счетных каскадов и примерно на середину длительности сигнала о совпадении кодов, чем исключается возможность фиксации в триггерах 14 блоков ложных сигналов (иголок), возникающих на выходах блоков сравнения в моменты прирашения кодового состояния счетных каскадов, происходящие по отрицательному фронту счетного сигнала. После фиксации в блоке сигнала о совпадении кодов в счетном каскаде в соответствующей груп.пе разрядов регистра 3, на выходе блока . появляется , которая, поступая на вход блока , дает разрешение на фиксацию в нем сигнала о совпадении кодов, формируемого блоком при установлении на выходах каскада кода, совпадающего с кодом в соответствующей группе разрядов регистра 3. В момент появления на выходе блока 1 , дающей разрешение на фиксацию в предыдущий блок , на выходах счетного каскада присутствует код, в старшем разряде которого - 1 а в остальных разрядах - О. Поэтому первой кодовой комбинацией, которая может быть выделена блоком сравнения с фиксацией сигнала о выделении в блоке 5 п-1 после получения разрешения на Фиксацию из блока , является кодовая комбинация, содержащая Ч в старшем разряде и в остальных разрядах. Эта кодовая комбинация соответствует комбинации все нули в соответствуклцих разрядах кодового эквивалента воспроизводимого момента времени при его прюдставлении В натуральном двоичном коде. Фиксация сигнала о совпадении кодов в блоке производится положительным фронтом входного счетного сигнала каскада , подаваемого также на вход блока . После фиксации в блоке сигнала о совпадении кодов на выходах счетного каскада и в соответствующей группе разрядов регистра 3 на выходе блока появляется , дающая разрешение на фиксацию сигнала совпадения кодов в блок . Далее преобразователь работает аналогично. Таким образом, происходит последовательная фиксация сигналов о совпадении кодовых состояний счетных каскадов с соответствующими группами разрядов регистра 3, начиная с групп старших разрядов. Полохсительный фронт сигнала, появляющийся на выходе блока , и следовательно на шине 10 в момент фиксации сигнала совпадения кодов на выходах счетного каскада с соответствующей группой разрядов регистра 3 задает момент времени, соответствующий преобразуемому коДУ. После окончанияпреобразования каждый из блоков .устанавливдется в исходное нулевое состояние следующим после окончания сигнала совпадения кодов на входе 7 блока 5 положительным фронтом, соответствующего счетного сигнала, поступающего на вход 6 блока 5 и следовательно на С-вход триггера 14. Длительность i на выходной шине 10 равна периоду генератора 1. Таким образом, предлагаемый пре образователь в целом представляется цепочкой структурно однородных .каскадов, взаимодействие которых ос 14ествляется последовательно во времени и асинхронно. Требования к син хронности счета возникают только на уровне каскада ограниченной разрядности (принципиально каскад может с держать только один счетный разряд, т.е. счетчик в целом может быть пол ностью асинхронным). Это обстоятель ство, а также возможность применени в предлагаемом устройстве элементов пониженного по мвре роста числа кас кадов быстродействия обеспечивают предлагаемому устройству более высокую надежность. . . Формула изобретения 1. Преобразователь код-момент вр мени, содержащий генератор эталошю частоты , п - каскадный счетчик един ных приращений, регистр кода и выпо ненный на п блоки - сравнения кодовы компаратор, входы которого соединен соответственно с выходами счетчика единичных приращений и регистра кода,отли чающий с я тем, что, с целью повышения надежности : преобразования, в него дополнительно введены п блоков фиксации совпадения код СЭВ, при этом выход генератора эталонно ; частоты соединен с входом первого счетного каскада счетчика единичных приращений и первым входом первого блока фиксации совпадения кодов, первые входы остальных блоков фиксации совпадения кодов соединены с входами соответствующих каскадов счетчика единичных приращений, вторые входы блоков фикса- . ции совпадения кодов подключены к выходам соответствующих блоков сравнения кодового компаратора, третий вход п-го блока фиксации совпадения кодов соединен с шиной запуска, третьи входы остальных блоков фиксации совпадения кодов соединены с выходами последующих блоков фиксации совпадения кодов, а четвертые входы блоков фиксации подключены к шине установки исходного состо;1ния. , 2. Преобразователь по п.1 отличающийся тем, что блок фиксации совпадения кодов выполнен на последовательно соединенных элементе И и D-триггере, информационный D-вход которого соединен с выходом элемента И, входы которого подключены соответственно ко второму и третьему входам блока фиксации совпадения кодов, первый и четвертый входы которого соединены ссГответственно с С- и R-входами D-триггера, выход которого .подключен к выходу блока фиксации совпадения кодов. . Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР №363207, кл. Н 03 К 13/20, 24.05.71., 2.Гихис Э.И. Преобразователи информации для электронных цифронлх вычислительных устройств. М., 1975, с. 268-270, рис. 6-9 б (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь код-момент времени | 1982 |

|

SU1034176A1 |

| Преобразователь моментов времени в код | 1979 |

|

SU855995A1 |

| Адаптивный аналого-цифровой преобразователь | 1980 |

|

SU875622A1 |

| Преобразователь код-временной интервал | 1979 |

|

SU822348A1 |

| Адаптивный аналого-цифровой преобразователь | 1979 |

|

SU864552A1 |

| Преобразователь код-напряжение с широтноимпульсной модуляцией | 1978 |

|

SU790283A1 |

| Адаптивный аналого-цифровой преобразователь | 1979 |

|

SU866734A1 |

| Устройство для вычисления функции линеаризации | 1980 |

|

SU905831A1 |

| Адаптивный аналого-цифровой преобразователь | 1980 |

|

SU942257A1 |

| Преобразователь код-напряжение | 1989 |

|

SU1635258A1 |

Авторы

Даты

1982-10-30—Публикация

1981-04-24—Подача