(54) ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО КОДОВ БОУЗА - ЧОУДХУРИ - ХОКВИНГЕМА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исправления ошибок в системах хранения и передачи информации в кодовой комбинации | 1984 |

|

SU1231503A1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ РАДИОВЕЩАТЕЛЬНОЙ ПЕРЕДАЧИ ЦИФРОВЫХ СООБЩЕНИЙ | 1994 |

|

RU2110148C1 |

| СПОСОБ ДЕКОДИРОВАНИЯ КОДОВ БОУЗА-ЧОУДХУРИ-ХОКВИНГЕМА ПО МАКСИМУМУ ДИСКРЕТНОЙ ФУНКЦИИ ПРАВДОПОДОБИЯ С ПРИМЕНЕНИЕМ ГРАФОВ БЫСТРЫХ ПРЕОБРАЗОВАНИЙ | 2011 |

|

RU2452087C1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ С МЯГКИМИ РЕШЕНИЯМИ ДЛЯ ДВУХСТУПЕНЧАТОГО КАСКАДНОГО КОДА | 2012 |

|

RU2485683C1 |

| Декодер кода Боуза-Чоудхури-Хоквингема с каноническим декодером Хэмминга | 2018 |

|

RU2704499C1 |

| Устройство для декодирования кодов Боуза-Чоудхури-Хоквингема | 1982 |

|

SU1168946A1 |

| Декодер кода БЧХ | 1987 |

|

SU1457166A1 |

| Способ кодовой цикловой синхронизации для каскадного кода Рида-Соломона и Боуза-Чоудхури-Хоквингема [РС(32,16,17), БЧХ(31,16,7)] при одновременном применении жестких и мягких решений | 2020 |

|

RU2747623C1 |

| ПАРАЛЛЕЛЬНЫЙ РЕКОНФИГУРИРУЕМЫЙ КОДЕР БЧХ КОДОВ | 2015 |

|

RU2591474C1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2001 |

|

RU2197788C2 |

Изобретение относится к радиотехнике и может использоваться в вьтислительной технике для определения и коррекции ошибок.

Известно декодирующее устройство

кодоЬ Боуза-Чоудхури-Хоквингема (БЧХ) содержащее входной регистр памяти, выходы разрядов которого подключены к входам соответствующих блоков поверочных комбинаций, а также ft формирователей сигнала о невозможности принятия достоверного решения и W блоков памяти ( П -число разрядов входного регистра памяти) LlJ .

Однако известное устройство характеризуется ограниченным б{ 1стродействием и большим количестЬом элементов для схемной реализации, а также невозможностью применения кодов с большим количеством разрядов.

Цель изобретения - повышение быстродействия.

Для этого в декодирующее устройство кодов БЧХ, содержащее входной регистр памяти, выходы разрядов которого

подключены к входам соответствующих блоков поверочных комбинаций, а также Н формирователей сигнала о невозможности принятия достоверного решения и И блоков памяти ( И -число разрядов входного регистра пам$1ти), введены для каждого разряда суммирующая матрица и два компаратора, при этом выход блока поверочных комбинаций каждого разряда через суммирукядую матрицу подключен к прямому Входу первого компаратора и к инверсному входу второго компаратора, а выходы первого и второго компараторов подключены к соответствующим входам блока памяти и формирователя сигнала о невозможности принятия достоверности решения, причем на другие входы первого и второго компараторов подано опорное иапр51жение.

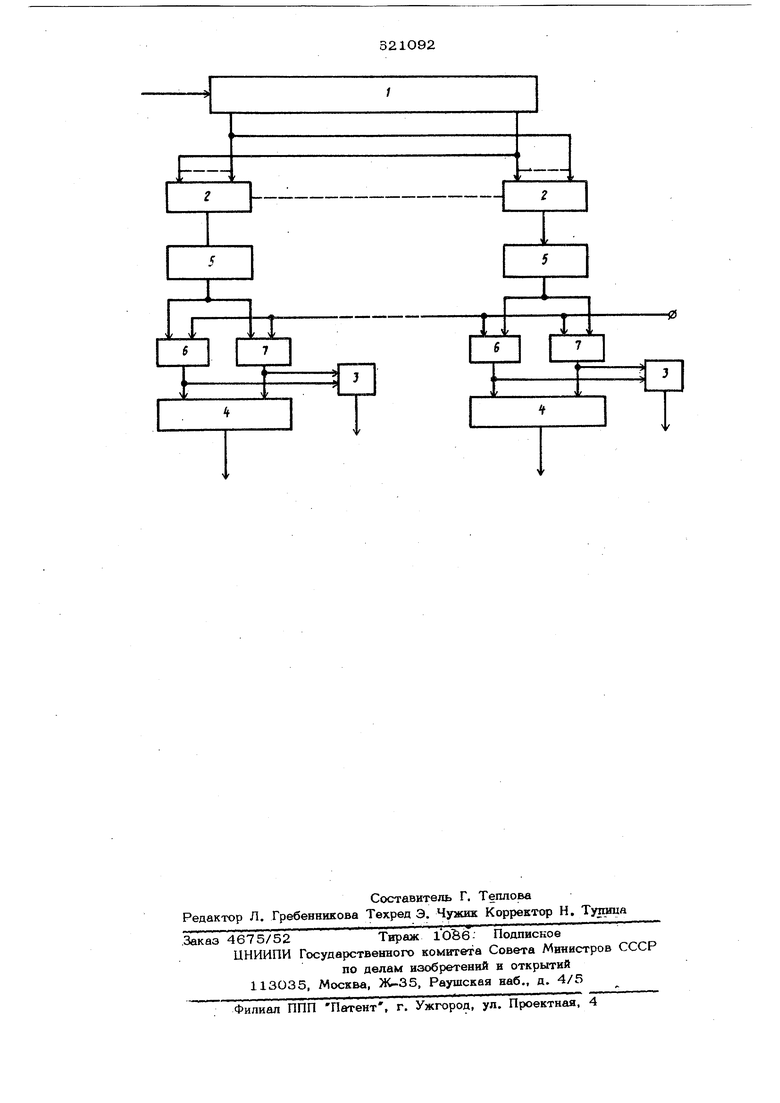

На чертеже дана структурная электрическая схема предлагаемого устройства.

Декодирующее устройство кодов БЧХ содержит входной регистр 1 памяти, выходы разрядов которого подключены к вхдам соответствукяцих блоков 2 поверочных комбннаошй, а также tt формирова|Твлей 3 сигнала о невозможности принятия достоверного решения и Я блоков 4 памяти ( Ч -число разрядов входного регистра 1 памяти). Устройство содержит также для каждого разряда суммирующую матрицу 5 и два компаратора 6 и 7, при этом выход блока 2 каждбго разряда через суммирующую матрицу 5 подключен к прямому входу первого компаратора б и к инверсному входу второго компаратора 7, а выходы первого и второго компараторов 6 и 7 подключены к соответствующим входам блока 4 памяти и формирователя 3, причем на другие входы первого и второго компараторов 6 И7 подано опорное напряжение.

Устройство работает следующим образом.

С выхода каждого, разряда входного регистра 1 памяти через блок 2 поверочных комбина1шй информационная посылка поступает на суммирующую матрицу 5, с выхода которой напряжение подается на входы двух компараторов 6 и 7, на другие входы которых подано опорное напряжение.

На выходах компараторов 6 и 7 появляется сигнал, соответствующий 1 или О передаваемого информационного разряда, если преобладает количество соответствующих поверочных комбинаций илисигнал отсутствует при равном количестве поверочных комбинаций, соответствующих 1 или О переданного информационного разряда. В случае отсутствия сигнала на выходах компараторов 6 и 7 в блоке 4 памяти сохраняется .предыдущее значение разряда передаваемой команды, и формирователем 3 вырабатывается сигнал о невозможности принятия достоверного (с заданной вероятностью ошибки) решения о передаваемой информации.

Прейлагаемое усаройство позволяет повысить быстродействие путем исключения промежуточных степеней преобразования {сокращение общего числа требуемых операций вьтисления, а следовательно, и значительное сокращение элементной базы).

Ф

изобретения

о р м у л а

Декодирующее устройство кодов БоузаЧоудхури-Хоквингема (БЧХ), содержащее входной регистр памяти, выходы разрядов которого подключены, к входам соответствующих блоков поверочных комбинаций, а также Ц формирователей сиг нала о невозможности принятия достоверного решения и П блоков памяти ( И -число разрядов входного регистра памяти), отличающееся тем, что, с целью повьщ1ения. быстродействия, введены для каждого разряда суммирующая матрица и два компаратора, при этом выход блока поверочных комбинаций каждого разряда через суммирующую матрицу подключен к прямому входу первого компаратора и к инверсному входу второго компаратора, а выходы первого и второго компараторов подключен к соответствующим входам блока памяти и формирователя сигнала о невозможности принятия достоверного решения, причем на другие входы первого и второго компараторов подано опорное напряжение.

Источники информации, принятые во внимание при экспертизе:

Авторы

Даты

1978-08-25—Публикация

1977-04-08—Подача