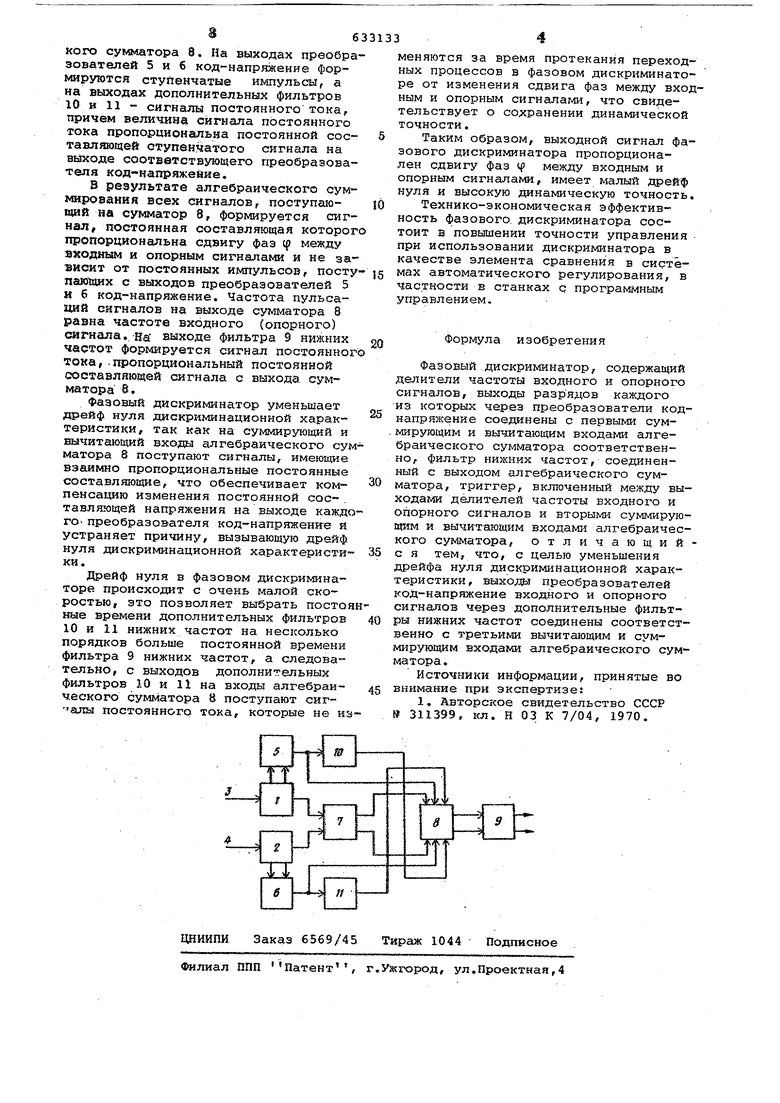

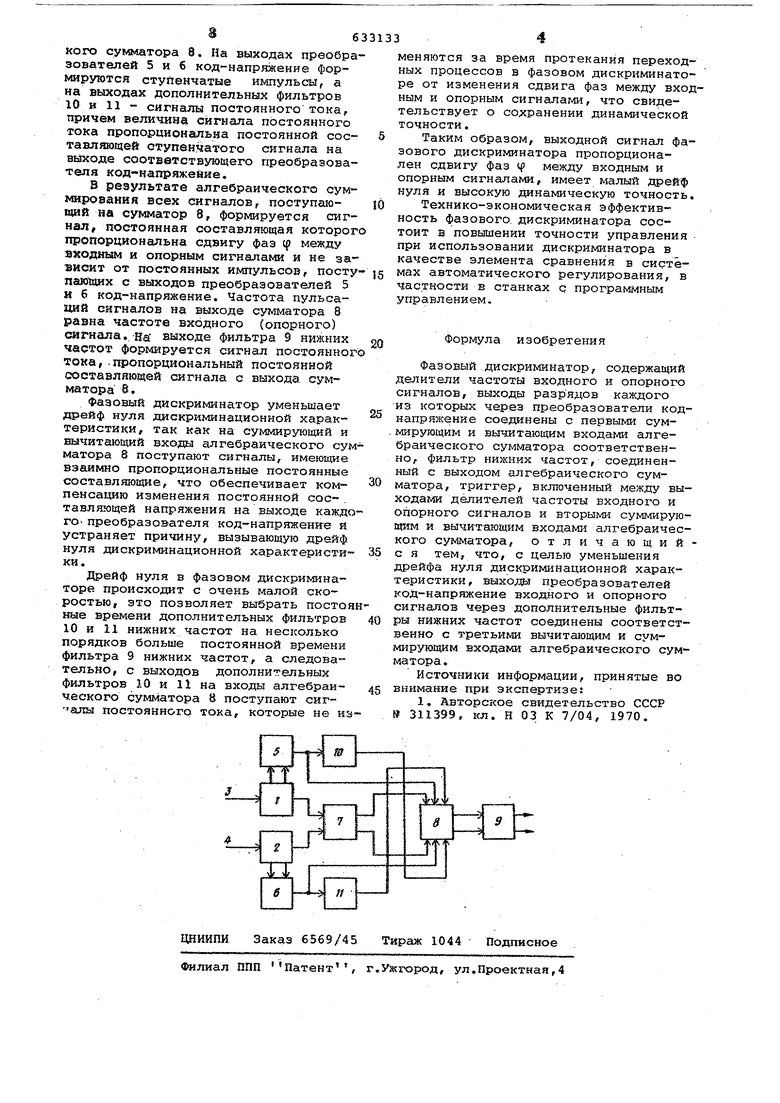

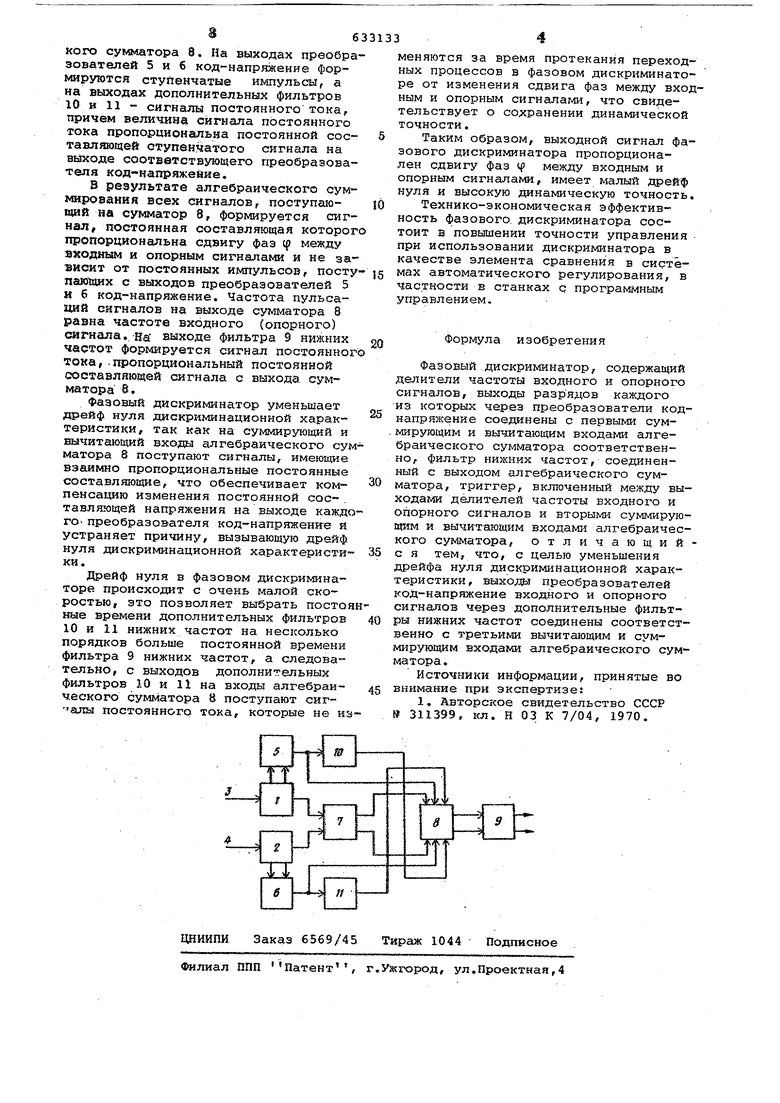

Изобретение относится к области автоматики, в .частности к системам автоматического управления, Известен фазовый дискриминатор , содержащий делители частоты вкодного И опорного сигналов, выходы разрядов каждого из которых lepes преобразователи код-напряжение соединены с первы ми .ГЛрующим и вычитающим входаNm алгебраического сумматора соответ ствекно, фильтр нижних частот, соеди ненный с выходом алгебраического сум матора, триггер, включенный между выходами делителей частоты входного и -опорного сигналов и вторьп.и cyм № ps1oщим и вычитающим входами алгебраического сумматора ij . Однако известный фазовый дискрими™ натор обладает значительным дрейфом нуля дискриминационной характеристики, который вызывается изменениями постоянных составляющих напряжений на выходах преобразователи код-напряжение, в свою очередь, вызванных нестабильностью уровней напряжений, поступ ющих на входьт преобразователей. Цель изобретения - уменьшение дрей фа нуля дискриг данационной характеристики. Для этого в предлагаемом фазовом дискриминаторе выходы преобразователей код-напряжение входного и опорного сигналов через дополнительные фильтры нижних частот соединены соответственно с третьими вычитающими и суммирующими входами алгебраического сумматора. На чертеже изображена функциональная электрическая схема предложенного фазового дискриьетнатора„ Фазовый дискриминатор содержит делители частоты 1 и 2 входного и опорного сигналов 3 и 4, преобразователи 5 и б код-напряжение, триггер , алгебраический сумматор 8, фильтр 9 нижних частот ФНЧ) и дополнительные фильтры Ю к 11. Фазовый дискриминатор работает следующим образом. Входные сигналы 3, имеющие фазовый сдвиг ф относительно опорных сигналов 4, поступают на делители 1 и 2 частоты. С выхода последних сигналы поступают на входы триггера 7, в результате чего на выходах этого триггера формируются противофазные импульсы, пропорциональные фазовому сдвигу If , поступающие на суммиру. и вычитающий входы алгебраичес86кого сумматора 8. На выходах преобра зователей 5 и б код-напряжение Формируются ступенчатые импульсы, а на выходах дополнительных фильтров 10 и 11 - сигналы постоянного тока, причем величина сигнала постоянного тока пропорциональна постоянной соетавляющей ступенчатого сигнала на выходе соответствующего преобразователя код-напряжейие. В результате алгебраического суммирования всех сигналов, поступаюадий на сумматор 8, формируется сигнал, постоянная составляющая которог пропорциональна сдвигу фаз (f между входным и опорным сигналами и не зависит от постоянных импульсов, посту паЮйшх с выходов преобразователей 5 н 6 код-напряжение. Частота пульсаций сигналов на выходе сумматора 8 равна частоте входного (опорного) сигнала,.-Ва выходе фильтра 9 нижних частот формируется сигнал гюстояыног тока,.пропорциональный постоянной составляющей сигнала с вьзхода сумматора 8 Фазовый дискриминатор уменьшает да1ейф нуля дискриминационной характеристики, так как на суммирующий и вычитающий входы алгебраического сум матора 8 поступают сигналы, имеющие взаимно пропорциональные постоянные составляющие, что обеспечивает компенсацию изменения постоянной сое-. тавляющей напряжения на выходе каждо ГО преобразователя код-напряженнге и устраняет причину, вызывающую дрейф нуля дискриминационной характеристики. Дрейф нуля в фазовом дискриминаторе происходит с очень малой скоростью, это позволяет выбрать посто ные времени дополнительных фильтров 10 и 11 нижних частот на несколько порядков больше постоянной времени фильтра 9 нижних частот, а следовательно, с выходов дополнительных фильтров 10 и 11 на входы алгебрамческого сумматора tt поступают сигалы постоянного тока, которые не и меняются за время протекания переходных процессов в фазовом дискриминаторе от изменения сдвига фаз между входным и опорным сигналагл, что свидетельствует о сохранении динамической точности. Таким образом, выходной сигнал фазового дискриминатора пропорционален сдвигу фаз Ц) между входным и опорным сигналами, имеет малый дрейф нуля и высокую динамическую точность. Технико-экономическая эффективность фазового, дискриминатора состоит в повышении точности управления при использовании дискриминатора в качестве элемента сравнения в системах автоматического регулирования, в частности в станках Q программным управлением. Формула изобретения Фазовый дискриминатор, содержащий делители частоты входного и опорного сигналов, выхода разрядов каждого -из которых через преобразователи коднапряжение соединены с первыми суммирующим и вычитающим входами алгебраического сумматора соответственно, фильтр нижних частот, соединенный с выходом алгебраического сумматора, триггер, включенный между выходами делителей частоты входного и опорного сигналов и вторыми суммируюЩ5{м и вычитающим входами алгебраического сумматора, отличающийс я тем, что, с целью уменьшения дрейфа нуля дискриминационной характеристики, выходы преобразователей код-напряжение входного и опорного сигналов через дополнительные фильтры нижних частот соединены соответственно с ypeTbHNm вычитающим и суммирующим входами алгебраического сумматора . Источники информации, принятые во внимание при экспертизе: 1, Авторское свидетельство СССР № 311399, кл. Н 03 К 7/04, 1970.

| название | год | авторы | номер документа |

|---|---|---|---|

| Фазовый дискриминатор | 1981 |

|

SU1050092A1 |

| Способ формирования периодических двуполярных колебаний с заданным фазовым сдвигом и устройство для его реализации | 2016 |

|

RU2625047C1 |

| Фазовый дискриминатор | 1983 |

|

SU1171970A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Цифроаналоговое устройство слежения за задержкой псевдослучайной последовательности импульсов | 1982 |

|

SU1083390A1 |

| ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 1991 |

|

RU2040852C1 |

| Устройство для коррекции частоты опорного генератора в квантовом стандарте частоты | 1990 |

|

SU1809528A1 |

| Частотный дискриминатор | 1982 |

|

SU1116527A1 |

| Фазовращатель дискретного действия | 1981 |

|

SU1005272A1 |

| Помехоустойчивый цифровой фазометр | 1979 |

|

SU1002979A1 |

Авторы

Даты

1978-11-15—Публикация

1977-03-28—Подача