Изобретение относится к фазометрии и может использоваться при проведении измерений в условиях помех.

Известен, помехоустойчивый цифровой фазометр, содержащий триггерный преобразователь аналог-код, включающий в себе формирующие устройства, управляемый триггер, квантующий генератор, делитель частоты, триггер, ключевые схемы, счетчик, узел управления формирователем, содержащий три триггера и ключевую схему, блок анализа области значений измеряемого сдвига фаз, содержащий элементы совпадения, ключевой элемент и элемент ИЛИ, триггер и узел коррекции результатов измерения . состоящий из элемента совпадений и ключевой схемыД11.

Недостатком этого помехоустойг чивого цифрового фазометра является его относительно высокая сложность, относительно низкое быстродействие, а также невозможность его использования для измерения фазовых сдвигов узкополосных случайных процессов.

Известен помехоустойчивый цифровой фазометр I содержащий первый и второй дискриминаторы полярности, входы которых .соединены соответственно с первым и вторым входами помехоустойчивого цифрового фазометра, генератор опорных импульсов, первый и второй элементы совпадения, триггер, блок усреднения и блок регистрации, входы которого соединены с выходами блока усредкения 2.

Недостатками известного помехоустойчивого цифрового фазометра являются низкое быстродействие измерения и отно10сительно низкая точность измерения в , условиях помех.

Целью изобретения является повышение точности и быстродействия.

Поставленная цель достигается

15 тем, что в помехоустойчивый цифровой фазометр ..содержащий первый и второй дискриминаторы полярности, генератор опорных импульсов, первый и второй элементы совпадения, триггер,

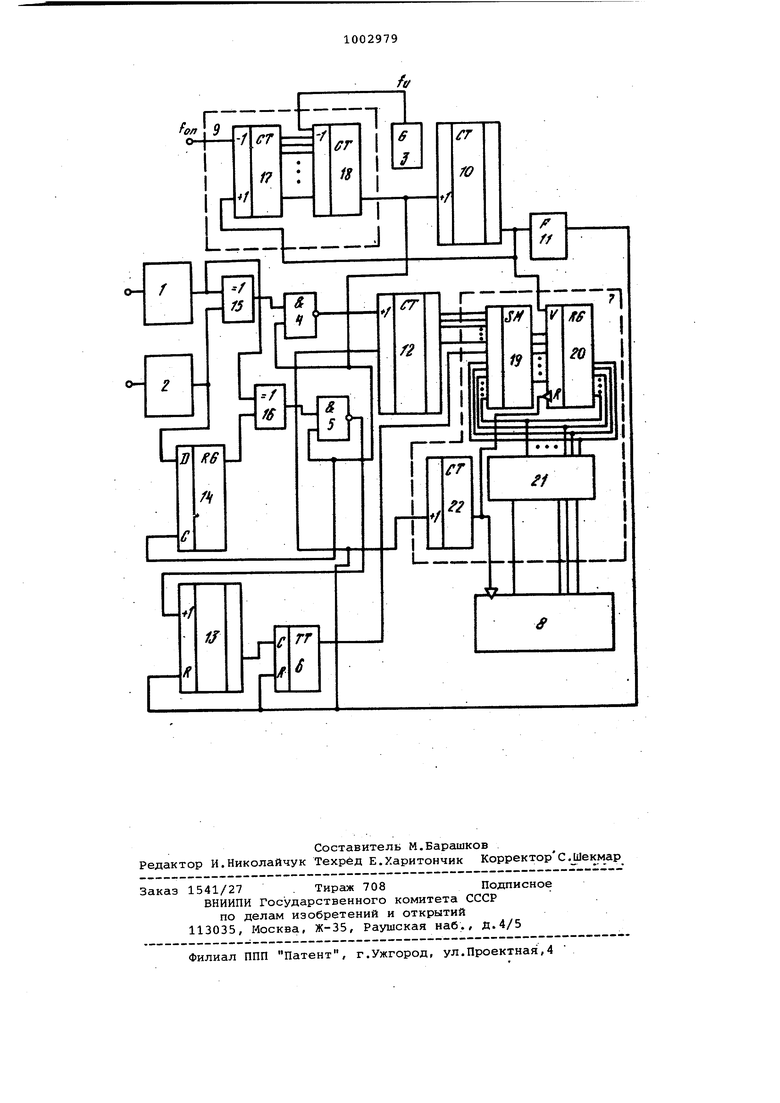

20 блок усреднения и блок регистрации, входы которого соединены с выходами блока усреднения, введены умножитель частоты, делитель частоты, формирователь, первый и второй счетчики, ре. 25 ,гистр сдвига и первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, причем Первые входы первого и второго элементов ВСКЛЮЧАЮЩЕЕ ИЛИ соединены с выходом первого дискриминатора полярности, 30 второй вход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с выходом второго дидкриминатора полярности и информационным входом регистра сдвига, выход которого соединен с вторым входом второго элемента ИКЛЮЧАЮЦЕЕ ИЛИ, выходы первого и второго элемен тов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с пео;выми входами соответственно первого и второго элементов совпадения, вторые входы которых соединены с тактовым входом регистра сдвига, выходом умножителя частоты и входом делителя частоты/ выход которого соединен с входом формирователя, управляющим входом умножителя частоты и тактовым входом блока усреднения, информационные входы которого соединены с выходами первого счетчика, сч.етный вход которого соединен с выходом первого элемента совпадения, знаковы вход блока усреднения соединен с выходом триггера, информационный вход которого соединен с выходом переноса второго счетчика, счетный вход которого соединен с выходом второго элемента совпадения, выход формировател соединен с входами сброса первого и второго счетчиков, триггера и управл ющим входом блока усреднения, выход генератора опорных импульсов соедине с тактовым входом умножителя частоты Умножитель частоты содержит разностный счетчик и вычитающий счетчик с регулируемым коэффициентом пересче та , управляющие входы которого соединены с выходами i разностного счетчика, .входы вычитания и суммирования которого являются соответственно информационным и управляющим входами умножителя частоты, выход которого является выходом вычитающего счетчика с регулируемым коэффициентом пересчета, тактовый вход которого является тактовым входом умножителя частоты. Блок усреднения содержит комбинационный сумматор, регистр, сдвигатель кодов и вспомогательный делитель, выход которого является управляющим выходом блока усреднения, который соединен с входом сброса регистра, информационные входы которого соединены с выходами комбинационного сумматора, знаковый вход и первая группа входов котррого являются соответственно знаковым и информацио ными входами блока усреднения, тактовый вход которого является тактовы входом регистра, управляющий вход блока усреднения является счетным входом Вспомогательного делителя, вы ходы регистра соединены с второй группой входов комбинационного сумматора и входами сдвигателя кодов, выходы которого являются выходами блока усреднения. / На чертеже показана структурная схема помехоустойчивого цифрового фазометра. Помехоустойчивый цифровой фазометр содержит первый 1 и второй 2 дискриминаторы полярности, генератор 3 опорных импульсов, первый 4 и второй 5 элементы совпадения, триггер б, блок 7 усреднения и блок 8 регистрации, умножитель 9 частоты, делитель 10 частоты, формирователь 11, первый 12 и второй 13 счетчики, регистр 14 сдвига и первый 15 и второй 16 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, умножитель 9 частоты содержит разностный счетчик 17 и вычитающий счетчик 18 с регулируемым коэффициентом пересчета. Блок 7 усреднения содержит комбинационный сумматор 19, регистр 20, сдвигатель 21 кодов и вспомогательный делитель 22. Помехоустойчивый цифровой фазометр работает следующим образом. Исследуемые сигналы, сдвиг фаз между которыми следует определить, подаются на первый и входы устройства. На управляющий вход помехоустойчивого цифрового фазометра подается сигнал с частотой исследуе.. Если хотя бы один мых сигналов из исследуемых сигналов не содержит случайной составляющей, характеризующей воздействие помехи, в качестве опорного сигнала можно использовать выходной сигнал дискриминатора полярности, вход которого соединен с входом, на который подан исследуемый сигнал без случайной составляющей . Если это условие не выполняется, , например, если проводится измерение сдвига фаз между узкополосными случайными сигналами, поступающими от виброакселерометров, установленных на исследуемом вращающемся объекте, в качестве опорного сигнала можно ис-. пользовать сигнал от датчика оборотной частоты, установленного на объекте . Умножитель 9 частоты обеспечивает получение на его выходе равномерно распределенных импульсов с частотой , в N раз превышающей опорную частоту на его информационном входе, причем N определяется частотой сигналов , поступающих на управляющий вход умножителя 9 частоты с выхода делителя 10 частоты, которая в N раз меньше частоты импульсов на выходе умножителя 9 частоты. Таким Образом, коэффициент умножения N равен коэффициенту деления частоты 10 делителя . В установившемся режиме частота импульсов на обоих входах разностного счетчика 17 одинакова и код, , зафиксированный этим счетчиком на его выходах и определяющий коэффи циент деления вычитающего счетчика 18, не изменяется. Если частота спорных импульсов увеличится (уменьшится), код на выходах разностного счетчика уменьшится (увеличится, что вызовет увеличение (уменьшение частоты импульсов на выходе вычитающего счетчика 18, так как уменьшается (увеличивается ) его коэффициент деления. Это обеспечивает увеличение (уменьшение ) частоты импульсов на выходе делителя 10, и устройство переходит в установившийся режим рабо ты,- Коэффициент деления частоты импульсов делителя 10 определяет точность определения фазового сдвига и равен , где йЧ- дискретность оп ределения оценки фазового сдвига в радианной мере. Аналогично для получения оценки -180 где в градусной мере N дискретность определения оценки фазового сдвига в градусной мере. Например, если оценка фазового сдвига проводится с точностью (дискретностью в 1°, то коэффициент деления делителя 10N 180. Коэффициен пересчета первого счетчика 12 должен превышать N, а коэффициент пересчет второго счетчка 13 и длина (количест во разрядов ) регистра 14 сдвига долж ны быть равным/2;. Исследуемые сигналы с выходов первого 1 и второго 2 дискриминаторов полярности поступают на входы первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 15 который обеспечивает выделение моме тов времени, характеризующихся разной полярностью исследуемых сигнало что приводит к появлению единичного логического сигнала на выходе пёр,вого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 15. Этот единичный логический сигнал, поступая на вход первого элемента 4 совпадения, разрешает прохождение через него импульсов с выхода умножителя 9 частоты, которые считают- ся первым счетчиком 12. Так как Изм рение оценки фазового сдвига подводится в течение полупериода, в счет чике 12 фиксируется код, характериз ющий длительность несовпадения знаков входных сигналов в относительны единицах, т.е. по существу модуль фазового сдвига Ч независимо от последовательности переходов исследуемых сигналов через нулевое значение. Логический сигнал с выхода одног из дискриминаторов 1 полярности подается на первый вход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 16, на второй вход которого подается логический сигнал с выхода второго дискриминатора полярности, задержанный на чет верть периода регистра 14 сдвига. Выходной сигнал второго элемента ИС КЛЮЧАЮЩЕЕ ИЛИ 16 управляет вторым элементом совпадения, который обесп чивает пропускание импульсов с выхо да умножителя 9 частоты на счетный ход второго счетчика 13, причем, сли за время получения данной оцени фазового сдвига на его вход постуит более N/2 импульсов, на выходе того счетчика формируется сигнал переноса, который перебрасывает триггер б, выходной сигнал которого хаактеризует знак получаемой оценки фазового сдвига. Получаемые оценки модуля фазового сдвига с учетом знака накапливаются в регистре 20 блока 7 усреднения путем суммирования с ранее накопленными результатами с помощью сумматора 19. Каждая оценка фазового сдвига начинается и оканчивается появлением сигнала на выходе делителя 10, по которому проводится запись в регистр 20 очередного значения суммы и запуск формирователя 11 импульса, который обеспечивает формирование импульса сброса счетчиков 12 и 13 и триггера 6. Этот импульс также увеличивает на единицу состояние вспомогательного делителя 22, коэффициент деления которого равен числу усредняемых оценок и по достижении этого числа на выходе вспомогатель;ного делителя 22 появляется сигнал, разрешающий считывание информации в блок 8 регистрации, а по заднему фронту - очистку регистра 20. Так как число устраняемых оценок удобно выбрать из ряда 2, 4, 8, 16 и т.д., т.е. целой степени числа 2, операция деления, необходимая для получения среднего значения, сводится к сдвигу кода, для чего используется сдвигатель 21 кодов. Помехоустойчивый цифровой фазометр обеспечивает получение одиночных и усредненных оценок фазового сдвига сигналов независимо от последовательности их переходов через нулевые значения из-за воздействия поjMex, что обеспечивает проведения из;мерений фазовых сдвигов сигналов в присутствии шумов, в частности узкополосных случайных сигналов, при относительно небольших аппаратурных затратах. Формула изобретения 1. Помехоустойчивый цифровой фа- . зометр, содержащий первый и второй дискриминаторы полярности, генератор опорных импульсов, первый и второй элементы совпадения, триггер, блок усреднения и блок регистрации, входы которого соединены с выходами блока усреднения, отличающийся тем, что, с целью повышения точности и быстродействия, он снабжен умножителем частоты, делителем частоты, формирователем, первым и вторым счетт чиком, регистром сдвига, первым и вторым элементом ИСКЛЮЧАЮЩЕЕ ИЛИ, причем первые входы первого и второго -элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соедиН; ны с выходом пврвого дискриминатора полярности, второй вход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с выходом второго дискриминатора полярности и информационным входом регистра сдвига, выход которого аоединен с вторым входом второго элемента ИСКЛЮЧАКЩЕЕ ИЛИ, выходы первого и второго элементов ИСКЛЮЧАКЯДЕЕ ИЛИ соединены с первыми,входами соответствен но первого и второго элементов совпадения, вторые входы которых соединены с тактовым входом регистра сдвига, выходом умножителя частоты и входом делителя частоты, выход которого соединен с входом формирователя управляющим входом умножителя частоты и тактовым входом блока усреднения информационные входы которого соеди иены с выходами первого счетчика, счетный вход которого соединен с вы2СОДОМ первого элемента совпадения, знаковый вход блока усреднения соединен с выходом триггера, информационнь вход которого соединен с выходом переноса второго счетчика, счетный вход которого соединен с выходом второго элемента совпадения, выход формирователя соединен с входами сброса первого и второго счетчиков, триггера и управляющим входом блока усреднения, выход генератора опорных импульсов соединен с тактовым входом умножителя частоты. 2. Фазометр по п.1, о т л.и ч.а ющ и с я тем, что умножитель частотысодержит .разностный счетчик тающий счетчик с регулиремым коэффици ентом, пересчета, управляющие входы которого соединены с выходами разностного счетчика, входы вычитания и суммирования которого являются соответственно информационным и управляю щим входами умножителя частоты, выход которого является выходом вычитающего счетчика с регулируемым коэффициентом пересчета, тактовый вход которого является тактовым входом умножителя частоты. 3. Фазометр по.п.1, о т л и ч аю щ и и с я тем, что блок усреднения содержит комбинационный сумматор, регистр, сдвигатель кодов и вспомогательный делитель, выход которого является управляющим выходом блока усреднения, который соединен с входом сброса регистра, информационные входы которого соединены с выходами комбинационного сумматора, знаковый вход и первая группа входов которого являются соответственно знаковым и информационньлм входами блока усреднения, тактовый вход которого является тактовым входом регистра, управляющий вход блока усреднения является счетным входом вспомогательного делителя, выходы регистра соединены с второй группой входов комбинированного сумматора и входами сдвигателя кодов, выходы которого являются выходами блока усреднения. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 421947, кл. d 01R 25/00, 1972. 2,Контрольно-измерительная техника. Львов,Вйща школа, 1976, . с. 116-121.

| название | год | авторы | номер документа |

|---|---|---|---|

| Радиоимпульсный фазометр | 1985 |

|

SU1257558A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| Цифровой корреляционный фазометр | 1980 |

|

SU943598A1 |

| Цифровой частотный дискриминатор | 1982 |

|

SU1131036A1 |

| Цифровой фазометр | 1986 |

|

SU1368807A1 |

| Устройство тактовой синхронизации | 1981 |

|

SU970717A1 |

| Цифровой фазометр | 1982 |

|

SU1092430A1 |

| Цифровой фазометр | 1977 |

|

SU705371A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Цифровой фазометр | 1980 |

|

SU935821A1 |

Авторы

Даты

1983-03-07—Публикация

1979-06-15—Подача