Изобретение относится к измерительной технике и предназначено для устройств контроля и управления радиоэлектронной аппаратуры путем изменения фазы Сигнала.

Известен дискретный фазовращатель (цифровой фазовращатель), содержащий счетчик, выходы которого подключены к первым входам блока сравнения, вторые входы которого соединены с выходами фазовращаквдего блока и триггер с раздельным управлением. В этом фазовращателе минимальный дискрет изменения Фазы составляет величину 360/2 , однако .с уменьшением дискрета изменения фазы в 2 раз во столько же раз увеличивается период выходного сигнала 1.

Таким образом, увеличение периода выходного сигнала в К раз при уменьшении дискрета, изменения фазы в К раз является недостатком указанного устройства.

Наиболее близким по технической сущности к предлагаемому является устройство для цифрового формирования фазового сдвига, содержащее заданхцйй генератор, два делителя частоты, управляе1 1ый по частоте генера- .

тор, фильтр низких частот, фазовый дискриминатор, два устройства сравненил кодов и два устройства установки числа, причем два входа Фазового дискриминатора подключены к выходам первого и второго делителей частоты соответственно, а его выход соединен с входом фильтра низких частот, выход которого подключен к

10 управлякяцему входу управляемого по частоте генератора, а выход послед- него соединен с входом второго делителя частоты, причем выходы каждого разряда делителей частоты и выходы

15 устройств установки числа подключены к входам устройств сравнения кО. дов, вход первого делителя частоты подключен к выходу задающего генератора 12 .

20

Недостатком этого устройства является увеличение периода выходного сигнала в К раз при уменьшении в К раз минимального дискрета изменения фазы.

25

Цель изобретения - увеличение быстродействия посредством сокращения минимального фазового сдвига без увеличения периода выходного сигнала.

Поставленная цель достигается

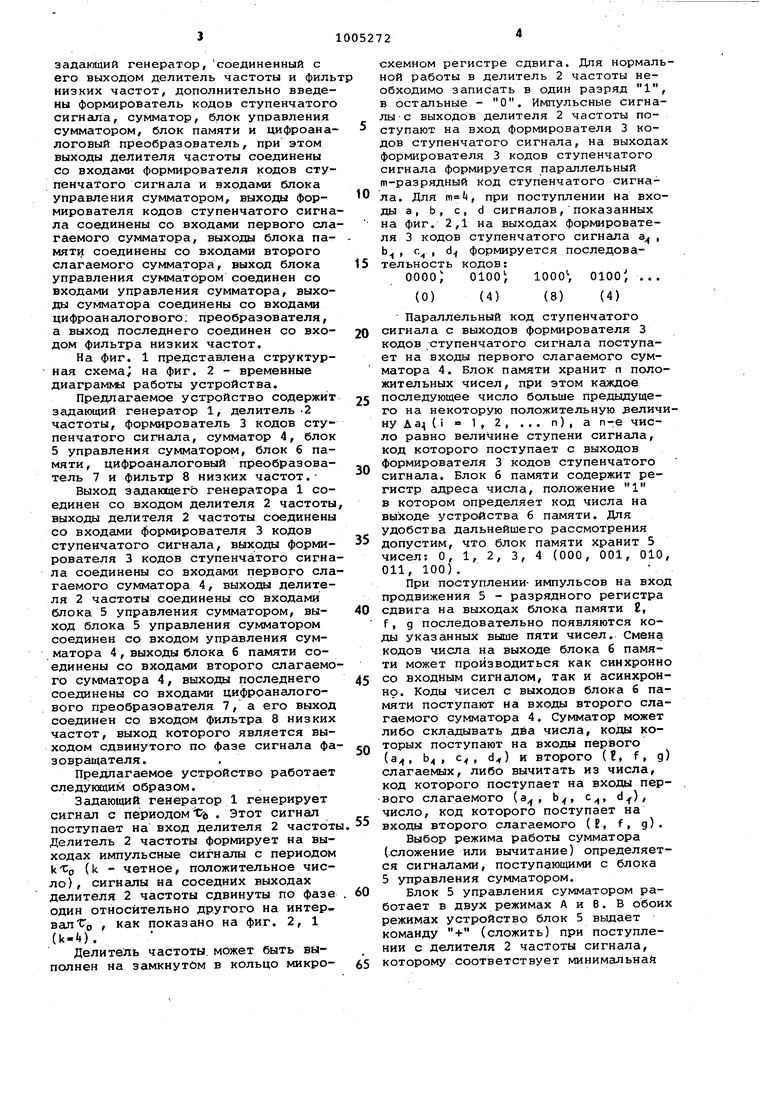

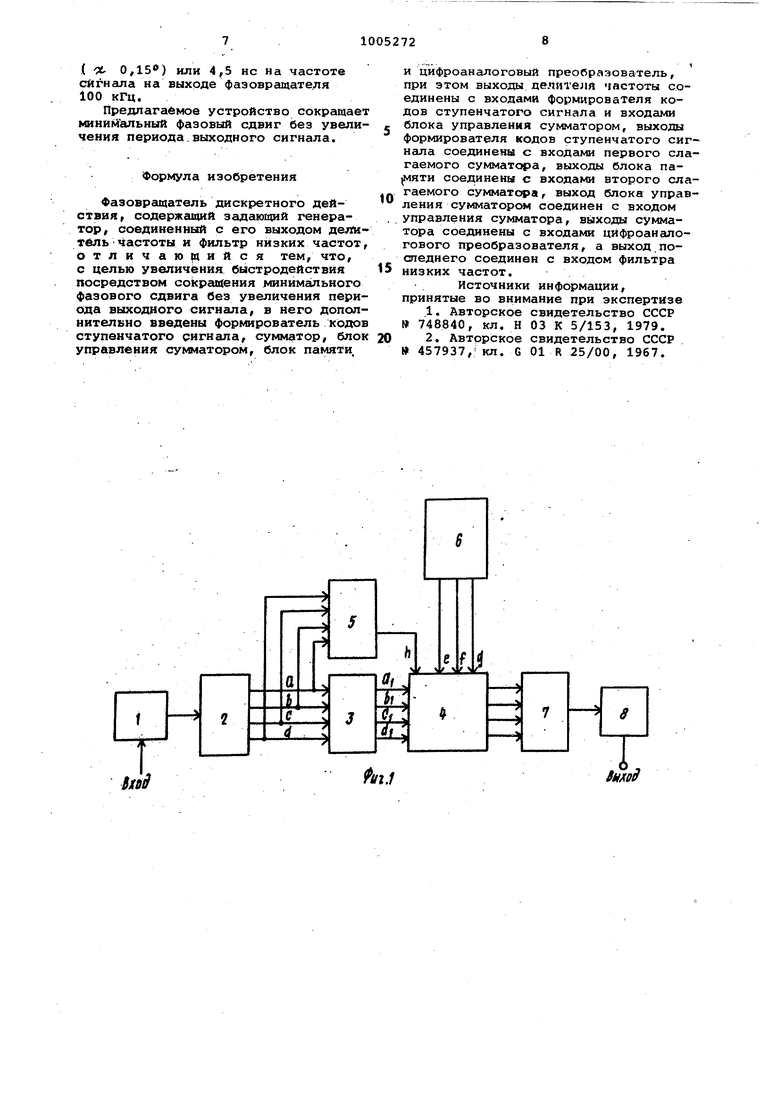

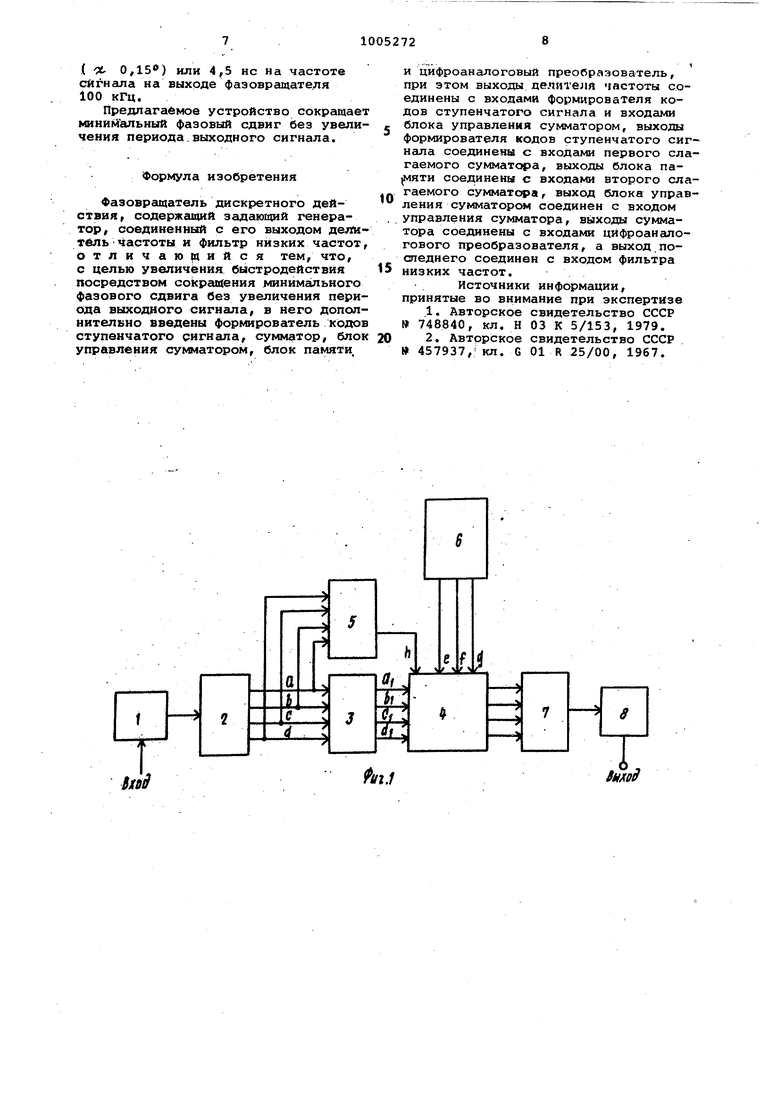

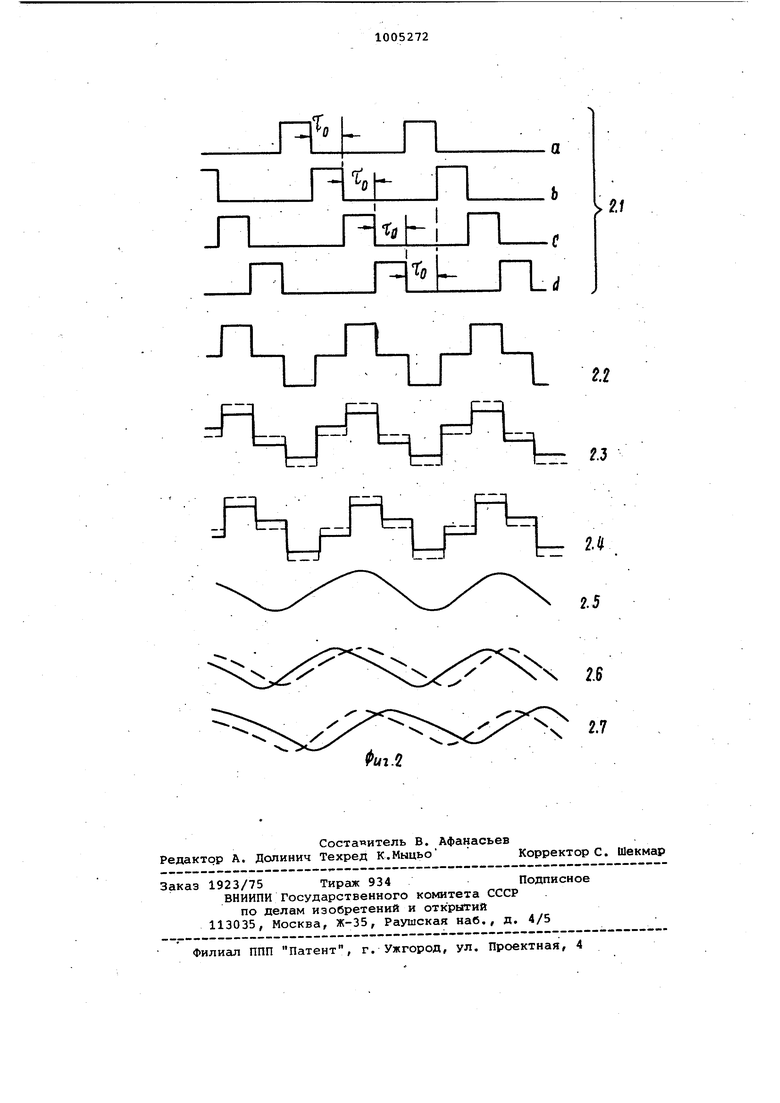

30 тем, что в формирователь, cojciepmafflHA задающий генератор, -соединенный с его выходом делитель частоты и филь низких частот, дополнительно введены формирователь кодов ступенчатого сигнала, сумматор, блок управления сумматором, блок памяти и цифроана логовый преобразователь, при этом выходы делителя частоты соединены со входами формирователя кодов ступенчатого сигнала и входами блока управления сумматором, выходы формирователя кодов ступенчатого сигна ла соединены со входами первого сла гаемого сумматора, выходы блока памяти соединены со входами второго слагаемого сумматора, выход блока управления сумматором соединен со входами управления сумматора, выходы сумматора соединены со входами цифроаналогового: преобразователя, а выход последнего соединен со входом фильтра низких частот. На фиг. 1 представлена структурная схема на фиг. 2 - временные диаграмг ы работы устройства. Предлагаемое устройство содержит задающий генератор 1, делитель -2 частоты, формирователь 3 кодов ступенчатого сигнала, сумматор 4, блок 5 управления сумматором, блок 6 памяти , цифроаналоговый преобразователь 7 и фильтр 8 низких частот. Выход задающего генератора 1 соединен со входом делителя 2 частоты выходы делителя 2 частоты соединены со входами формирователя 3 кодов ступенчатого сигнала, выходы формирователя 3 кодов ступенча того сигна ла соединены со входами первого сла гаемого сумматора 4, выходы делителя 2 частоты соединены со входами блока 5 управления сумматором, выход блока 5 управления сумматором соединен со входом управления сумматора 4 , выходы блока б памяти соединены со входами второго слагаемо го сумматора 4, выходы последнего соединены со входами цифроанапогового преобразователя 7, а его выход соединен со входом фильтра 8 низких частот, выход которого является выходом сдвинутого по фазе сигнала фа зовращателя. Предлагаемое устройство работает следуквдим образом. Задающий генератор 1 генерирует сигнал с периодом tj, . этот сигнал поступает на вход делителя 2 частоты Делитель 2 частоты формирует на выходах импульсные сигналы с периодом kCp (k - четное, положительное число) , сигналы на соседних выходах делителя 2 частоты сдвинуты по фазе один относительно другого на интервал Т , как показано на фиг. 2, 1 (k.M. Делитель частоты, может быть выполнен на замкнутом в кольцо микросхемном регистре сдвига. Для нормальной работы в делитель 2 частоты необходимо записать в один разряд 1, в остальные - О. Импульсные сигналы с выходов делителя 2 частоты поступают на вход формирователя 3 кодов ступенчатого сигнала, на выходах формирователя 3 кодов ступенчатого сигнала формируется параллельный т-разрядный код ступенчатого сигнала. Для , при поступлении на входы а, Ь, с, d сигналов,показанных на фиг. 2,1 на выходах формирователя 3 кодов ступенчатого сигнала а , Ь ч I d формируется последовательность кодов: ООСО; 0100 1000-, 0100, ... (0) (4) (8) (4) Параллельный код ступенчатого сигнала с выходов формирователя 3 кодов ступенчатого сигнала поступает на входы первого слагаемого сумматора 4. Блок памяти хранит п положительных чисел, при этом каждое последующее число больше предыдущего на некоторую положительную зеличину Ла (i 1 , 2, ... п), а п-е число равно величине ступени сигнала, код которого поступает с выходов формирователя 3 кодов ступенчатого сигнала. Блок 6 памяти содержит регистр адреса числа, положение 1 в котором определяет код числа на выходе устройства 6 памяти. Для удобства дальнейшего рассмотрения допустим, что блок памяти хранит 5 чисел: О, 1, 2, 3, 4 (000, 001, 010, 011, 100). При поступлении- импульсов на вход продвижения 5 - разрядного регистра сдвига на выходах блока памяти , f, g последовательно появляются коды указанных выше пяти чисел,. Смена кодов числа на выходе блока б памяти может производиться как синхронно со входным сигналом, так и асинхронно. Коды чисел с выходов блока б памяти поступают на входы второго слагаемого сумматора 4. Сумматор может либо складывать два числа, коды которых поступают на входы первого (а, Ь, с, d) и второго (t, f, g) слагаемых, либо вычитать из числа, код которого поступает на входы первого слагаемого (а, Ь, с, d), число, код которого поступает на входы второго слагаемого (Е, f, g). Выбор режима работы сумматора (.сложение или вьлчитание) определяется сигналами, поступающими с блока 5 управления сумматором. Блок 5 управления сумматором работает в двух режимах А и В. В обоих режимах устройство блок 5 выдает команду + (сложить) при поступлении с делителя 2 частоты сигнала, которому соответствует 1иинимальнай

величина ступени ступенчатого сигнала.

В обоих режимах блок 5 управления вьщает команду - (вычесть) при поступлении с делителя 2 частоты сигнала, которому соответствует максимальная величина ступени.

В режиме А блок управления 5 выдает команду + на возрастающем участке ступенчатого сигнала и команду на убывающем участке ступенjiaToro сигнала.

В режиме В блок 5 управления выдаёт команду -. на врэрастающем участке ступенчатого сигнала и команду + - на убывающем участке ступенчатого сигнала.

В данном случае предполагается, что блок управления сумматором получает сигнал от делителя частоты, выполненного в виде 4-раэрядного регистра сдвига, замкнутого в кольцо.

В рассматриваемом варианте при последовательном поступлении 1 на входы а, Ь, с, d (фиг. 2.1) блок 5 управления сумматором выдает на сумматор в режиме А последовательность команд: +, +, -, а в резкиме +, -, -, .

Команда + соответствует 1 на выходе h, команда - соответствует О на выходе h.

Режим А или В определяется положением триггера. Установка режима А производится подачей О на вход А, режима В - подачей О на вход В

Если от блока 6 памяти на вход второго слагаемого сумматора 4 поступает код числа О (000), то независимо от режима (А или В) имеет место нулевой фазовый сдвиг сигналана выходе устройства относительно входного сигнала. Если от блока памяти на вход второго слагаемого сумматора 4 поступает любое из чисел, хранящихся в памяти, кроме нуля, то режим А соответствует сдвигу выход-: со% Ь- cos-Tf-j

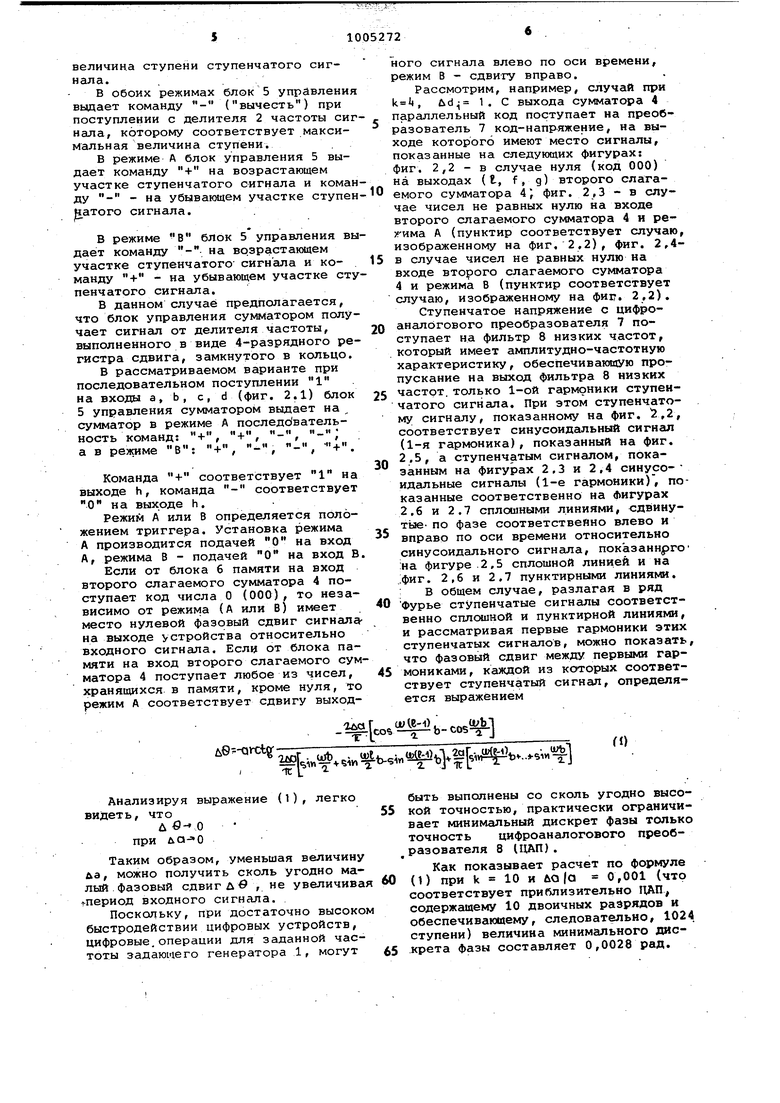

S--arelg i«f......V,«i|.

Анализируя выражение (1), легко видеть, что

Л 0- О при

Таким образом, уменьшая величину &а, можно получить сколь угодно малый . фазовый сдвигдв , не увеличивая ..период входного сигнала.

Поскольку, при достаточно высоком быстродействии цифровых устройств, цифровые,операции для заданной частоты задающего генератора 1, могут

ного сигнала влево по оси времени, режим В - сдвигу вправо.

Рассмотрим, например, случай при , ud 1. с выхода сумматора 4 параллельный код поступает на преобразователь 7 код-напряжение, на выходе которого имеют место сигналы, показанные на следующих фигурах: фиг. 2,2 - в случае нуля (код 000) на выходах (t, f, g) второго слатаемого сумматора 4, фиг. 2,3 - в случае чисел не равных нулю на входе второго слагаемого сумматора 4 и регима А (пунктир соответствует случаю, изображенному на фиг. 2,2), фиг. 2,4в случае чисел не равных нулю на входе второго слагаемого сумматора 4 и режима В (пунктир соответствует случаю, изобргокенному на фиг, 2,2), Ступенчатое напряжение с цифроаналогового преобразователя 7 поступает на фильтр 8 низких частот, который имеет амплитудно-частотную характеристику, обеспечивающую пропускание на выход фильтра 8 низких

частот, только 1-ой гармоники ступенчатого сигнала. При этом ступенчатому, сигналу, показанному на фиг. 5,2, соответствует синусоидгшьный сигнал (1-я гармоника), показанный на фиг.

2,5, а ступенчатым сигналом, показанным на фигурах 2,3 и 2,4 синусо- идальные сигналы (1-е гармоники), показанные соответственно на Фигурах 2.6 и 2.7 сплошными линиями, сдвинутые- по фазе соответственно влево и

вправо по оси времени относительно синусоидального сигнсша, показаннрго :на фигуре .2,5 сплошной линией и на ;фиг. 2,6 и 2,7 пунктирными линиями. В общем случае, разлагая в ряд

Фурье ступенчатые сигналы соответственно сплошной и пунктирной линиями, и рассматривая первые гармоники этих ступенчатых сигналов, можно показать, что фазовый сдвиг между первыми гарМониками, каждой из которых соответствует ступенчатый сигнал, определяется выражением

1лаГ . ).

П)

быть выполнены со сколь угодно высокой точностью, практически ограничивает минимальный дискрет фазы только точность цифроаналогового преобразователя В 1ЦАП).

Как показывает расчет по формуле (1) при k 10 и ло(а 0,001 (что соответствует приблизительно ЦАП, содержащему 10 двоичных разрядов и обеспечиваюшему, следовательно, 1024. ступени) величина минимального дискрета фазы составляет 0,0028 рад.

( -pi- 0,15) или 4,5 НС на частоте сигнала на выходе фазовращателя 100 кГц,

Предлагаемое устройство сокращает минимальный фазовый сдвиг без увеличения периода.выходного сигнала.

Формула изобретения

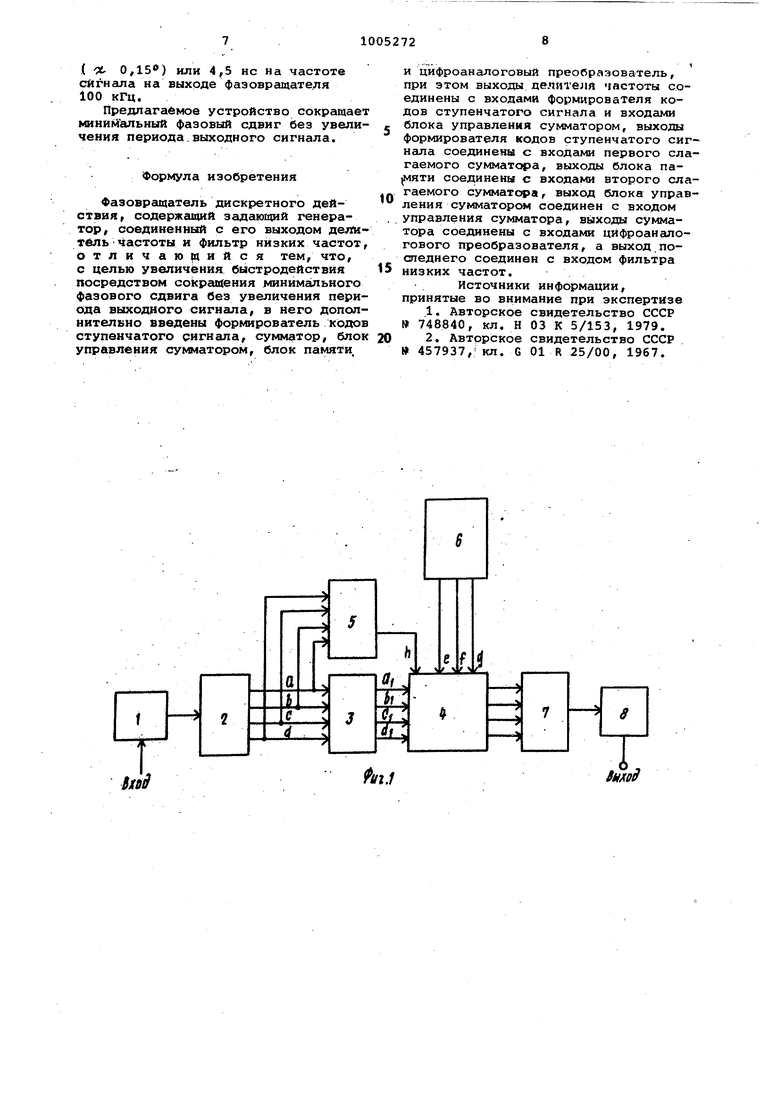

Фазовращатель дискретного действия, содержащий задающий генератор, соединенный с его выходом делитель частоты и фильтр низких частот, отличаю|цийся тем, что, с целью увеличения быстродействия посредством cokpaII(eния минимального фазового сдвига без увеличения периода выходного сигнала, в него дополнителБНо введены формирователь кодов ступенчатого сигнала, сумматор, блок управления сумматором, блок памяти.

и цифроаналоговый преобразователь, при этом выходы делителя частоты соединены с входами формирователя кодов ступенчатого сигнала и входами блока управления сумматором, выходы формирователя кодов ступенчатого сигнала соединены с входами первого слагаемого сумматора, выходы блока па|Мяти соединены с входами второго слагаемого сумматора, выход блока управления сумматором соединен с входом управления сумматора, выходы сумматора соединены с входами цйфроаналогового преобразователя, а выход последнего соединен с входом фильтра низких частот.

Источники информации, принятые во внимание при экспертизе

,1. Авторское свидетельство СССР № 748840, кл, Н 03 К 5/153, 1979.

2, Авторское свидетельство СССР 457937, кл. G 01 R 25/00, 1967.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фазовращатель | 1986 |

|

SU1372593A1 |

| Дискретный фазовращатель | 1985 |

|

SU1338005A1 |

| Имитатор радиосигналов | 1989 |

|

SU1702328A1 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| Широкодиапазонный калибратор фазовых сдвигов | 1987 |

|

SU1525614A1 |

| СПОСОБ ГЕНЕРАЦИИ DTMF СИГНАЛОВ И ГЕНЕРАТОР DTMF СИГНАЛОВ | 2002 |

|

RU2226314C1 |

| ЦИФРОВОЙ МНОГОФАЗНЫЙ ГЕНЕРАТОР | 1992 |

|

RU2066918C1 |

| ЦИФРОВОЙ ФОРМИРОВАТЕЛЬ ЧЕТЫРЕХФАЗНОГО ГАРМОНИЧЕСКОГО КОЛЕБАНИЯ | 2001 |

|

RU2212092C2 |

| ГЕНЕРАТОР ПАРНЫХ СИГНАЛОВ ПРОИЗВОЛЬНОЙ ФОРМЫ | 2022 |

|

RU2795263C1 |

| Регулируемая мера фазовых сдвигов | 1986 |

|

SU1352401A2 |

Авторы

Даты

1983-03-15—Публикация

1981-07-27—Подача