щий вход которого соединен с информационным входом первого элемента запрета, с выходом знакового разряда счетчика и с информационным входом третьего элемента запрета, выходы первого и второго элементов запрета подключены ко входам элемента ИЛИ, выход которого подключен к информа цнонному входу четвертого элемента запрета и к первому входу элемента И, выходы которых подключены соответственно к суммирующему и вычитающему входам счетчика, управляющий вход третьего элемг-нта запрета подключен к шине синхронизации устройства, а выход - ко входу знакового разряда сумматора, который является также знаковым входом устройства, управляющим входом четвертого элемента запрета и вторым входом элемента И.

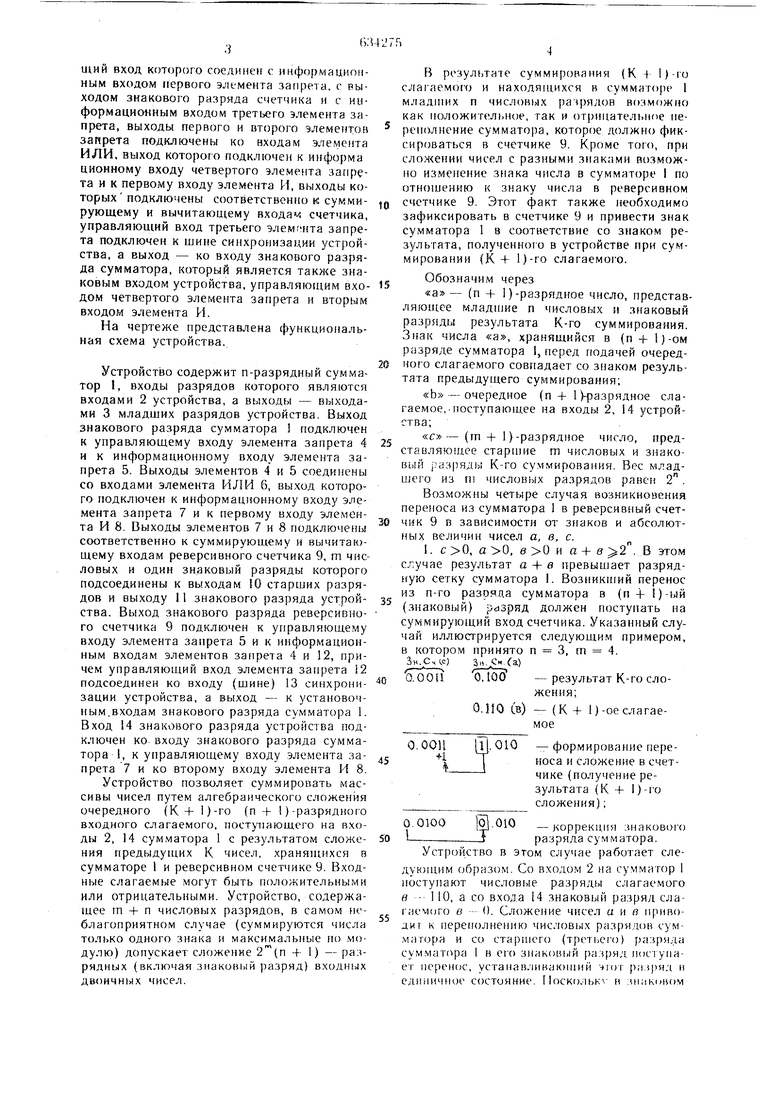

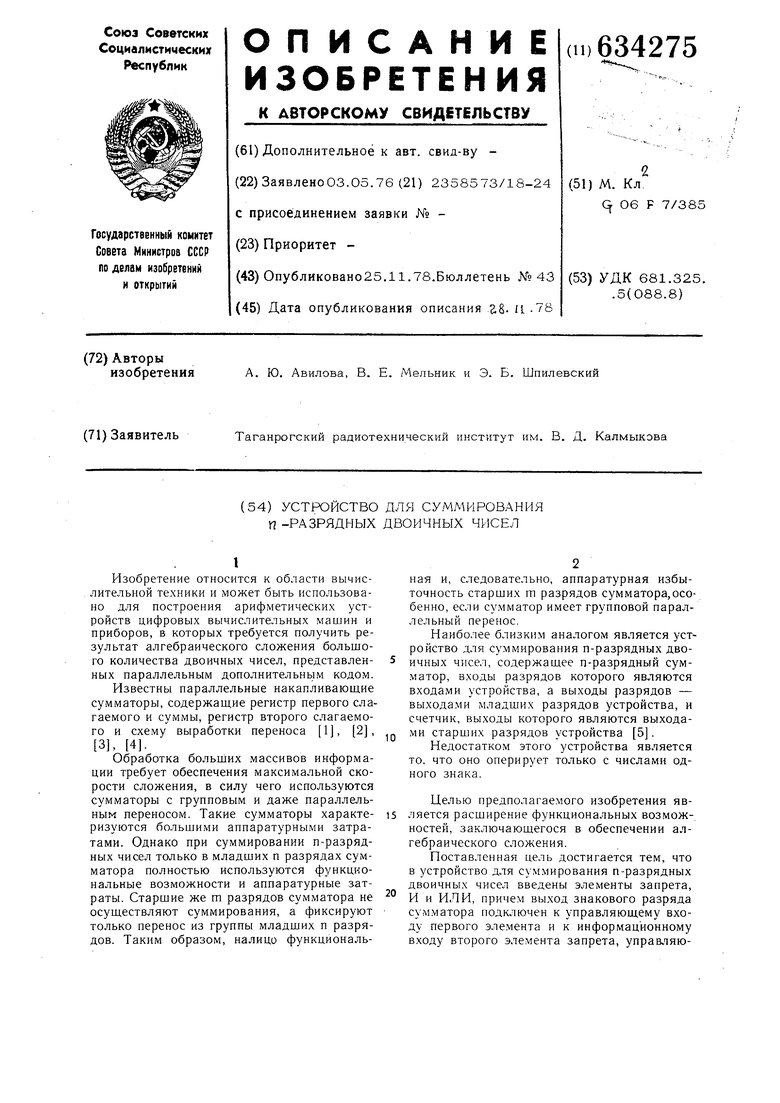

На чертеже представлена функциональная схема устройства.

Устройство содержит п-разрядный сумматор 1, входы разрядов которого являются входами 2 устройства, а ВЫХОДЕ - выходами 3 младших разрядов устройства. Выход знакового разряда сумматора 1 подключен к управляющему входу элемента запрета 4 и к информационному входу элемента запрета 5. Выходы элементов 4 и 5 соединены со входами элемента ИЛИ б, выход которого подключен к информационному входу элемента запрета 7 и к первому входу элемента И 8. Выходы элементов 7 и 8 подключены соответственно к суммирующему и вычитающему входам реверсивного счетчика 9, m числовых и один знаковый разряды которого подсоединены к выходам 0 старших разрядов и выходу 11 знакового разряда устройства. Выход знакового разряда реверсивного счетчика 9 подключен к управляющему входу элемента запрета 5 и к информационным входам элементов запрета 4 и 12, причем управляющий вход элемента запрета 12 подсоединен ко входу (щине) 13 синхронизации устройства, а выход - к установочным.входам знакового разряда сумматора 1. Вход 14 знакового разряда устройства подключен ко входу знакового разряда сумматора , к управляющему входу элемента запрета 7 и ко второму входу элемента И 8.

Устройство позволяет суммировать массивы чисел путем алгебраического сложения очередного (К + 1)-го (п + )-разрядного входного с,тагаемого, постут ающего на входы 2, 14 сумматора 1 с результатом сложения предыдущих К чисел, хранящихся в сумматоре 1 и реверсивном счетчике 9. Входные слагаемые могут быть положительными или отрицательными. Устройство, содержащее гп + л числовых разрядов, в самом неблагоприятном случае (суммируются числа только одного знака и максимальные но модулю) допускает сложение 2(п -f- 1) - разрядных (включая знаковый разряд) входных двоичных чисел.

в результате суммирования (К f 1)-го слагаемого и находящихся в сумматоре 1 младших п числовых разрядов возможно как положительное, так и отринател1 ное переполнение сумматора, которое должно фиксир(;ваться в счетчике 9. Кроме того, при чисел с разными знаками возмож ш изменение знака числа в сумматоре I по отнощению к знаку числа в реверсивном счетчике 9. Этот факт также необходимо зафиксировать в счетчике 9 и привести знак сумматора 1 в соответствие со знаком результата, полученного в устройстве при суммировании (К 4 1)-го слагаемого.

Обозначим через

«а - (п + 1)-разрядное число, представляющее младн ие п числовых и знаковый разряды результата К-го суммирования. Знак числа «а, хранящийся в (п -|- 1)-ом разряде сумматора 1, перед нодачей очередного слагаемого совпадает со знаком результата предыдущего суммирования;

«Ь - очередное (п + 1)-разрядное слагаемое,-поступающее на входы 2, 14 устройства;

(т + 1)-разрядное число, представляющее старшие m числовых и знаковый )яды К-го суммирования. Вес ылзлQiero из П1 числовых разрядов равен 2 .

Возможны четыре случая возникновения переноса из сумматора i в реверсивный счетчик 9 в зависимости от знаков и абсолютных величин чисел а, в, с.

1. с 0, а 0, 0 0 и а -f 0 2. В этом с..пучае результат а -f в превышает разрядную сетку сумматора 1. Возникпгий перенос из п-го разряда сумматора в (п + 1)-ый (знаковый) разряд должен поступать па суммирующий вход счетчика. Указанный случай иллюстрируется следующим примером, в котором принято п 3, m 4. Зн.) Зн.Си.а)

0,100 - результат К-го сложения;

О.ЛО (в) - (К 4- 1)-ое слагаемое

0.0011 UJ.010

- формирование пере iIноса и сложение в счетчике (получение результата (К + 1)-го сложения);

о .010

0.0100

-коррекция знакового разряда сумматора. Устройство в этом случае работает следующим образом. Со входом 2 на сумматор 1 поступают числовые разряды слагаемого я - 1 10, а со входа 14 знаковый разряд слагаемого в - (}. Сложение чисел айв приводит к переполнению числовых разрядов сумматора и со старшего (TpcTi ero) сумматора I в его знаковый ра.чряд поступает перенос, устанап.1ивак)Н1ий чгиг ри.ряд о еди||ичное состояние. . Ft знаковом разряде счртчика 9, хранящего число С 0,0011, имеется «О, то срабатывает злемент 5, единичный сигнал с выхода которого через элемент ИЛИ 6 поступает на входы элементов 7 и 8. В силу того, что на входе 14 в этот момент имеется «О (знак числа б), то срабатывает элемент 7, который выдает «I на суммирующий вход счетчика 9. В результате число С увеличивается на единицу, и становится равным 0,0100. По окончании импульса, поступающего на вход (шину) 13 синхронизирующего работу сумматора и счетчика, срабатывает элемент 12, выходной сигнал которого переключает знаковый разряд сумматора 1 из «1 в «О, что соответствует состоянию з)1акового разряда устройства. Устройство готово к приему очередного слагаемого. 2. с 0, а О, в О, (а + 0) 2 Отрицательный результат а + переполняет разрядную сетку сумматора I. Возникщий перенос из п-го разряда должен поступать на вычитающий вход счетчика. Следует отметить, что отрицательные числа в устройстве представляются и обрабатываются в дополнительном коде. Пример. -- результат К-го сложения;-(К -f 1)-ое слагаемое -формирование переноса и вычитание в.счетчике (получение результата (К + 1)-го сложения); -коррекция знакового разряда сумматора Рассмотренный выше при.мер соответствует следующему сложению чисел в прямых кодах. -ООП НЮ -прямой код результата К-го сложения; -0000 ПО- (К + 1)-ое слагае-0100 010 -прямой код результата (К + 1)-го сложения. Преобразуя дополнительный код на выходах 3, 10, II устройства в прямой, получаем, что результат (К + 1)-го сложения равен - 0.0100010, т.е. совпадает с результатом сложения отрицательных чисел в прямых кодах. Устройство в этом случае работает следующим образом. Слолчение дополнительных кодов отрицательных чисел а и s приводит к переполнению числовых разрядов сумматора 1 и перенос со старшего числового разряда переключает знаковый разряд сумматора «I и «О. Посксхпьку в знаковом разряде счетчика 9, xpaiinniero число ( 1.1100, находится «I, то срабатыгзает элемент 4, оигна.ч с выхода которою через элом.чп ИЛИ Г) ii()(-iyn;u4 lui вх(.ды 7 и 8. В СИЛУ ил.шчии на к.ходс 1-1 единицы (знак числа и) срабатывает элемент 8, который выдает « на вычитающий вход счетчика 9. В результате дополнительный код отрицательного числа С уменьшается на единицу (соответствует увеличению прямого кода отрицательного числа на «1) и становится равным 1.1011. По окончании синхронизирующего импульса срабатывает элемент J2, выходной сигнал которого переключает знаковый ртзряд сумматора 1 в соответствии с состоянием знакового разряда счетчика 9, т.е. - из «О в «1. Устройство готово к приему очередного слагаемого. 3. с 0, а 0, в О, /а/ - /в/. При сло)кев1ии чисел а и я в сум.маторе 1 возникает отрицательный результат, в то время как в старших m разрядах хранится положительное число С. В математическом плане в этом случае число С, в младших разрядах которого иаходятся нули, необходимо сложить с дополнительным кодом отрицательной разности а-а, в старших m разрядах которого будут единицы. Но поскольку в предлагаемом устройстве для старших m разрядов применяется счетчик, а не сумматор, то выполнить указанную операцию невозможно. Однако, если в этом случае сформировать перенос на вычитающий вход счетчика 9, а зате.м выполнить коррекцию в сумматоре 1. го получится праБИЛьныГ« результат сложепия. Пример.- результат К-го ело0.0011 0.100жения; - (К + 1)-ое слагаемое; 0.0011 Щ.110- формирование переноса и вычитание в счетчике (получение результата (К + i)-го сложения); 0.0010 Ш1.110 -:- коррекция знака I сум.матора. Расс 1Отрен П)1Й пример соответствует следующей операции над числами в прямых кодах. + 0011 100- прямой код результата К-го сложения; -- 0000 110-- прямой код (К + I) го слагаемого; -f 0010 110- прямой код результата (К + I )-го сложения. Полученный результат сложения чисел с разными знаками (фактически вычитание из большего по модулю положительного числа меньшего по модулю отрицательного числа) совпадает с результатом (К + 1)-го в предлагао.мо.м устройстве. Устройство в рассматриваемом случае работает следующим образом. (Сложение чисе.1 а 0 и 0 О, при /о/ /rt/, приводит к появлению единицы Ei знаковом кчзряде сумматора I Поскольку в знаковим разряде счсгчика 9з гранящего число С -- (IDdll. находится «О, то cp;i6;n ьпиим члемснг ,), CMI нал с выхода которого через элемент 6 поступает на входы элементов 7 и 8. В силу наличия на входе 14 единицы (знак отрицательного числа в), срабатывает элемент 8, который выдает «1 на вычитающий вход счетчика 9. В результате положительное число С уменьшается на единицу и становится равным 0.0010. По окончании на выходе 13 синхронизирующего импульса срабатывает элемент 12, выходной сигнал которого переключает знаковый разряд сумматора 1 в соответствии с состоянием знакового разряда счетчика 9, т.е. - из «О в «l.v. Устройство готово к приему очередного слагаемого. 4. с 0, , б О, . При сложении чисел Q и 0 в сумматоре 1 возникает положительный результат, в то время как в старших ш разрядах (в счетчике 9) хранится отрицательное число С.- Этот случай симметричный предыдущему, о чем свидетельствует следующий при.мер. Пример. -результат К-го сло1.1100 ..1.100 жения; 0.100 -(К + 1)-оеслагаемое;1.1100 ШЮ -формирование переноса и.сложение в.счетчике (получение результата (К + 1)-го сложения) ; -коррекция знака I1 , сумматора. Рассмотренный пример соответствует следующей операции над числами в прямых кодах. - ООП 100 -прямой код результата К-го сложения; -прямой код (К + 1) + 0000 110 го слагаемого; - 0010 1.10 -7 прямой код результата (К + 1)-го сложения. Преобразуя дополнительный код на выходах 3, 10, 11 устройства в прямой, находим, что результат (К + 1)-го сложения равен -0010 1.10, т. е. совпадает с результатом операции кад числами в прямых кодах. Устройство в этом случае работает еледующим образом. Сложение чисел , в О, при /а/ /в/, приводит к появлению нуля в знаковом разряде сумматора 1. Поскольку в знаковом разряде счетчика 9, хранящего число С 1.1100, имеется «1, то срабатывает элемент 4, сигнал с выхода которого через элемент 6 поступает на входы элементов 7 и 8. Вследствие наличия на входе 14 нуля (знака положительного числа в) срабатывает элемент 7, который выдает «1 на суммирующий вход счетчика 9. В результате дополнительный код числа С увеличивается на единицу (соответствует уменьщению прямого кода отрицательного числа на «1) и становится равным 1.1101. По окончании синхронизирующего импульса на входе 13 срабатывает элемент 12, выходной сигнал которого по установочным входам переключает знаковый разряд сумматора 1 в соответствии с состоянием знакового разряда счетчика 9, т. е, - из «О в «1. Устройство готово к приему очередного слагаемого. В остальных случаях, когда состояние знакового разряда сумматора 1 после подачи (К -+- 1)-го слагаемого совпадает с состоянием знакового разряда результата К-го сложения (знакового разряда счетчика 9), переполнение сумматора 1, а также изменение знака его содержимого не происходит. При этом элементы 4 и 5 не срабатывают, в силу чего остаются закрытыми и элементы 7 и 8 независимо от сигнала, поступающего со входа 14. Старщие m разрядов результата, хранящиеся в реверсивном счетчике 9, не изменяются. Формирование результата (суммирование) осуществляется в пределах разрядной сетки сумматора 1. В заключение следует отметить высокую эффективность применения предлагаемого устройства при выполнении суммирования большого количества чисел, разрядность которых в несколько раз меньше разрядности получаемого результата. Было разработано предлагаемое устройство для суммирования 256 5-разрядных (включая знаковый) двоичных чисел (, т-8). Для построения этого устройства потребовалось 32 микросхемы серии 133. Если же для аналогичных це.1ей использовать 13-разрядный (с учетом знакового разряда) параллельный сумматор, то его реализация потребует 63 микросхемы серии 133, т.е. почти в два раза больше. Экономия аппаратурных затрат еще более заметна при увеличении количества суммируемых чисел. Так при построении предлагаемого устройства для суммирования Ю 5-разрядных чисел требуется 53 микросхемы серии 133, в то время как при построении параллельного сумматора для суммирования такого же количества чисел требуется 125 микросхем той же серии. Формула изобретения Устройство для суммирования п-разрядных двоичных чисел, содержащее п-разрядный сумматор, входы разрядов которого подключены ко входам устройства, а выходы разрядов - к выходам младших разрядов устройства, и счетчик, выходы которого подключены к выходам старших разрядов устройства, отличающееся тем, что, с целью расширения функциональных возможностей устройства, заключающегося в обеспечении алгебраического сложения, в него введены элементы запрета, И и ИЛИ, причем выход знакового разряда сумматора подключен к управляющему входу первого элемента запрета и к информационному входу второго элемента запрета, управляющий вход которого соединен с информационным входом первого элемента запрета, с выходом знакового разряда счетчика и с информационным входом третьего элемента запрета, выходы первого и второго элементов запрета подключены ко входам элемента ИЛИ, выход которого подключен к информационному входу четвертого элемента запрета и к первому входу элемента И, выходы которых подключены соответственно к суммирующему и вычитающему входам счетчика, управляющий вход третьего элемента запрета подключен к шине синхронизации устройства, а выход - ко входу знакового разряда сумматора, который соединен также со знаковым входом устройства, управляющим входом четвертого элемента запрета и вторым входом элемента И.

Источники информации, принятые во внимание iijii экспертизе:

1.Фи.шппов А. Г. и Белкин О. С. Проектирование логических узлов ЭВМ-М., «Советское радио, 1973, с. 263.

2.Авторское свидетельство СССР До 315179, кл. G 06 F //50, 1970.

3.Авторское свидетельство СССР ..9 351214, кл. G 06 F 7/50, 1970.

4.Шалагинов Ю. В. Быстродействующий сумматор накапливающего типа - «Автометрия, 6, 1973.

5.Макаревич О. Б. и Суркова Л. М. Устройство ввода исходной информации в цифровую .интегрируюпгую машину - Известия ВУЗов, «Электромеханика, № 10, 1969. с. 1070.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для суммирования двоичных чисел | 1983 |

|

SU1103223A2 |

| Устройство для суммирования чисел | 1984 |

|

SU1183959A1 |

| Устройство для суммирования двоичных чисел | 1983 |

|

SU1087987A1 |

| Устройство для суммирования двоичных чисел | 1982 |

|

SU1022153A1 |

| Устройство для сложения чисел | 1982 |

|

SU1035599A1 |

| Устройство для суммирования двоичных чисел | 1984 |

|

SU1198511A1 |

| Устройство для суммирования двоичных чисел | 1988 |

|

SU1578709A2 |

| Устройство для сложения чисел | 1984 |

|

SU1218383A1 |

| Устройство для суммирования Фибоначчи-десятичных кодов | 1989 |

|

SU1649535A1 |

| Устройство для алгебраического накопительного суммирования | 1988 |

|

SU1550511A1 |

1

Авторы

Даты

1978-11-25—Публикация

1976-05-03—Подача