Изобретение относится к вычисли- гельной технике и может быть использовано в арифметических устройствах ЭВМ.

Целью изобретения является повышение быстродействия и расширение ункциональных возможностей за счет - осуществления сложения чисел как в обратном, так и в дополнительном кодах,

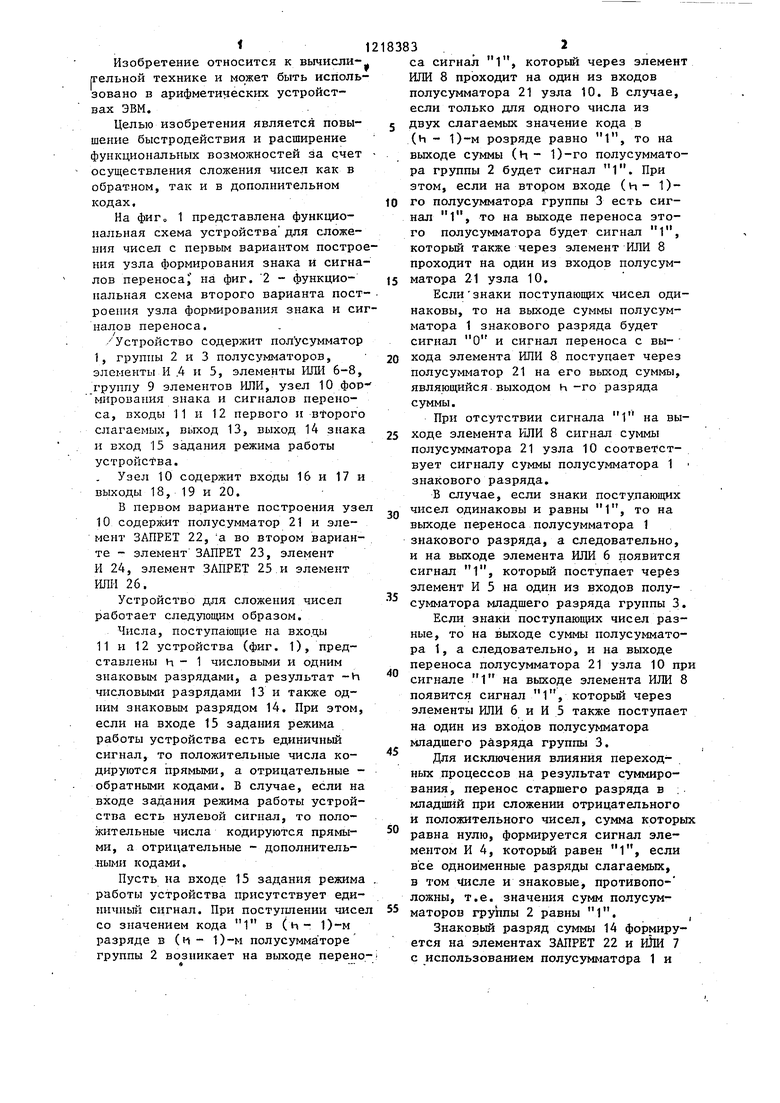

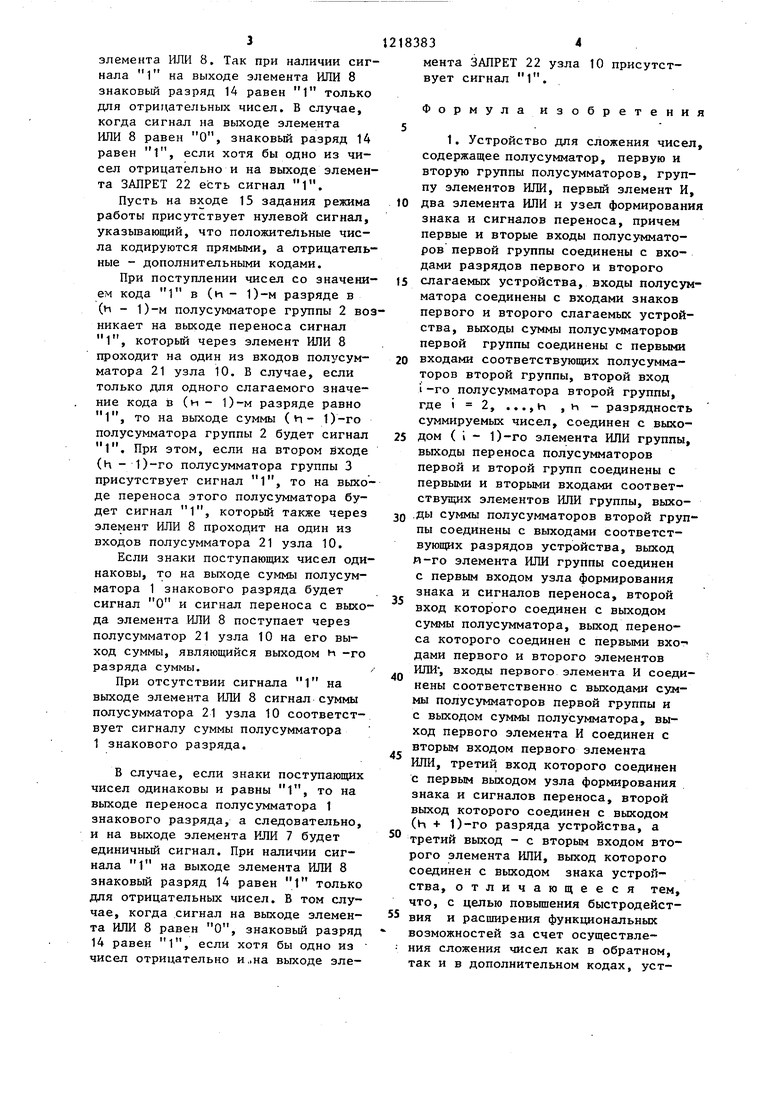

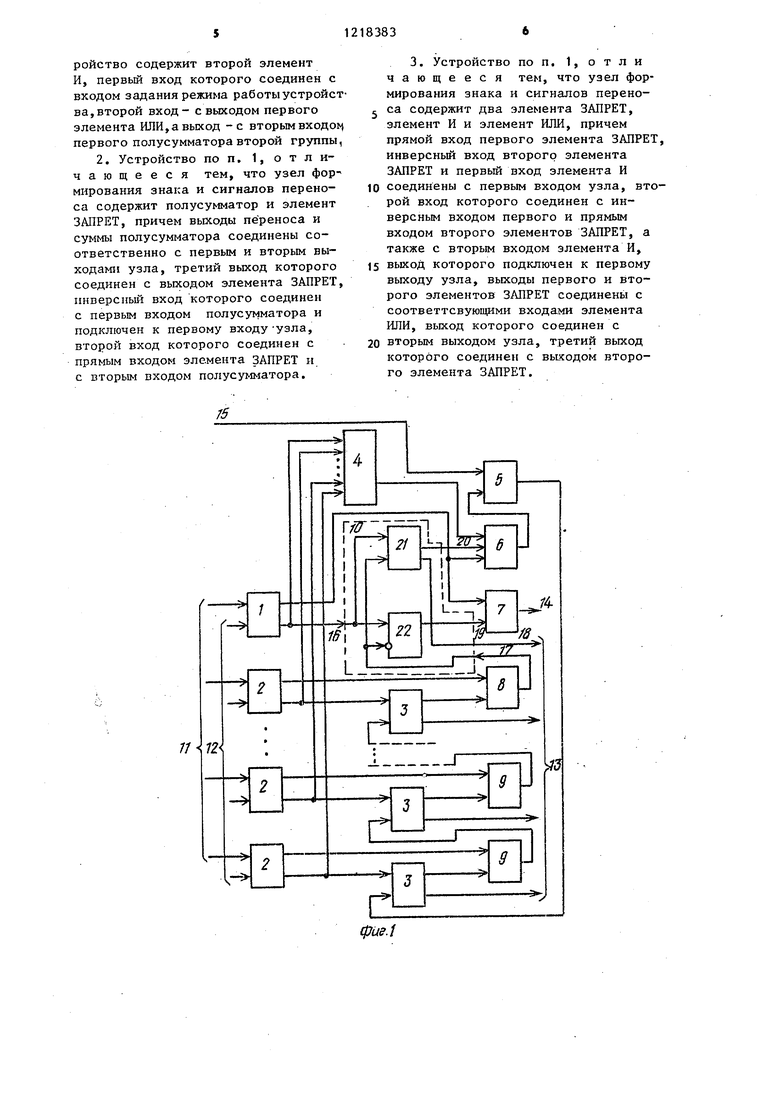

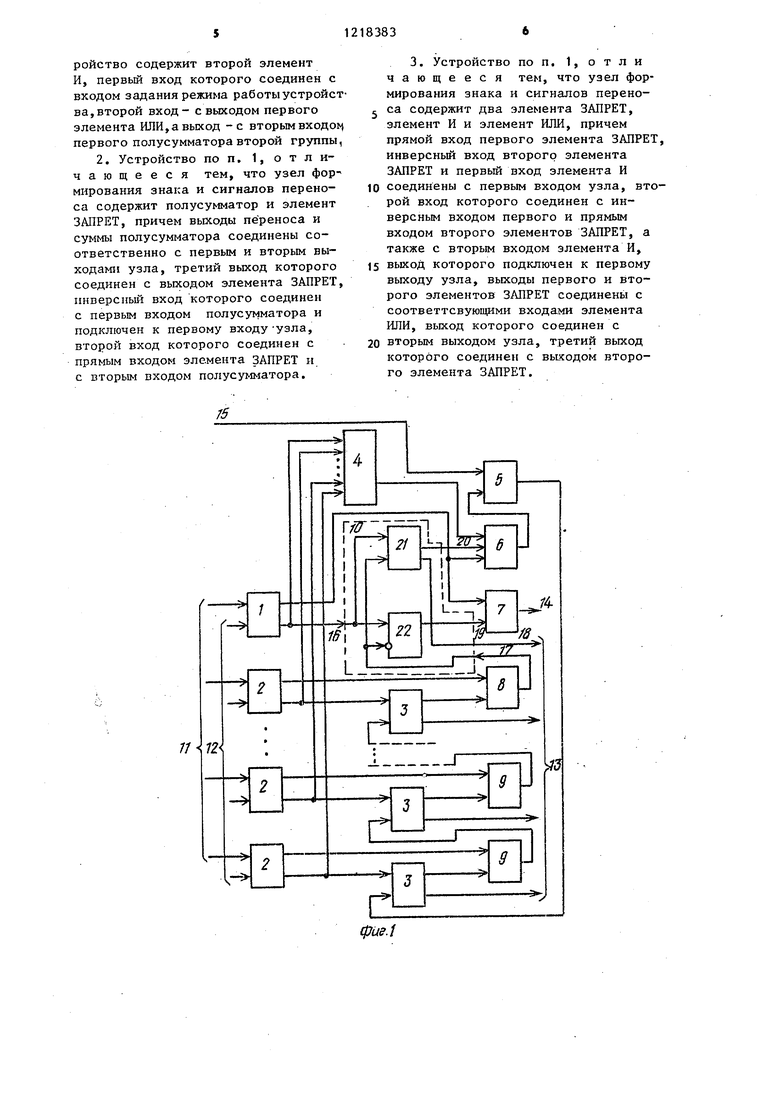

На фиго 1 представлена функциональная схема устройства для сложения чисел с первым вариантом построения узла формирования знака и сигналов переносаJ на фиг. 2 - функциональная схема второго варианта пост- . роения узла формирования знака и сигналов переноса.

/Устройство содержит полусумматор 1, группы 2 и 3 полусумматоров, элементы И .4 и 5, элементы ИЛИ 6-8, группу 9 элементов ИЛИ, узел 10 фор мирования знака и сигналов переноса, входы 11 и 12 первого и второго слагаемых, выход 13, выход 14 знака и вход 15 задания режима работы устройства.

Узел 10 содержит входы 16 и 17 и выходы 18, 19 и 20.

В первом варианте построения узел

10содержит полусумматор 21 и элемент ЗАПРЕТ 22, а во втором варианте - элемент ЗАПРЕТ 23, элемент

И 24, элемент ЗАПРЕТ 25 и элемент ИЛИ 26.

Устройство для сложения чисел работает следующим образом.

Числа, поступашцге на входы

11и 12 устройства (фиг. 1), представлены и - 1 числовыми и одним знаковым разрядами, а результат -h числовыми разрядами 13 и также одним знаковьм разрядом 14. При этом, если на входе 15 задания режима работы устройства есть единичньй сигнал, то положительные числа кодируются прямыми, а отрицательные - обратными кодами. В случае, если на входе задания режима работы устройства есть нулевой сигнал, то поло- Ж11тельные числа кодируются прямыми, а отрицательные дополнительными кодами.

Пусть на входе 15 задания режима . работы устройства присутствует единичньй сигнал. При поступлении чисел со значением кода 1 в (и- 1)-м разряде в (и- 1)-м полусумма торе группы 2 возникает на выходе перено-i

218383

-

.

. i

са сигнал 1, которьй через элемент ШШ 8 проходит на один из входов полусумматора 21 узла 10. В случае, если только дпя одного числа из

5 двух слагаемьк значение кода в

(h - 1)-м розряде равно 1, то на выходе суммы (h- 1)-го полусумматора группы 2 будет сигнал 1. При этом, если на втором входе (и- 1)10 го полусумматора группы 3 есть сигнал 1, то на выходе переноса этого полусумматора будет сигнал 1, который также через элемент ИЛИ 8 проходит на один из входов полусумJ5 матора 21 узла 10.

Если знаки поступающих чисел одинаковы, то на выходе суммы полусумматора 1 знакового разряда будет сигнал О и сигнал переноса с вы-

20 хода элемента ИЛИ 8 поступает через полусумматор 21 на его выход суммы, являющийся выходом h -го разряда суммы.

При отсутствии сигнала 1 на вы25 ходе элемента ИЛИ 8 сигнал суммы полусумматора 21 узла 10 соответствует сигналу суммы полусумматора 1 знакового разряда.

В случае, если знаки поступающих

I111I

30

35

40

45

50

55

чисел одинаковы и равны 1, то на выходе переноса полусумматора 1 знакового разряда, а следовательно, и на выходе элемента ШШ 6 появится сигнал 1, который поступает через элемент И 5 на один из входов полусумматора младшего разряда группы 3.

Если знаки поступающих чисел разные, то на выходе суммы полусумматора 1 , а следовательно, и на выходе переноса полусумматора 21 узла 10 при сигнале 1 на выходе элемента ИЛИ 8 появится сигнал 1, которьш через элементы ИЛИ 6 и И 5 также поступает на один из входов полусумматора младшего разряда группы 3.

Для исключения влияния переходных процессов на результат суммирования, перенос старшего разряда в ; младший при сложении отрицательного и положительного чисел, сумма которых равна нулю, формируется сигнал элементом И 4, который равен 1, если все одноименные разряды слагаемых, в том числе и знаковые, противопо- ложны, т.е. значения сумм полусумматоров группы 2 равны 1.

Знаковый разряд суммы 14 формируется на элементах ЗАПРЕТ 22 и ИЛИ 7 с использованием полусзт матора 1 и

элемента ИЛИ 8, Так при наличии сигнала 1 на выходе элемента ИЛИ 8 знаковый разряд 14 равен 1 только для отрицательных чисел, В случае, когда сигнал на выходе элемента ИЛИ 8 равен О, знаковьй разряд 14 равен 1, если хотя бы одно из чисел отрицательно и на выходе элемента ЗАПРЕТ 22 есть сигнал 1.

Пусть на входе 15 задания режима работы присутствует нулевой сигнал, указывающий, что положительные числа кодируются прямыми, а отрицательные - дополнительными кодами.

При поступлении чисел со значением кода 1 в (и - 1)-м разряде в (и - 1)-м полусумматоре группы 2 воникает на выходе переноса сигнал 1, который через элемент ИЛИ 8 проходит на один из входов пол гсум- матора 21 узла 10. В случае, если только для одного слагаемого значение кода 1в (и - 1)-м разряде равно 1, то на выходе суммы (h- 1)-го полусумматора группы 2 будет сигнал 1. При этом, если на втором входе (h - 1)-го полусумматора группы 3 присутствует сигнал 1, то на выходе переноса этого полусумматора будет сигнал 1, который также через элемент ИЛИ 8 проходит на один из входов полусумматора 21 узла 10.

Если знаки поступающих чисел одинаковы, то на выходе суммы полусумматора 1 знакового разряда будет сигнал О и сигнал переноса с выхода элемента ИЛИ 8 поступает через полусумматор 21 узла 10 на его выход суммы, являющийся выходом н -го разряда суммы.

При отсутствии сигнала 1 на выходе элемента ИЛИ 8 сигнал суммы полусумматора 21 узла 10 соответствует сигналу суммы полусумматора 1 знакового разряда.

В случае, если знаки поступающих чисел одинаковы и равны 1, то на выходе переноса полусумматора 1 знакового разряда, а следовательно, и на выходе элемента ИЛИ 7 будет единичный сигнал. При наличии сигнала 1 на выходе элемента ИЛИ 8 знаковый разряд 14 равен 1 только для отрицательных чисел. В том случае, когда сигнал на выходе элемента ИЛИ 8 равен О, знаковый разряд 14 равен 1, если хотя бы одно из чисел отрицательно и„на выходе эле-

мента ЗАПРЕТ 22 узла 10 присутствует сигнал 1.

s

0

5

0

5

0

5

0

Формулаизобретения

1. Устройство для сложения чисел, содержащее полусумматор, первую и вторую группы полусумматоров, группу элементов ИЛИ, первый элемент И, два элемента ИЛИ и узел формирования знака и сигналов переноса, причем первые и вторые входы полусумматоров первой группы соединены с входами разрядов первого и второго слагаемых устройства, входы полусумматора соединены с входами знаков первого и второго слагаемых устройства, выходы суммы полусумматоров первой группы соединены с первыми входами соответствующих полусумматоров второй группы, второй вход i-го полусумматора второй группы, где , ...,h ,b - разрядность суммируемых чисел, соединен с выходом ( I - 1)-го элемента ИЛИ группы, выходы переноса полусумматоров первой и второй групп соединены с первыми и вторыми входами соответ- ствупщх элементов ИЛИ группы, выхо- .ды суммы полусумматоров второй группы соединены с выходами соответствующих разрядов устройства, выход и-го элемента ИЛИ группы соединен с первым входом узла формирования знака и сигналов переноса, второй вход которого соединен с выходом суммы полусумматора, выход переноса которого соединен с первыми вхо- дами первого и второго элементов ИЛИ , входы первого элемента И соединены соответственно с выходами суммы полусумматоров первой группы и с выходом суммы полусумматора, выход первого элемента И соединен с вторым входом первого элемента ИЛИ, третий вход которого соединен с первым выходом узла формирования знака и сигналов переноса, второй выход которого соединен с выходом (и + 1)-го разряда устройства, а третий выход - с вторым входом второго элемента ИЛИ, выход которого соединен с выходом знака устройства, отличающееся тем, что, с целью повьшения быстродействия и расширения функциональных возможностей за счет осуществления сложения чисел как в обратном, так и в дополнительном кодах, устройство содержит второй элемент И, первый вход которого соединен с входом задания режима работы устройства,второй вход- с выходом первого элемента ИЛИ,а выход -с вторьмвходоь) первого полусумматора второй группы,

2. Устройство по п. 1, отличающееся тем, что узел фор- мирования знака и сигналов переноса содержит полусумматор и элемент ЗАПРЕТ, причем выходы переноса и суммы полусумматора соединены соответственно с первым и вторым выходами узла, третий выход которого соединен с выходом элемента ЗАПРЕТ, инверсный вход которого соединен с первым входом полусумматора и подключен к первому входу-узла, второй вход которого соединен с прямым входом элемента ЗАПРЕТ и с вторым входом полусумматора.

3, Устройство по п. 1, отли чающееся тем, что узел формирования знака и сигналов перено- J са содержит два элемента ЗАПРЕТ, элемент И и элемент ИЛИ, причем прямой вход первого элемента ЗАПРЕТ инверсный вход второго элемента ЗАПРЕТ и первый вход элемента И

10 соединены с первым входом узла, второй вход которого соединен с инверсным входом первого и прямым входом второго элементов ЗАПРЕТ, а также с вторым входом элемента И,

J5 выход которого подключен к первому выходу узла, выходы первого и второго элементов ЗАПРЕТ соединены с соответтсвующими входами элемента ИЛИ, выход которого соединен с

20 вторым выходом узла, третий выход которого соединен с вькодом второго элемента ЗАПРЕТ.

L

.;I

(ffifff.2

Редактор M.Бандура

Составитель А.Степанов

Техред Т.Дубинчак Корректор М.Максимишинец

Заказ 1132/56 Тираж 673 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сложения чисел | 1982 |

|

SU1035599A1 |

| Устройство для сложения чисел | 1978 |

|

SU788107A1 |

| Устройство для суммирования Фибоначчи-десятичных кодов | 1989 |

|

SU1649535A1 |

| Устройство для суммирования двоичных чисел | 1983 |

|

SU1087987A1 |

| Устройство для суммирования чисел | 1984 |

|

SU1183959A1 |

| Устройство для суммирования п-разрядных двоичных чисел | 1976 |

|

SU634275A1 |

| Устройство для суммирования двоичных чисел | 1983 |

|

SU1103223A2 |

| Устройство для суммирования двоичных чисел | 1984 |

|

SU1198511A1 |

| Устройство для сложения | 1986 |

|

SU1415223A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

Изобретение относится к вычислительной технике и позволяет повысить быстродействие устройства, а также осуществить на одном устройстве сложение чисел в обратном и дополнительном кодах. Указанный эффект достигается введением в известное устройство, содержащее две группы полусумматоров, группу элементов И, элементы И и ИЛИ, а также узел формирования знака и сигнгшов переноса, элемента И, с помощью которого осуществляется управляемая передача сигнала переноса из старшего разряда устройства в его младший разряд. Таким образом осуществляется управление кодом, которым представлены отрицательные числа. Кроме того, устройство содержит узел формирования знака и сигналов переноса измененной конструкции, представленный двумя вариантами построения. В первом варианте этот узел содержит полусумматор и элемент ЗАПРЕТ, что вместе с новьп«ш связями позволяет повысить быстродействие устройства. 2 з.п. ф-лы. 2 ил. S (Л

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сложения чисел | 1982 |

|

SU1035599A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-03-15—Публикация

1984-05-16—Подача