13 L

1UL

&25

-36

23

Utf Mr

AL

f. 201 .1

w

w,, З . i-. -. л .,- X- f.

«3f73|77 |/7 1 1Шф}1В2 1в 1 3529l 28 j 27 j 261

202

Ji

19

33

32

J/

30

ОЭ 4b CO СЛ

со en

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор кодов Фибоначчи | 1987 |

|

SU1411735A1 |

| Устройство для сложения п-разрядных десятичных чисел | 1980 |

|

SU900282A1 |

| Устройство для приведения 1-кода Фибоначчи к минимальной форме | 1989 |

|

SU1665515A1 |

| Конвейерный сумматор | 1983 |

|

SU1137460A1 |

| Комбинационный сумматор | 1985 |

|

SU1310808A1 |

| Конвейерное вычислительное устройство | 1989 |

|

SU1693601A1 |

| Комбинационный сумматор | 1987 |

|

SU1442988A1 |

| Устройство для суммирования фибоначчиево-десятичных кодов | 1981 |

|

SU945862A1 |

| Устройство для умножения двоично-десятичных цифр | 1983 |

|

SU1198513A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1292187A1 |

Изобретение относится к вычислительной технике и может быть использовано в специализированных машинах. 5tA5i35t25t1 Цель изобретения - расширение Лункцио- нальных возможностей путем реализации операции вычитания Фибоначчи-десятичных кодов. Устройство содержит в -каждом разряде с первого по четвертый элементы 17.1-17.4 запрета, с первого по четвертый элементы И 18.1-1 о.4, преобразователь 19 прямого кода в дополнительный код, с первого по третий узлы 20.1-20.3 свертки, с первого по четвертый одноразрядные двоичные сумматоры 2201-22.4, с первого по пятый элементы ИЛИ 23.1-23.5, узел 24 коррекции и узел 25 формирования переносов с соответствующими связями. Осуществляется суммирование или вычитание n-разрядных Фибоначчи-десятичных операндов за два такта без распространения переносов между десятичными разрядами. 3 з.п.ф-лы, 6 ил., 3 та бл. 6i4 6i3 6i2 Bi17 с $ (Л

Jd Idi2 Bi3 8i4

Фиг 2

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных машинах.

Цель изобретения - расширение функциональных возможностей путем реализации операции вычитания Фибоначчи-десятичных кодов.

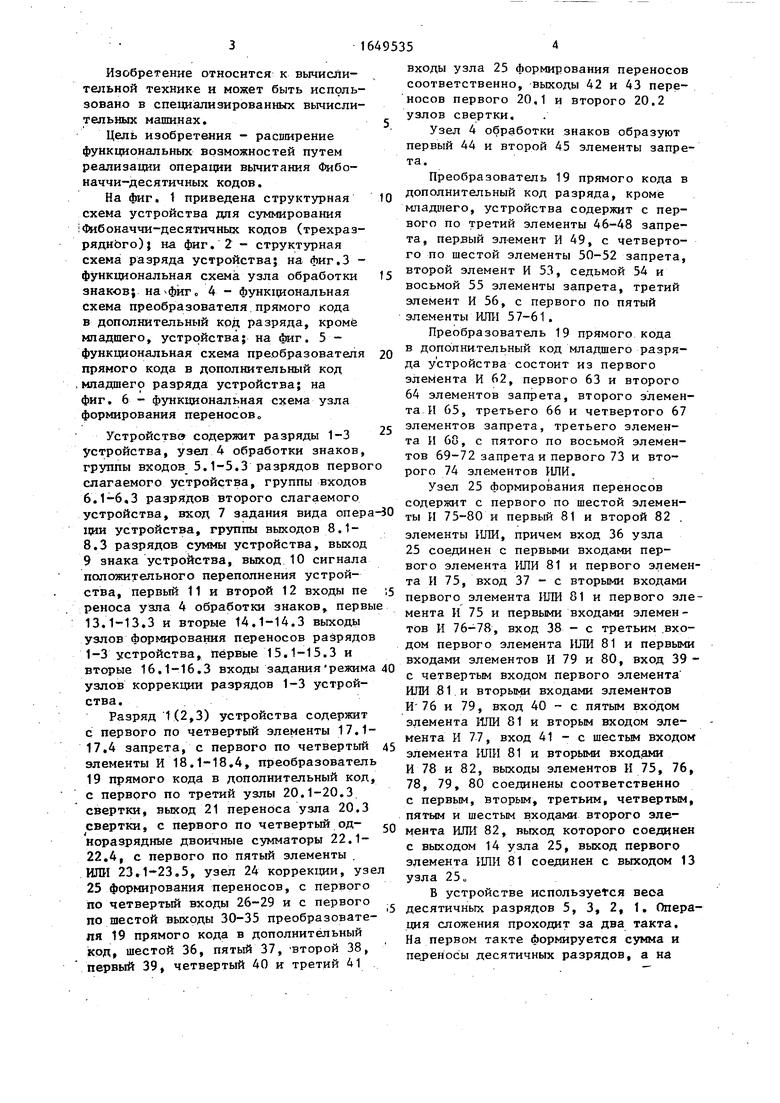

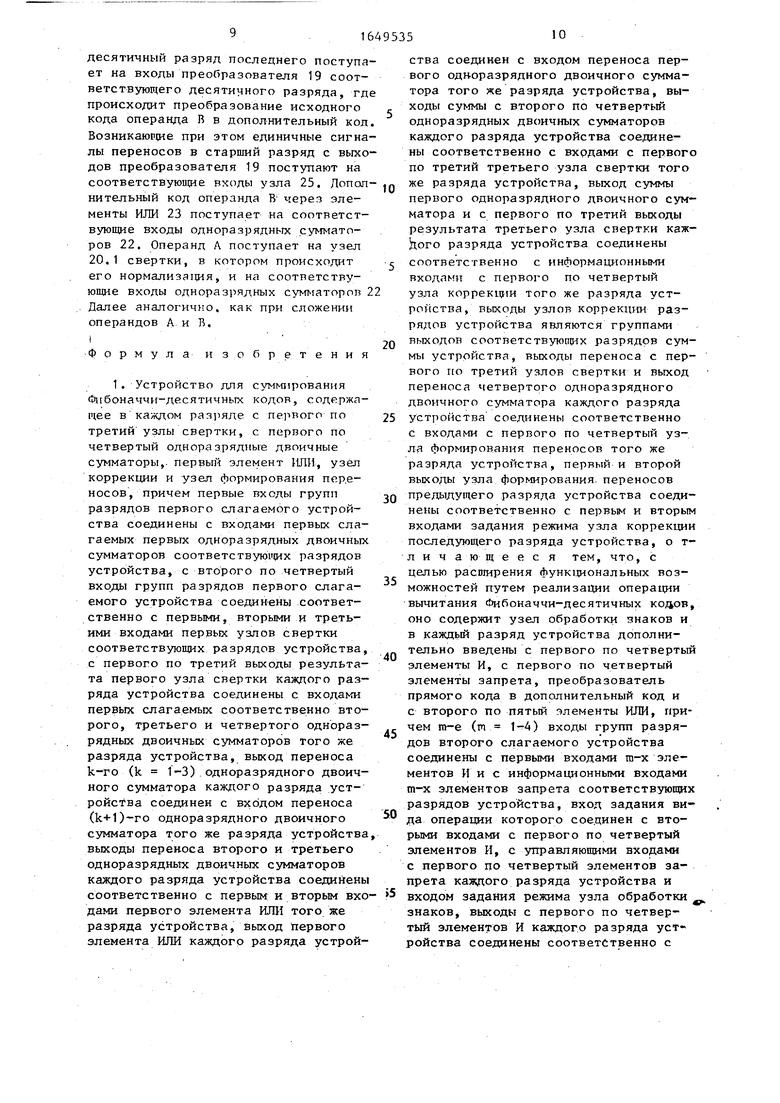

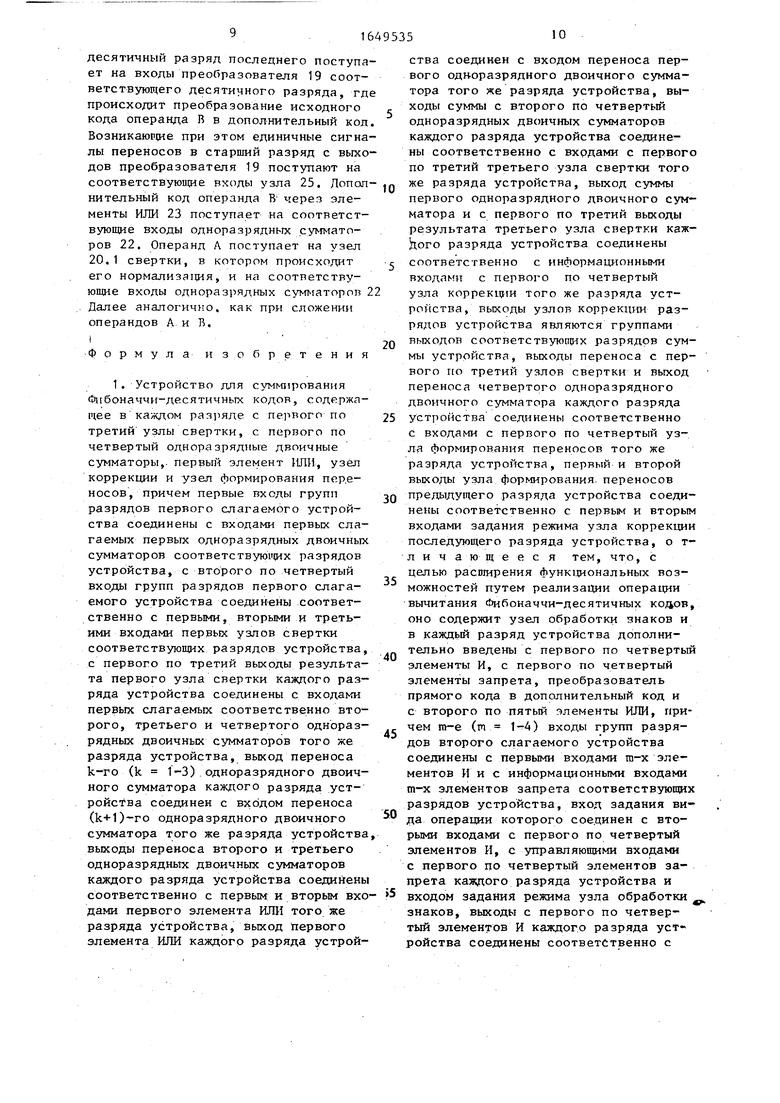

На фиг. 1 приведена структурная схема устройства для суммирования Фибоначчи-десятичных кодов (трехраз- ряднЬго)} на фиг. 2 - структурная схема разряда устройства; на фиг.З - функциональная схема узла обработки знаков; 4 - функциональная схема преобразователя прямого кода в дополнительный код разряда, кроме младшего, устройства; на фиг. 5 - функциональная схема преобразователя прямого кода в дополнительный код младшего разряда устройства; на фиг, 6 - функциональная схема узла формирования переносов

Устройстве содержит разряды 1-3

устройства, узел 4 обработки знаков, группы входов5.1-5.3 разрядов первого слагаемого устройства, группы входов 6.1-6,3 разрядов второго слагаемого устройства, вход 7 задания вида операции устройства, группы выходов 8.1- 8.3 разрядов суммы устройства, выход 9 знака устройства, выход 10 сигнала положительного переполнения устройства, первый 11 и второй 12 входы пе реноса узла 4 обработки знаков, первы 13.1-13.3 и вторые 14.1-14.3 выходы узлов формирования переносов разрядов 1-3 устройства, первые 15.1-15.3 и вторые 16.1-16.3 входы задания режима узлов коррекции разрядов 1-3 устройства.

Разряд 1(2,3) устройства содержит с первого по четвертый элементы 17.1- 17.4 запрета, с первого по четвертый элементы И 18.1-18.4, преобразователь 19 прямого кода в дополнительный код, с первого по третий узлы 20.1-20.3 свертки, выход 21 переноса узла 20.3 свертки, с первого по четвертый од- норазрядные двоичные сумматоры 22.1- 22.4, с первого по пятый элементы ИЛИ 23.1-23.5, узел 24 коррекции, узе 25 формирования переносов, с первого по четвертый входы 26-29 и с первого по шестой выходы 30-35 преобразователя 19 прямого кода в дополнительный код, шестой 36, пятый 37, второй 38, первый 39, четвертый 40 и третий 41

5

0 5 0

5

30 15 40

45 5о

входы узла 25 формирования переносов соответственно, выходы 42 и 43 переносов первого 20,1 и второго 20.2 узлов свертки.

Узел 4 обработки знаков образуют первый 44 и второй 45 элементы запрета.

Преобразователь 19 прямого кода в дополнительный код разряда, кроме младшего, устройства содержит с первого по третий элементы 46-48 запрета, первый элемент И 49, с четвертого по шестой элементы 50-52 запрета, второй элемент И 53, седьмой 54 и восьмой 55 элементы запрета, третий элемент И 56, с первого по пятый элементы ИЛИ 57-61.

Преобразователь 19 прямого кода в дополнительный код младшего разряда устройства состоит из первого элемента И 62, первого 63 и второго 64 элементов запрета, второго элемента И 65, третьего 66 и четвертого 67 элементов запрета, третьего элемента И 60, с пятого по восьмой элементов 69-72 запрета и первого 73 и второго 74 элементов ИЛИ.

Узел 25 формирования переносов содержит с первого по шестой элементы И 75-80 и первый 81 и второй 82 элементы ИЛИ, причем вход 36 узла 25 соединен с первыми входами первого элемента ИЛИ 81 и первого элемента И 75, вход 37 - с вторыми входами первого элемента ИЛИ 81 и первого элемента И 75 и первыми входами элементов И 76-78, вход 38 - с третьим входом первого элемента ИЛИ 81 и первыми входами элементов И 79 и 80, вход 39 - с четвертым входом первого элемента ИЛИ 81 и вторыми входами элементов И 76 и 79, вход 40 - с пятым входом элемента ИЛИ 81 и вторым входом элемента И 77, вход 41 - с шестым входом элемента ИЛИ 81 и вторыми входами И 78 и 82, выходы элементов И 75, 76, 78, 79, 80 соединены соответственно с первым, вторым, третьим, четвертым, пятым и шестым входами второго элемента ИЛИ 82, выход которого соединен с выходом 14 узла 25, выход первого элемента ИЛИ 81 соединен с выходом 13 узла 25„

Б устройстве используется веса десятичных разрядов 5, 3, 2, 1. Операция сложения проходит за два такта. На первом такте формируется сумма и переносы десятичных разрядов, а на

втором такте - гашение переносов простым прибавлением их к значениям соответствующих сумм разрядов. При этом предусмотрен отказ от нормализованной формы представления десятичных чисел и допускается значение десятичного разряда 10 или 11. Алгоритм сложения полностью идентичен алгоритму сложения, реализованно му в прототипе,

Операцию вычитания из операнда А операнда Б можно снести к сложению, преобразовав код операнда В в дополнительный код, как код отрицательног числа. Если код операнда В имеет п десятичных разрядов (с 0-го по (п-1)-й то n-й десятичный разряд рассматривается как знаковый.

Положительные числа представляют- ся в виде:

иИ

0 10П + В 0-10 + МП1 ,

. UO

где В« 0,11 - значение 1-го десяти ного разряда числа В.

Дополнительный код числа есть дополнение модуля отрицательного числа до некоторого граничного значения превосходящего максимально возможный модуль. При этом надо учитывать необходимость размещения отрицательных чисел на положительном участке числовой оси для обеспечения возможности выполнения вычислений на сумматоре.

Максимально возможный модуль п-

/В/ . 10

+ 2-ZV

+ 10

Поэтому граничным числом может быть число 2 10 , но при этом возможно попадание отрицательных чисел в дополнительном коде в область положительных чисел. Во избежание этого за граничное число принимается величина, равная 3 ЧОИ.

Отрицательные числа в дополнительном коде представляются в виде:

ми

3-Ю - В ЫОП + (2-10И -2Х--Ю1)

т.е. знаковому разряду числа предварительно присваивается значение 1, а дополнительный код значащей части числа получается дополнением до 2-10й, т.е дополнительный код 1-го десятичного разряда отрицательного числа получается следующим образом;

Эоп пр d- 20 - d- при 1 0;

df°; 18 - + при i 1,2.... где d. - значение 1-го десятичного

т разряда прямого кода числа; оап d- - значение 1-го десятичного

разряда дополнительного

«

-

0

5

0

5

кода числа; P. перенос из (i-1)-ro разряда.

После приведения дополнительного кода числа к нормализованному виду значение в знаковом разряде равно 2. После преобразования операнда В далее производится сложение кодов известным способом, указанным выше.

Узел 4 обработки знаков предназначен дпя формирования знака результата и сигнала положительного переполнения в зависимости от производимой в устройстве операции и значений сигналов переноса из старшего десятичного разряда устройства. Он реализует

следующие логические функции: сг Р,

С

- ст Р.-О)ЗИ Г 1 ш 1

ппф co-pf,

где C-JH знак результата;

ПП. - сигнал положительного переполнения;

СО 0 - если производится сложение операндов;

- если производится вычитание операндов;

РСТ

М

per ге

- соответственно значения первого и второго переносов из старшей декады в знаковые разряды.

Преобразователь 19 реализует функции ДЛЯ любого 1-го десятичного 0 разряда, кроме младшего, и функции

f -f ri Г6

для младшего десятичного разряда. Функции - значения соответственно с первого по четвертый двоичных разрядов дополнительного кода

5 соответствующего десятичного разряда, f. - f - то же, для младшего десятичного разряда, функции ., Ј4 fg- - перенос в старший разряд (возникают при нормализации дополнительного кода

0 соответственно 1-го,младшего десятичных разрядов). Эти функции заданы в табл. 1.

Узлы 20.1-20.3 свертки предназначе- 5 ны для нормализации десятичного разряда операнда, если его значение больше 9, т.е. 10 или 11.

Фиббоначчи-десятичный сумматор Представляет собой совокупность че-

71

тырех одноразрядных сумматоров 22.1- 22.4, предназначенных для суммирования двух Фибоначчи-десятичных цифр операндов А и В соответственно с весами 5, 3. 2, 1, соединенных между собой цепями переносов на основании правил суммирования, описанных в устройстве для суммирования Фибоначчи-десятичных кодов.

Узел 24 коррекции предназначен для коррекции суммы, прошедшей нормализацию в узле 20.3 свертки с учетом

переносов Р,, и Р из предыдущего десятичного разряда устройства Узел коррекции может быть реализован комбинационным или на основе ПЗУ, что более экономично.

Карта прошивки ПЗУ приведена в табл. 2.

Узел 25 формирования переносов предназначен для формирования переносов Р, и РЈ в последующий разряд устройства в зависимости от поступающих на его входы переносов из преобразователя 19, узлов 20.1-20.3 свертки и сумматора 22.4. Это комбинационный узел, реализующий функции Р и Р, которые задаются следующими логическими выражениями:

л, /ч/ - А Р , Т. + „ + Р, + + Рг + 7,

1

Р«2 Р(

Л,

:

Л, /-Л.

Рг +, Р, Р.

Р Р 1 згб

г. Ч

РЛ

Г

+ Р„Р,

Ггг6

где

Л.

р„

р; р„ перенос из преобразователя 19 младшего разряда устройства;

перенос из преобразователя 19 соответствующего разряда устройства,

перенос из второго узла 20.2 свертки;

перенос из первого узла 20.1 свертки;

перенос из четвертого одноразрядного сумматора 22.4; перенос из третьего узла 20. 3,.свертки.

Несмотря на то, что в формировании переноса в последующий разряд участвуют шесть сигналов переноса из различных узлов соответствующего разряда, величина максимального перено- qa в следующий разряд равна 2Г Наличие одного из шести возможных переносов допускает наличие только еще одного другого переноса, исключая полностью возникновение четырех других переносов.

Р

ЛР,

В табл. 3 показано,, какие из пе

0

5

5

0

5

0

реносов могут возникнуть одновременно.

Устройство работает следующим образом.

Одновременно на входы 5 и 6 устройства поступают коды десятичных разрядов обрабатываемых десятичных чисел А и В На вход 7 устройства поступает нулевой сигнал, если числа А и В надо сложить, и единичный сигнал, если из числа А надо вычесть число В.

При сложении входных десятичных чисел А и В, если любой десятичный разряд любого из чисел А и В имеет значение 10 или 11, то узлы 20.1 и 20.2 свертки соответствующих десятичных разрядов производят нормализацию, в результате чего через выходы 20.1 и 20.2 узлов свертки единичные сигналы переноса поступают на соответствующие входы узла 25. Если произошла нормализация одноименных десятичных разрядов сразу обоих чисел, то появление единичного сигнала с выхода переноса сумматора 22.4 и узла 20.3 свертки соответствующего десяQ тичного разряда исключается. Затем нормализованный операнд А поступает на соответствующие входы одноразрядных сумматоров 22, а нормализованный операнд В через элементы ИЛИ 23 поступает на соответствующие входы одноразрядных сумматоров 22, где происходит первый такт сложения. Если в результате суммирования на сумматоре 22.4 возникает перенос в старший десятичный разряд, то единичный сигнал поступает на соответствующий вход узла 25. В этом случае полученная сумма не нуждается в дальнейшей нормализации. Полученная сумма с выходов сумматоров 22 поступает на соответствующие входы узла 20.3 свертки, где в случае необходимости происходит нормализация результата, в результате чего через выход узла 20.3 свертки единичный сигнал переноса поступает на соответствующий вход узла 25. Затем результат поступает на узел 24 коррекции, где происходит коррекция полученного результата с учетом переносов из младшего разряда,

5 формируемых узлом 25 младшего разряда.

При вычитании из десятичного операнда А десятичного операнда В каждый

десятичный разряд последнего поступает на входы преобразователя 19 соответствующего десятичного разряда, где происходит преобразование исходного кода операнда В в дополнительный код. Возникаклцие при этом единичные сигналы переносов в старший разряд с выходов преобразователя 19 поступают на соответствующие входы узла 25. Допол- нительный код операнда В черет элементы ИЛИ 23 поступает на соответствующие входы одноразрядных сумматоров 22. Операнд Л поступает на узел 20.1 свертки, в котором происходит

его нормализация, и на соответствующие входы одноразрядных сумматороп 22 Далее аналогично, как при сложении операндов А и В.

Формула изобретения

5

0

5 п 0 5

5

ства соединен с входом переноса первого одноразрядного двоичного сумматора того же разряда устройства, выходы суммы с второго по четвертый одноразрядных двоичных сумматоров каждого разряда устройства соединены соответственно с входами с первого по третий третьего узла свертки того же разряда устройства, выход суммы первого одноразрядного двоичного сумматора и с первого по третий выходы результата третьего узла свертки каж- horo разряда устройства соединены соответственно с информационными входами с первого по четвертый узла коррекции того же разряда устройства, выходы узлов коррекции разрядов устройства являются группами выходов соответствующих разрядов суммы устройства, выходы переноса с первого по третий узлов свертки и выход переноса четвертого одноразрядного двоичного сумматора каждого разряда устройства соединены соответственно с входами с первого по четвертый узла формирования переносов того же разряда устройства, первый и второй выходы узла формирования переносов предыдущего разряда устройства соединены соответственно с первым и вторым входами задания режима узла коррекции последующего разряда устройства, о т- личающееся тем, что, с целью расширения функциональных возможностей путем реализации операции вычитания Фибоначчи-десятичных кодов, оно содержит узел обработки знаков и в каждый разряд устройства дополнительно введены с первого по четвертый элементы И, с первого по четвертый элементы запрета, преобразователь прямого кода в дополнительный код и с второго по пятый элементы ИЛИ, причем m-е (т 1-4) входы групп разрядов второго слагаемого устройства соединены с первыми входами га-х элементов И и с информационными входами т-х элементов запрета соответствующих разрядов устройства, вход задания вида операции которого соединен с вторыми входами с первого по четвертый элементов И, с управляющими входами с первого по четвертый элементов запрета каждого разряда устройства и входом задания режима узла обработки в знаков, выходы с первого по четвертый элементов И каждого разряда устройства соединены соответственно с

перв гб по четвертый входами преобразователя прямого кода в дополнительный код того же разряда устройства, с первого по четвертый выходы преобразователя прямого кода в дополнительный код каждого разряда устройства соединены с первыми входами соответственно с второго по пятый элементов ИЛИ того же разряда устройства, пятый выход преобразователя прямого кода в дополнительный код соединен с соответствующим входом узла формирования переносов того же разряда устройства, шестой выход преобразователя прямого кода в дополнительный код младшего разряда устройства соединен с соответствующим входом узла формирования переносов этого же разряда устройства, выход первого элемента запрета каждого разряда устройства соединен с вторым входом второго элемента ИЛИ того же разряда устройства, выходы с второго по четвертый элементов запрета каждого разряда устройства соединены соответственно с первого по третий входами второго узла свертки того же разряда устройства, с первого по третий выходы результата второго узла свертки каждого разряда устройства соединены с вторыми входами соответ- , ственно с третьего по пятый элементов ИЛИ того же разряда устройства, выходы с второго по пятый элементов ИЛИ

нены с входами вторых слагаемых соответственно с первого по четвертый одноразрядных двоичных сумматоров того же разряда устройства, первый и второй выходы узла формирования перекосов старшего разряда устройства соединены соответственно с первым и вторым входами переноса узла обработки знаков, первый выход которого соединен с выходом знака устройства, второй выход узла обработки знаков соединен с выходом сигнала положительного переполнения устройства.

15

20

25

30

входом первого элемента запрета и информационным входом второго элем та запрета, выход которого являетс вторым выходом узла обработки знак второй вход переноса и первый выхо которого соединены соответственно с вторым управляющим входом и выхо дом первого элемента запрета.

элементов И, второй вход преобразо теля прямого кода в дополнительный код соединен с вторым управляющим входом первого элемента запрета, уп равляющим входом второго элемента запрета, информационными входами третьего и пятого элементов запрет первым информационным входом шесто элемента запрета, вторым входом

каждого разряда устройства соеди- первого элемента И и первым входом

40

45

50

второго элемента И, третий вход пр разователя прямого кода в дополнит ный код соединен с вторыми информационными входами второго и шестого элементов запрета, управляющими вхо дами третьего и четвертого элементов запрета, вторым управляющим вхо дом пятого элемента запрета, вторым входами второго и третьего элементов И, первым управляющим входом восьмого элемента запрета, и первым инверсным входом первого элемента ИЛИ, четвертый вход преобразователя прямого кода в дополнительный код соединен с вторыми управляющими вхо дами седьмого и восьмого элементов запрета, третьим входом третьего элемента И и вторым инверсным входо первого элемента ИЛИ, третий вход КОТОРОГО сординен с выходом первого элемента запрета, выход второго эле мента запрета соединен с первыми входами второго и четвертого элемен

чающееся тем, что узел обработки знаков содержит первый и второй элементы запрета, причем вход задания режима узла обработки знаков соединен с информационным входом первого элемента запрета и управляющим входом второго элемента запрета, первый вход переноса узла обработки знаков соединен с первым управляющим

5

0

5

0

входом первого элемента запрета и с информационным входом второго элемента запрета, выход которого является вторым выходом узла обработки знаков, второй вход переноса и первый выход которого соединены соответственно с вторым управляющим входом и выходом первого элемента запрета.

элементов И, второй вход преобразователя прямого кода в дополнительный код соединен с вторым управляющим входом первого элемента запрета, управляющим входом второго элемента запрета, информационными входами третьего и пятого элементов запрета, первым информационным входом шестого элемента запрета, вторым входом

5 первого элемента И и первым входом

0

5

0

5

второго элемента И, третий вход преобразователя прямого кода в дополнительный код соединен с вторыми информационными входами второго и шестого элементов запрета, управляющими входами третьего и четвертого элементов запрета, вторым управляющим входом пятого элемента запрета, вторыми входами второго и третьего элементов И, первым управляющим входом восьмого элемента запрета, и первым инверсным входом первого элемента ИЛИ, четвертый вход преобразователя прямого кода в дополнительный код соединен с вторыми управляющими входами седьмого и восьмого элементов запрета, третьим входом третьего элемента И и вторым инверсным входом первого элемента ИЛИ, третий вход КОТОРОГО сординен с выходом первого элемента запрета, выход второго элемента запрета соединен с первыми входами второго и четвертого элементов ИЛИ, выход третьего элемента запрета соединен с вторым входом второго элемента ИЛИ, выходы первого элемента И и четвертого элемента запрета соединены соответственно с входами третьего элемента ИЛИ, выходы пятого и шестого элементов запрета соединены соответственно с вторым и третьим входами четвертого элемента ИЛИ, выходы второго элемента И, седьмого и восьмого элементов запрета и третьего элемента И соединены соответственно с входами пятого элемента ИЛИ, выходы с первого по пятый элементов ИЛИ являются соответственно пятым, первым, вторым, третьим и четвертым выходами преобразователя прямого кода в дополнительный код.

0

5

0

5

0

5

первого, второго и третьего элементов И, с вторыми управляющими входами первого, второго и восьмого элементов запрета и информационными входами четвертого и шестого элементов запрета, третий вход преобразователя прямого кода в дополнительный код соединен с третьим входом первого элемента И, третьими управляющими входами первого и восьмого элементов запрета, информационными входами второго и седьмого элементов запрета и управляющими входами третьего и четвертого элементов запрета, четвертый вход преобразователя прямого кода в дополнительный код соединен с четвертым входом первого элемента И, четвертым управляющим входом первого элемента запрета, управляющими входами пятого, шестого и седьмого элементов запрета и информационным входом восьмого элемента запрета, выходы второго элемента И, третьего и четвертого элементов запрета соединены соответственно с входами первого элемента ИЛИ, выходы третьего элемента И, с пятого по восьмой элементов запрета соединены соответственно с входами второго элемента ИЛИ, выходы второго элемента запрета, первого и второго элементов ИЛИ, инверсный выход первого элемента И.и выход первого элемента запрета соединены соответственно с выходами с второго по шестой преобразователей прямого кода в дополнительный код.

Т I

Таблица 1

Таблица 2

7 5.3 &3

10

Т Т

fc/

//

44

/f

45

ФигЗ

u

У

I

Л/

10

л

36

Щиг.5

$

#.

41,

81

| Устройство для суммирования фибоначчиево-десятичных кодов | 1981 |

|

SU945862A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР по заявке № 4450608/24-24, ют | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-05-15—Публикация

1989-06-23—Подача