Изобретение относится к вычислительной технике и может быть использовано при построении арифметических устройств ЭВМ, а также в специализированных вычислительных машинах и цифровых устройствах роботизированных систем управления для сложения чисел с иррациональным основанием -JZ и обработки векторной информации в двумерной системе координат и является усовершенствованием изобретения по авт.св. № 1193665.

Цель изобретения - расширение функциональных возможностей за счет обеспечения суммирования чисел с иррациональным основанием как в дополнительном, так и в обратном кодах.

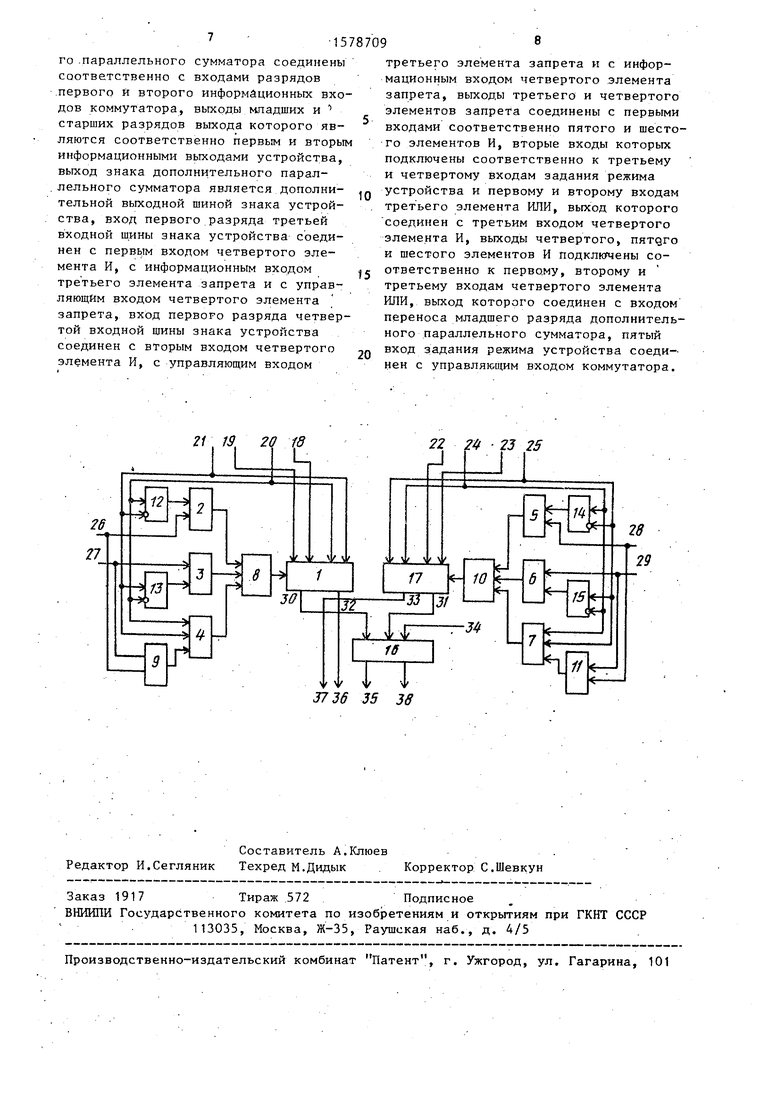

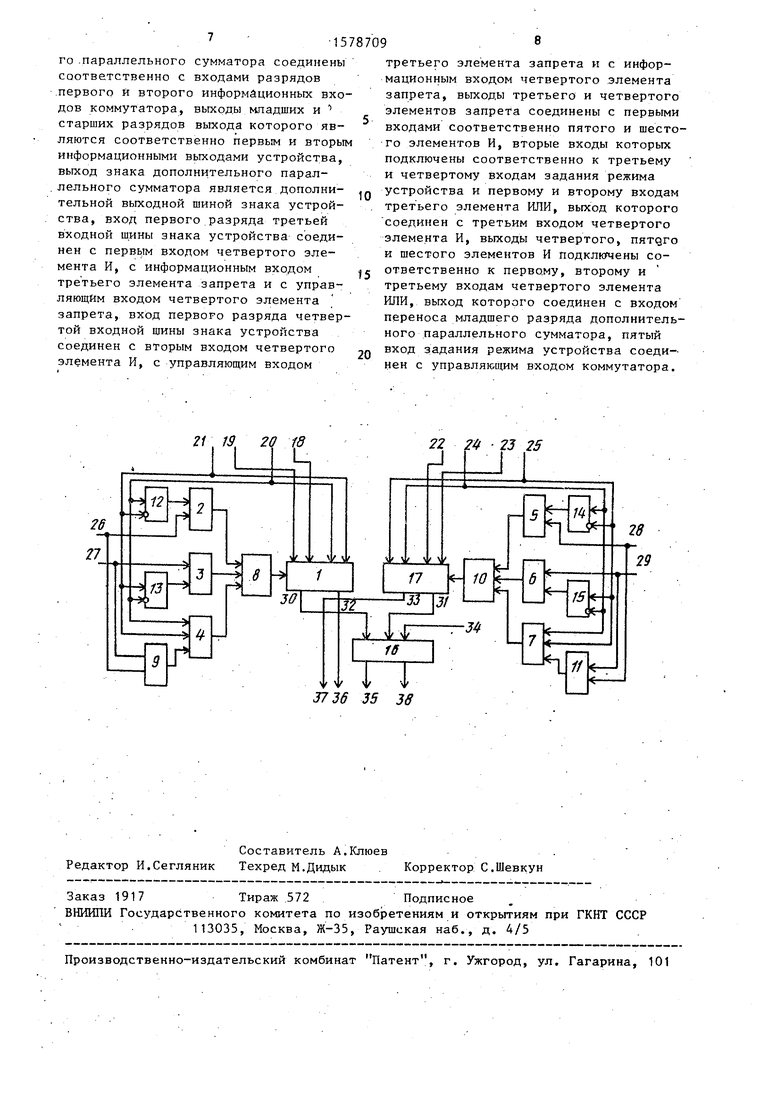

На чертеже представлена схема устройства для суммирования двоичных чисел.

Устройство содержит параллельный сумматор 1, второй и третий элементы И 2 и 3 соответственно, первый элемент И 4, пятый и шестой элементы И 5 и 6 соответственно, четвертый тпемент И 7, второй элемент ИЛИ 8, первый элемент ИЛИ 9, четвертый элемент ИЛИ 10, третий элемент ИЛИ II, г первого по четвертый элементы 12-13 запрета, коммутатор 16, дополнительный параллельный сумматор 17, первую и вторую входные числовые шины 18 и 19 устройства, первую и вторую в отные шины 20 и 21 знака устройства, третью и

сп vj

00 J

ГЧ)

315

четвертую входные числовые шины 22 и 23 устройства, третью и четвертую входные шины 24 и 25 знака устройства, с первого по четвертый входы 26-2 задания режима устройства, выходы 30 и 31 разрядов параллельного сумматора 1 и дополнительного параллельного сумматора 17 соответственно, выходы 32 и 33 знака параллельного сумматора 1 и дополнительного параллельного сумматора 17 соответственно, пятый вход 34 задания режима устройства, первый информационный выход 35 устройства, выходная шина 36 знака устройства, дополнительная выходная шина 37 знака устройства, второй информационный выход 38 устройства.

Устройствр для суммирования двоичных чисел предназначено для сложения операндов (векторов), представленных в двоично-кодированной позиционной системе счисления с иррациональным основанием -|2 как в дополнительном, так и в обратном коде.

В этой системе счисления любое число (вектор) представляется в виде

„., (Ч) -1 (42)-г +

+х

Лп-дЛ ДАп- «(#) +Х0(лГ2)° .

(1)

разрядов, то при этом выражения для четных и нечетных разрядов примут вид

10

9-

5

20

25

30

- 21х;i-0

l-

Xj 2 ,

(3)

где i,j € o,1,2,..., - 1J.

Сжатию нечетных разрядов предшествует их сдвиг вправо на один разряд.

Для суммирования операндов, четные и нечетные разряды которых представлены выражением (3), используются обыкновенные двоичные сумматоры. Кроме того -, за счет наличия двух сумматоров получена возможность одновременного и независимого сложения двух пар двоичных чисел как в дополнительном, так и обратном кодах.

Устройство для суммирования двоичных чисел может работать в двух режимах: в режиме сложения 2п-разрядных операндов (векторов) с иррациональным основанием -|2как в дополнительном, так и обратном коде; в режиме суммирования п разрядных двоичных чисел в дополнительном и обратном кодах.

Устройство в первом режиме работает следующим образом.

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельный накапливающий сумматор | 1988 |

|

SU1578710A2 |

| Последовательный сумматор | 1989 |

|

SU1709298A2 |

| Последовательный сумматор | 1987 |

|

SU1411734A1 |

| Сумматор последовательного действия | 1989 |

|

SU1689945A2 |

| Параллельный накапливающий сумматор | 1987 |

|

SU1587496A1 |

| Параллельный накапливающий сумматор | 1986 |

|

SU1399726A1 |

| Параллельный накапливающий сумматор | 1988 |

|

SU1564614A1 |

| Арифметико-логическое устройство | 1987 |

|

SU1495782A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1547062A1 |

| Устройство для суммирования двоичных чисел | 1985 |

|

SU1264164A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении арифметических устройств ЭВМ, а также в специализированных вычислительных машинах и цифровых устройствах роботизированных систем управления для сложения чисел с иррациональным основанием и обработки "векторной" информации в двоичной системе координат. Целью изобретения является расширение функциональных возможностей за счет обеспечения суммирования чисел с иррациональным основанием √2 как в дополнительном, так и в обратном кодах. Устройство содержит параллельный сумматор 1, элементы И 2 - 7, ИЛИ 8 - 11, запрета 12 - 15, коммутатор 16 и дополнительный параллельный сумматор 17 с соответствующими связями. 1 ил.

В связи с тем, что веса разрядов

данного кода являются последовательностью степеней основания -j

8 -J 8 4-if2 4 24 2 42 1,

четные степени которой представляют веса разрядов двоичного кода, а нечетные - веса разрядов двоичного кода, умноженные на -j, то выражение (1) можно записать так

X , (2)

г

где величины принимают з начения Х- ,ф J6 fl,3,5,...,n-l); Ji€{0,2,4,...,n-2l.

Первый член формулы (2) составляет сумму нечетных разрядов кода, а второ член - сумму четных разрядов кода с основанием -|2

Особенностью такого изображения

(77

является то, что код с основанием -у2, используемый для записи числа единый и в тоже время члены выражения (2) независимы друг от друга. Это позволяет при сложении двух операндов осуществлять параллельное и независимое сложение составных частей операндов. Если использовать операцию сжатия (опускание нулей) четных и нечетных

Числа А и В в виде сжатых четных разрядов и сжатых нечетных разрядов AjBji, поступающие на соответст- вующие входные шины 18, 20, 19, 21

и 22, 24, 23, 25 устройства, представлены п числовыми и, двумя знаковыми разрядами, а результат С (в сжатом состоянии) в виде четных разрядов Сц и нечетных разрядов С2 соответственно на выходах 30, 32 и 31, 33 представлен также п числовыми и двумя знаковыми разрядами. При этом четные , разряды слагаемых и нечетные разряды,поступающие на соответствующие шины 18,20, 19, 21 и 22, 24, 23, 25 устройства, кодируются обратными или дополнительными модифицированными кодами, а результат в виде четных Cj и нечетных С ч разрядов на выходах 30, 32 и 31, 33 - только в дополнительном модифицированном коде. Если числа А и В представлены в дополнительных модифицированных кодах, то на входах 26, 28 и 27, 29 задания режима устройства должны быть нулевые сигналы. При этом результат суммирования С (четные С и нечетные С разряды) также представлены в дополнительном модифицированном коде. Если число А представлено в обратном модифицированном коде, а число В - в дополнительном модифицированном коде, то на входах 26, 28 задания режима устройства должен быть единичный сигнал, а на входах 27 и 29 нулевой сигнал. При этом, если число А отрицательное (отрицательные четные А и нечетные А2 разряды), а число В положительное (положительные четные В и нечетные В2 разряды), то на выходах элементов 12 и 14 запрета, а следовательно, и на выходах элементов И 2, 5 и ИЛИ 8, 10 будут единичные сигналы, вследствие чего в младшие разряды сумматоров 1 и 17 поступает дополнительная единица. При условии, что числа А и В отрицательные, то на выходах элементов И 4, 7, а следова тельно, и на выходах элементов ИЛИ 8, 10 будут единичные сигналы, вследстви чего в младшие разряды сумматоров 1, 17 также поступит дополнительная еди- .ница. В том случае, когда числа А и В положительные или число А. положительное, а число В отрицательное, то на выходах элементов 12, 14 запрета И 2, 5; И 4, 7 и ИЛИ 8, Ю будут нулевые сигналы,вследствие чего в младший разряд сумматоров. 1, 17 дополнительна единица не поступает. Результат суммирования С представлен в дополнительно модифицированном коде.

Если число А представлено в дополнительном модифицированном коде, а число В в обратном модифицированном коде, то на входах 27, 29 задания режима устройства должен быть единичный сигнал, а на входах 26, 28 - нулевой. Если число В отрицательное, а число А положительное, то на выходах элементов 13, 15 запрета, а следо- вательнр и на выходах элементов И 3, 6 и ИЛИ 8, 10 будут единичные сигналы, вследствие чего в младшие разряды сумматоров 1, 17 поступает дополнительная единица. В том случае, когда числа А и В отрицательные, то на выходах элементов И 4, 7, а следовательно, и на выходах элементов ИЛИ 8, 10 будет единичный сигнал, вследствие чего в младшие разряды сумматоров 1, 17 также поступает дополнительная единица. При условии, что числа А и В положительные или число В положительное, а число А отрицательное, то на выходах элементов 13, 15 запрета И 3,

6; И 4, сигналы,

10

15

X)

25

30

35

7 и ИЛИ 8, 10 будут нулевые 1, вследствие чего в младшие разряды сумматоров 1, 17 дополнительная единица не поступает. Результат суммирования С представлен в дополнительном модифицированном коде. Сложение четных и нечетных (в сжатом виде) разрядов операндов осуществляется параллельными сумматорами 1, 17 по правилам двоичной информации. Для представления результата суммирования в коде с основанием -v|Z необходимо ко входу 34 приложить единичный сигнал,

тогда числовая информация в виде чет-- ных и нечетных разрядов, присутствующая на первом и втором входах коммутатора 16 с помощью его распределится таким образом, что нечетные разряды кода займут места между четными разрядами, т.е. будет сформирован окончательный код с основанием 2.

Работа устройства для суммирования двоичных чисел в режиме сложения двух пар п-разрядных двоичных операндов ничем не отличается от первого режима. Различие состоит в том, что для формирования результатов сложения следует приложить ко входу 34 нулевой сигнал. Тогда первый результат с выхода сумматора 1 передается в младшие- п разрядов, а второй результат с выхода сумматора 17 в старшие п разрядов выхода коммутатора 16.

Формула изобретения.

Устройство для суммирования двоичных чисел по авт. св. № 1193665,

отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения суммирования чисел с иррациональным основанием 42 как в дополнительном,

так и в обратном кодах, оно содержит четвертый, пятый и шестой элементы И, третий и четвертый элементы ИЛИ, третий и четвертый элементы запрета, коммутатор и дополнительный параллельный сумматор, причем третья и четвертая входные числовые шины устройства соединены соответственно с входами первого и второго слагаемых дополнительного параллельного сумматора, первый и второй входы знака которого соединены соответственно с третьей и четвертой входными шинами знака устройства, выходы разрядов параллельного сумматора и дополнительного параллельного сумматора соединены соответственно с входами разрядов первого и второго информационных входов коммутатора, выходы младших и старших разрядов выхода которого являются соответственно первым и вторым информационными выходами устройства, выход знака дополнительного параллельного сумматора является дополни- тельной выходной шиной знака устройства, вход первого разряда третьей входной шины знака устройства соединен с первым входом четвертого элемента И, с информационным входом третьего элемента запрета и с управляющим входом четвертого элемента запрета, вход первого разряда четвертой входной щины знака устройства соединен с вторым входом четвертого элемента И, с управляющим входом

третьего элемента запрета и с информационным входом четвертого элемента запрета, выходы третьего и четвертого элементов запрета соединены с первыми входами соответственно пятого и шестого элементов И, вторые входы которых подключены соответственно к третьему и четвертому входам задания режима устройства и первому и второму входам третьего элемента ИЛИ, выход которого соединен с третьим входом четвертого элемента И, выходы четвертого, пятдго и шестого элементов И подключены соответственно к первому, второму и третьему входам четвертого элемента ИЛИ, выход которого соединен с входом переноса младшего разряда дополнительного параллельного сумматора, пятый вход задания режима устройства соединен с управляющим входом коммутатора.

22 24 23 25

| Устройство для суммирования двоичных чисел | 1984 |

|

SU1193665A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-07-15—Публикация

1988-09-29—Подача