1

Изобретение относится к цифровой вычислительной технике.

Известно устройство для раскрытия определителей, содержащее матрицу ячеек памяти, логические схемы, селекторы и вспомогательное оборудование 1. Это устройство не позволяет производить вычисление плюс-определителей, (перманентов матриц).

Наиболее близки.м техническим решением к изобретению является устройство для анализа определителей, содержащее матрицу ячеек памяти, генератор импульсов, триггер 2. Кроме того, известное устройство содержит блок определения четности подстановок, логические элементы, выключатели ячеек строк и столбцов, искатель знака алгебраического дополнения и две группы переключателей ячеек памяти. С помощью известного устройства возможна организация счета плюс-определителей, для чего достаточно не проводить анализа на четность подстановок, что достигается отключением блока определения четности подстановок. Однако в этом устройстве затрачивается значительное время, так как в нем организуется перебор всех п перестановок, где празмерность исследуемого определителя.

Целью изобретения является повыщение быстродействия устройства.

Достигается это те.м, что устройство для анализа определитеоТей содержит блок перебора сочетаний, сумматоры и блок умножения, причем вход блока перебора сочетаний соединен с выходом генератора импульсов. Первые группы входов ячеек памяти столбцов подключены к первой группе соответствующих информационных щин, вторые группы входов - к соответствующим

вы.ходам блока перебора сочетаний, третьи группы входов ячеек памяти строк подключены к второй группе соответствующих информационных щин, выходы ячеек памяти строк подключены к входам соответствующих сумматоров, выходы которых подключены к входам блока умножения, выходы которого подключены к первым входам выходного сумматора, второй и третий входы выходного сумматора подключены к выходам триггера, счетный вход которого подключен

к второму выходу блока перебора сочетаний, третий выход которого подключен к четвертому входу выходного сумматора.

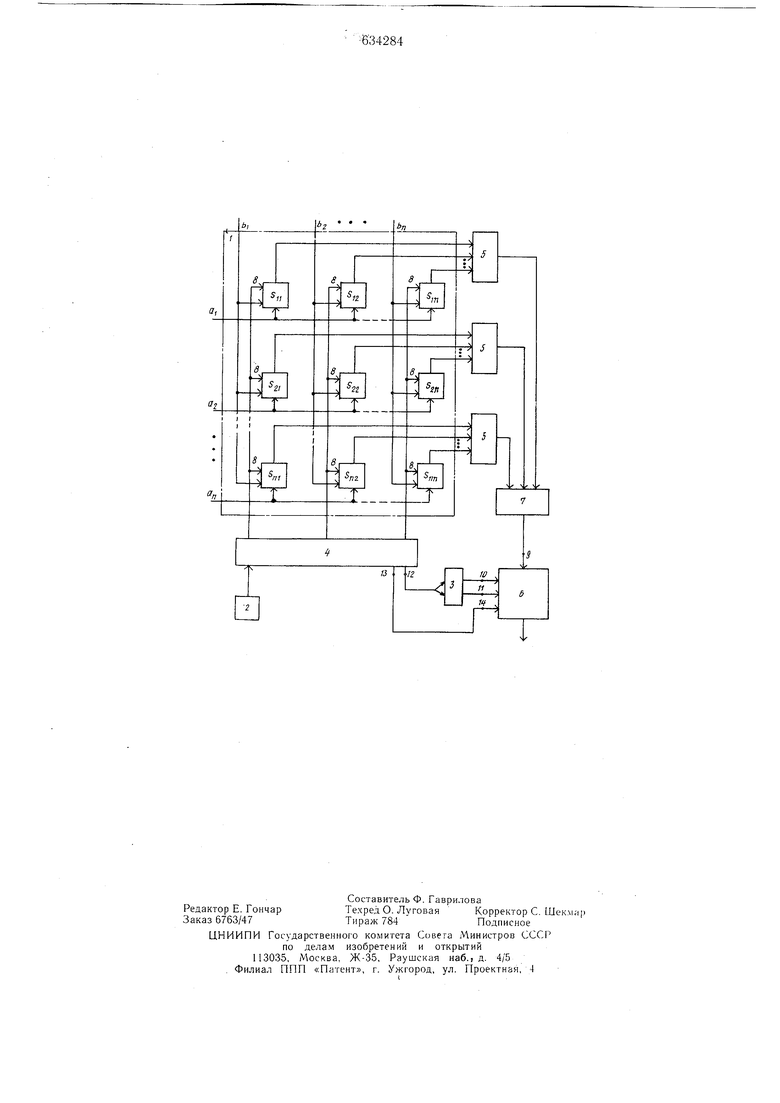

На чертеже представлена блок-схема устройства.

Устройство содержит матрицу 1 ячеек памяти, генератор импульсов 2, триггер 3, блок 4 перебора сочетаний, сумматоры 5, выходной сумматор 6 и блок умножения 7. Вход блока 4 перебора сочетаний соединен с выходом генератора импульсов 2, первые группы входов ячеек памяти столбцов подключены к первой группе в- соответствующих информационных шин, вторые группы входов 8 - к соответствующим выходам блока 4 перебора сочетаний, третьи группы входов ячеек памяти строк подключены к второй группе соответствующих информационных щин .,Выходы ячеек памяти строк подключены к входам соответствующих сумматоров

5,выходы которых подключены к входам блока умножения 7, выходы которого подключены к первым входам 9 выходного сумматора

6,второй 10 и третий 11 входы выходного сумматора 6 подключены к выходам триггера В, счетный вход которого подключен к второму вь.лоду 12 блока 4 перебора сочетаний, третий выход 13 которого подключен к четвертому входу 14 выходного сумматора 6.

Вычисление плюс-определителей производится по следующему алгоритму:

производится выбор всевозможных i столбцов из п (i п, п-1, ... 1);

для каждой выборки производится построчное суммирование выбранных столбцов и перемножения полученных результатов;

производится накопление (суммирование) результатов перемножения для всех Сп(i п, п-1,..,) выборок, причем знак слагаемых меняется при изменении i (при i п берется положительным, при i п-1 - отрицательным, при i п-2 - положительным и т. д,).

Работа устройства заключается в следующем.

Перед началом вычислений происходит настройка матрицы ячеек памяти 1, реализуемая по координатному принципу. Для настройки ячейки памяти посылаются соответствующие сигналы по информационным щинам uj ..и Bj,. на пересечении которых происходит запись соответствующей информации. Выбор всевозможных i столбцов из п (i п, п-1,..,1) осуществляется посредством блока 4 перебора сочетаний, производящего перебор всевозможных п-разрядных кодов с i единицами, причем выборке столбца соответствует наличие единицы на соответствующем выходе блока 4 перебора сочетаний. Изменение состояния блока перебора сочетаний происходит при поступлении сигнала с выхода генератора импульсов 2. При заверщении перебора всех Сп п-разрядных кодов с i единицами осуществляется переход к перебору всевозможных п-разрядных кодов с i-1 единицами, при этом на выходе 12 блока 4 перебора сочетаний-вырабатывается сигнал, перебрасывающий счетный триггер 3 в противоположное состояние.

Содержимое столбцов матрицы ячеек памяти, выбранных при каждом состоянии блока 4 перебора сочетаний, подается на сумматоры 5, в которых происходит построчное суммирование содержимого выбранных столбцов. С сумматоров 5 информация поступает в блок у.множения 7,.производящий перемножение результатов построчного суммирования содержимого выбранных столбцов матрицы ячеек памяти. Результат перемножения при каждой выборке поступает в накапливающий выходной сумматор 6 со знаком, зависящим от состояния счетного триггера 3. При единичном состоянии триггера 3 возбуждается вход приема в выходной сумматор 6 без изменения знака 10, а при нулевом состоянии триггера 3 возбуждается вход 11 приема слагаемых в выходной сумматор 6 с отрицательны.м знаком. Изменение состояния триггера 3 происходит по сигналу с выхода 12 блока 4 перебора сочетаний.

При выработке блоком перебора сочетаний всех

Z с;

состояний сигналом с выхода 13 блока 4 перебора сочетаний, привозбуждении входа 14 выходного сумматора 6, с последнего производится выдача результата вычисления плюс-определителя.

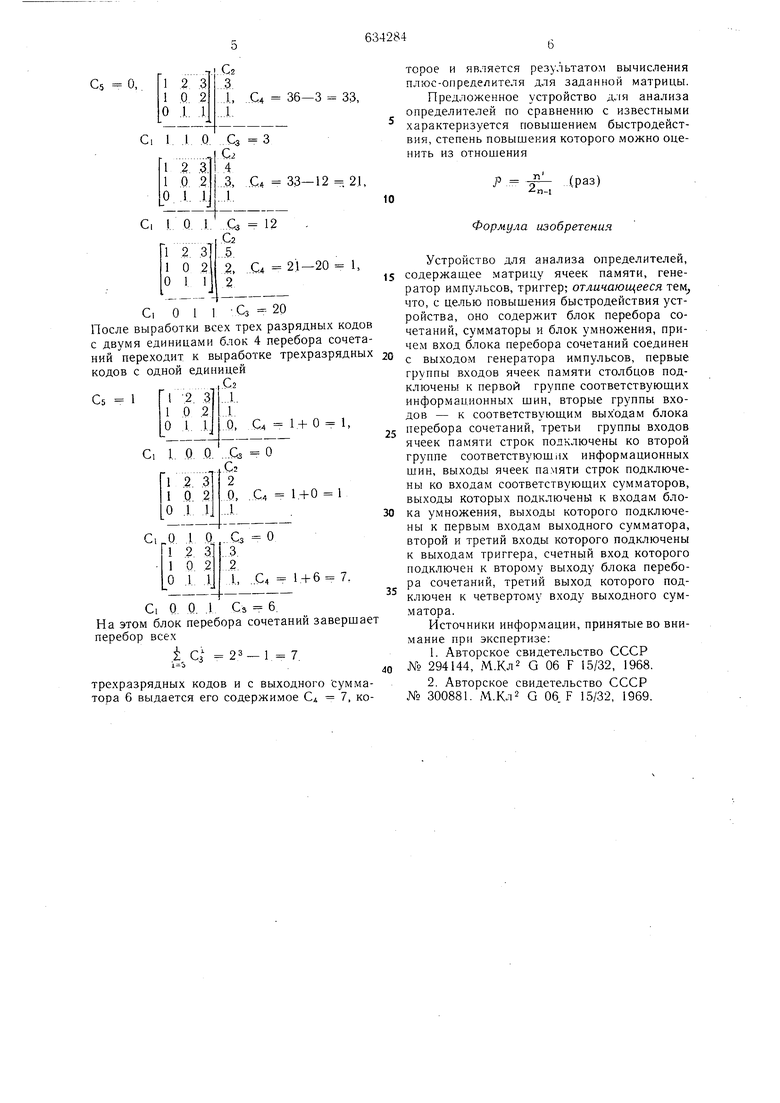

Пример последовательности вь числения плюс-определителя.

Пусть задана матрица

В виде обозначения:

Ci -состояние блока перебора сочетаний 4;

С2 - содержимое сумматоров 5;

Сз - содержимое блока умножения 7;

Q - содержимое выходного сумматора 6;

Cs -состояние триггера 3.

Процесс вычисления плюс-определителя заданной матрицы происходит в следующем порядке.

Вначале в блоке перебора сочетаний осуществляется перебор всевозможных трехразрядных кодов с тремя единицами

С2

6 3 2,

Cs 1,

. Сд 36.

С, 1.

.1. .1Сз 36

На этом перебор трехразрядных кодов с тремя единицами заканчивается и блок 4 перебора сочетаний переходит к выработке всевозможных трехразрядных кодов с двумя единицами Сэ О, Сз 3 Ci 1 1 О 1 2, .3. 1 4 1023, Сл О 1. 1J ..1. 1 О 1. Сз 12 Сз 1 2, 3 2, ,С.4 1 О 2 О 1 1 о 1 1 Сз 2 После выработки всех трех ра с двумя единицами блок 4 пе ний переходит к выработке кодов с одной единицей Сз 1 1 О, С.4 I -2 3 Cs 1 1 О 2 О 1 1 и 1 1J и, и Ci 1, 0. 0. ...Сз О Ci О 0. .1 Сз 6. На этом блок перебора сочет перебор всех i С, 2 трехразрядных кодов и с вых тора 6 выдается его содержим торое и является результатом вычисления плюс-определителя для заданной матрицы. Предложенное устройство для анализа определителей по сравнению с известными характеризуется повышением быстродействия, степень повышения которого можно оценить из отношения Формула изобретения Устройство для анализа определителей, содержащее матрицу ячеек памяти, генератор импульсов, триггер; отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит блок перебора сочетаний, сумматоры и блок умножения, причем вход блока перебора сочетаний соединен с выходом генератора импульсов, первые группы входов ячеек памяти столбцов подключены к первой группе соответствуюших информационных шин, вторые группы входов - к соответствующим выходам блока перебора сочетаний, третьи группы входов ячеек памяти строк подключены ко второй группе соответствуюших информационных шин, выходы ячеек па.мяти строк подключены ко входам соответствующих сумматоров, выходы которых подключены к входам блока умножения, выходы которого подключены к первым входам выходного сумматора, второй и третий входы которого подключены к выходам триггера, счетный вход которого подключен к второму выходу блока перебора сочетаний, третий выход которого подключен к четвертому входу выходного сумматора. Источники информации, принятые во внимание при экспертизе: 1.Авторское свидетельство СССР № 294144, М.Кл2 G 06 F 15/32, 1968. 2.Авторское свидетельство СССР № 300881. М.Кл2 G 06. F 15/32, 1969.

Авторы

Даты

1978-11-25—Публикация

1975-11-05—Подача