Изобретение относится к вычислительной технике и может быть использовано с специализированных вычислителях.

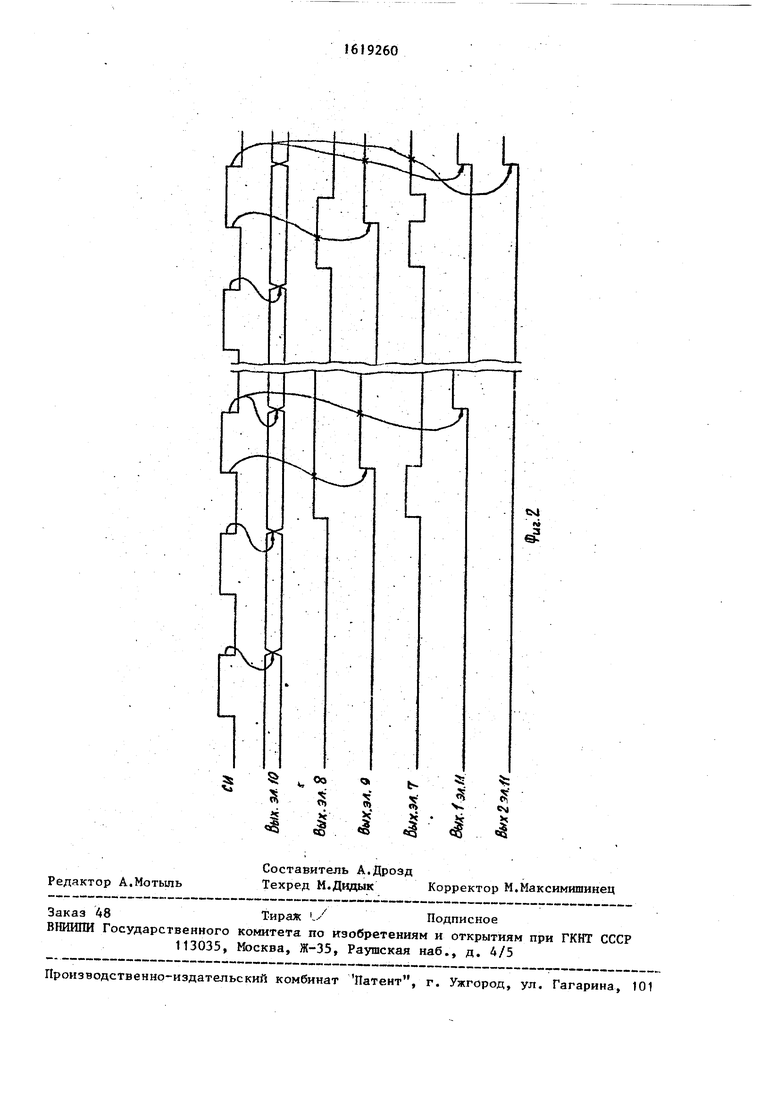

Цель изобретения - повышение достоверности функционирования.На фиг.1 представлена структурная схема устройства для случая на фиг.2 - временные диаграммы работы.

Устройство включает элементы И 1, сумматоры 2, группу сумматоров 3.1- 3.11 по модулю два, блок 4 свертки

по модулю три, первый 5, второй 6 и третий 7 сумматоры по модулю два, элемент И 8, триггер 9, выходной регистр 10 и регистр 11 контроля.

Устройство работает следующим образом.

Операнд поступает на входы разрядов операнда. При этом первый разряд операнда подается на первый информационный вход выходного регистра 10, второй разрядный выход результата устройства постоянно принимает значеся

CD N9

Ф

ния логического нуля. Кроме того, первый разряд 1р подается на первые входы элементов И 1 первого столбца, на вторые входы которых поступают соответственно разряды операнда 2р, Зр, 4р,5р и 6р. На выходах элементов И 1 первого столбца образуются конъюкции р-2р, р-3р, 1р-4р, 1р.5р, , которые поступают на вторые входы соответствующих сумматоров 2 первого столбца. Через первые входы и выходы этих сумматоров 2, как в сумматоре 2 последующих столбцов, распространяется сигнал переноса (кроме первого входа первого суммато ра два, который, как и в последующих столбцах, занулен,а также кроме пер- вого выхода последнего пятого сумматора 2, с выхода которого как и во втором столбце, сигнал переноса поступает на третий вход четвертого сумматора 2 последующего столбца, распространяется сигнал переноса и поступает на третий вход четвертого сумматора 2 последующего столбца). Третьи входы четных сумматоров первого столбца занулены, а на третьи входы первого, третьего и пятого сумматоров 2 первого столбца поступают разряды операнда соответственно 2р, Зр, 4р. При этом определяются третий и четвертый разряды результата, поступающие с вторых выходов первого и второго сумматоров 2 первого столбца на второй и третий информационные входы выходного регистра 10 соответственно. Сигналы суммы с вторых выходов третьего, четвертого и пятого сумматоров 2 первого столбца поступают, как и сигналы суммы с соответствующих сумматоров 2 второго столбца, на третьи входы соответственно первого, второго и третьего суммато-1 ров 2 следующего столбца. Элементы И 1 второго столбца вычисляют в соответствии с заведенными на их входы разрядами операнда конъюнкции 2р-3р, 2р.4р, 2р«5р, 2р 6р, , которые поступают на вторые входы сумматоров 2 второго столбца. На третий вход пятого сумматора 2 второго столбца поступает разряд операнда 5р При этом определяются пятый и шесто разряды результата, поступающие с вторых выходов первого и второго сумматоров 2 второго столбца на четвертый и пятый информационные входы выходного регистра 10 соответственно.

0

0

5

0

5

0

Элементы И 1 третьего столбца определяют в соответствии с заведенными на их входы разрядами операнда

конъюнкции Зр 4р, Зр Зр, Зр.бр, 4р 6р, Зр бр, которые поступают на вторые входы соответствующих сумматоров 2 третьего столбца. На третий вход пятого сумматора 2 третьего

столбца поступает разряд операнда 6р. При этом определяются последующие разряды результата, поступающие с вторых выходов сумматора 2 третьего столбца и первого выхода пятого суммато5 ра 2 третьего столбца соответственно на информационные входы выходного регистра 10 с шестого по одиннадцатый На синхровход выходного регистра 10 подаются через тактовый вход устройства синхросигналы СИ типа меандр. По заднему фронту синхросигнала СИ осуществляется прием разрядов результата в выходной регистр 10 (фиг.2), с выходов которого результат поступа-

5 ет на входы устройства: первый и с третьего по двенадцатый в соответствии с разрядами результата - 1рр и .

Кроме того, разряды результата рр и поступают на первые входы сумматоров 3.1-3.11 по модулю два группы соответственно. На вторые входы сумматоров 3.1-3.11 группы поступает сигнал с выхода триггера 9, принимающий при правильной работе устройства нулевое значение. Это же значение является исходным состоянием триггера 9 для работы устройства, что достигается включением в работу изначального исправного устройства или начальными сбросами триггера 9 и регистра 11 контроля в нулевое состояние после второго синхроимпульса СИ перед началом работы (цепи сброса не показаны для лучшего восприятия устройства) . Нулевое значение сигнала на выходе триггера 9 обеспечивает прохождение разрядов результата Зрр-12рр без изменения через сумматоры 3.2- З.И по модулю на входы блока 4 свертки по модулю два соответственно с первого по десятый, а также первого разряда результата 1р через сумматор 3.1 по модулю два группы на второй вход второго сумматора 6 по модулю

$ два. При этом блок 4 сверки по модулю два формирует остаток от деления десяти старших разрядов результата на модуль три. Два разряда полученного

5 16

остатка совместно с разрядом результата 1рр (с учетом, что ) составляют трехразрядный контрольный код |Jpp,2,lJ по модулю три всего результата, причем этот контрольный код не может для правильного результата возведения в квадрат принимать значения 101 и 010. Указанные значения выделяются в контрольном коде с использованием первого 5 и второго 6 сумматоров по модулю два, которые на этих значениях и только на них одновременно принимают соответственно единичное и нулевое значения, что и регистрирует элемент и 8. Единичное значение на выходе элемента И 8 указывает на получение запрещенных значений контрольного кода 101 и 050, а нулевое значение подтверждает правильное функционирование устройства.

Сигнал с выхода элемента И 8 поступает на первый вход третьего сумматора 7 по модулю два, а также записывается по переднему фронту синхросигнала СИ в триггер 9, с выхода которого поступает на первый информационный вход регистра 11 контроля, второй вход сумматора 7 по модулю два и вторые входы сумматоров 3.1-3.11 по модулю два группы. При неисправной работе устройства единичное значение с выхода триггера 9 обеспечивает инвертирование разрядов результата 1рр, Зрр-12рр на сумматорах 3. 1-3.1 1 по модулю два. Блок 4 свертки по модулю три и сумматор 3.1 по модулю два группы формируют на инверсном значении результата инверсное значение контрольного кода. При правильной работе блоков контроля одно запрещенное значение переходит в другое, инверсное ему запрещенное значение контрольного кода и сигнал на выходе элемента И 8 подтверждает свое единичное значение, третий сумматор 7 по модулю два сравнивает сигнал на выходах элемента И 8 и триггера 9 и результат сравнения записывается по заднему фронту синхросигнала СИ в регистр 11 контроля через его второй информационней вход. С первого и второго выходов регистра 11 контроля снимаются сигналы СК 1 и СК 2, поступающие соответственно на первый и второй контрольные выходы устройства. Сигналы контроля СК 1, переписываемый в регистр 11 контроля с выхода триггера 7, принимает нулевое значение при

10

92606

правильной работе устройства, а единичным значением отмечает нарушение функционирования устройства. Сигнал контроля СК 2 принимает нулевое значс ние при правильной работе блока контроля, которая обеспечивает совпадение сигналов, сравниваемых на третьем сум маторе по модулю два 7. Единичное значение сигнала СК 2 указывает на ошибочную работу блоков контроля при анализе прямого или инверсного значения результата. I «с Формула изобретения

0

5

Матричное устройство для возведения в квадрат, содержащее блок сверки по модулю три, первый и второй сумматоры по модулю два, элемент И и матрицу ячеек из п/2 столбцов и п-1 строк, где п - .четное число, разрядность операнда, причем каждая ячейка содержит сумматор и элемент И, первый выход сумматора ячейки i-й строки каждого столбца матрицы соединен с первым входом сумматора ячейки (п + )-й строки того же столбца матрицы (i I,n-2), выход элемента И каждой ячейки матрицы соединен с вторым входом сумматора этой же ячейки матрицы, первый выход сумматора ячейки (п -1)-й строки j-ro столбца матрицы соединен с третьим входом сумматора ячейки (п-2)-й строки (j + столбца матрицы (j 1, n/2-l), второй выход сумматора ячейки i-й строки j-ro столбца матрицы (,n-l) соединен с третьим входом сумматора ячейки (i -2)-й строки (j +1)-го столбца матрицы, первые входы элементов И ячеек первых (п - j)-x строк j-ro столбца (j 1, п/2), объединены между собой и подключены к входу j-ro разряда операнда устройства, второй вход элемента И ячейки i-й строки j-ro столбца матрицы (j 1, n-j) соединен с входом (i +j)-ro разряда операнда устройства, первые входы элементов И ячеек последних (j -l)-x строк j-ro столбца матрицы (для j 1) объединены между собой и подключены к входу (n/2+j)-ro разряда операнда устройства, второй вход элемента И ячейки i-й строки j-ro столбца матрицы (i n-j+l, n-1, j 1), соединен с входом (j +i -n/2)-ro разряда операнда устройства, третий вход сумматора ячейки (2j -1)-й строки первого

0

5

0

5

0

5

столбца матрицы подключен к входу (j +1)-го разряда операнда устройства, а третьи входы сумматоров ячеек четных строк первого столбца матрицы и первые входы сумматоров ячеек пер- вой строки всех столбцов матрицы подключены к входу логического нуля устройства, третий вход сумматора ячейки (п-1)-й строки j-ro столбца (j 1) матрицы соединен с входом (j + п/2)-го разряда операнда устройства, второй разрядный выход результата, которого соединен с входом логи10

венно к 2j-My и 2j +1)му информа ционноым входам выходного регистра

(j 1, iL/2 - 1) , второй выход сумма тора ячейки i-й строки n/2-ro стол ца матрицы соединен с (i + n - 1)-м информационным входом выходного ре гигтра, (i ), (2п-1)-й ин формационный вход выходного регист соединен с первым выходом сумматор ячейки (п-1)-й строки n/2-ro стол ца матрицы, выходы выходного регис подключены к первому и с третьего п

выходам устройства соответстЧеского нуля устройства, первый и вто-1с н .. - 1э венно, а также к

рой выходы блока свертки по модулю три соединены соответственно с первым и вторым входами первого сумматора по модулю два, выход которого соединен с прямым входом элемента И, инверсный вход которого соединен с выходом второго сумматэра по модулю два, первый вход которого соединен с первым выходом блока свертки по модулю три, отличающееся тем, что, с целью повышения достоверности функционирования, в него введены группа из 2п - 1 сумматоров по модулю два, третий сумматор по модулю два, триггер и регистр контроля, прцчем вход первого разряда операнда устрой - ства соединен с первым информационным входом выходного регистра, синх- ровход которого -объединен с синхро- входами триггера и регистра контроля и подключен к тактовому входу устройства, вторые выходы сумматоров ячеек первой и второй строк j-ro столбца матрицы подключены соответст20

25

30

35

, a. icutw c л первым входам соо ветствующих сумматоров по модулю дв группы, вторые входы которых объед нены и подключены к выходу тригге ра, выходы сумматоров по модулю дв группы, с второго по (2п-1)й соед нены с входами соответственно с пер вого по ()й блока сверки по модулю три, выход первого сумматора по модулю два группы соединен с вто рым входом второго сумматора по мод лю два, выход элемента И соединен с первым входом третьего сумматора п модулю два и входом триггера, выход которого соединен с вторым входом третьего сумматора по модулю дв и первым информационным входом реги ра контроля, второй информационный вход которого соединен с выходом тр тьего сумматора по модулю два, а пе вый и второй выходы регистра контро ля являются первым и вторым контрол ными выходами устройства соответств но.

венно к 2j-My и 2j +1)му информа- ционноым входам выходного регистра

(j 1, iL/2 - 1) , второй выход сумматора ячейки i-й строки n/2-ro столбца матрицы соединен с (i + n - 1)-м информационным входом выходного ре- гигтра, (i ), (2п-1)-й информационный вход выходного регистра соединен с первым выходом сумматора ячейки (п-1)-й строки n/2-ro столбца матрицы, выходы выходного регистра подключены к первому и с третьего по

н венно, а также к

, a. icutw c л первым входам соответствующих сумматоров по модулю два группы, вторые входы которых объединены и подключены к выходу триггера, выходы сумматоров по модулю два группы, с второго по (2п-1)й соединены с входами соответственно с первого по ()й блока сверки по модулю три, выход первого сумматора по модулю два группы соединен с вторым входом второго сумматора по модулю два, выход элемента И соединен с первым входом третьего сумматора по модулю два и входом триггера, выход которого соединен с вторым входом третьего сумматора по модулю два и первым информационным входом регистра контроля, второй информационный вход которого соединен с выходом третьего сумматора по модулю два, а первый и второй выходы регистра контроля являются первым и вторым контрольными выходами устройства соответственно.

аа

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричное устройство для возведения в квадрат | 1988 |

|

SU1520512A1 |

| Матричное устройство для возведения в квадрат | 1988 |

|

SU1509881A1 |

| Матричное устройство для возведения в квадрат | 1988 |

|

SU1608653A1 |

| Устройство для умножения чисел с контролем | 1988 |

|

SU1621033A1 |

| Устройство для умножения | 1988 |

|

SU1603379A1 |

| Устройство для умножения | 1989 |

|

SU1714592A1 |

| Устройство для вычисления сумм произведений | 1980 |

|

SU905814A1 |

| Множительно-делительное устройство | 1981 |

|

SU1267407A2 |

| Устройство для вычисления произведения векторов (его варианты) | 1984 |

|

SU1280389A1 |

| Устройство для вычисления сумм произведений | 1984 |

|

SU1166101A1 |

Изобретение относится к вычислительной технике и позволяет возводить n-разрядное число в квадрат с контролем и различением ошибок в основном и контрольном оборудовании, что является целью изобретения. Устройство содержит матрицу ячеек из п-1 строк и п/2 столбцов, состоящих из элементов И, сумматоров и вычисляющих 2п разрядов результата. Peзyльтat записывается в выходной регистр 10, с которого поступает на выходы устройства и через сумматоры по модулю два на входы блока свертки по модулю три. На выходах первого сумматора и блока свертки формируется трехразрядный контрольный код по модулю три результата, два значения которого 101 и 010 являются запрещенными. Два сумматора по модулю два и элемент И формируют на запрещенных значениях контрольного кода сигнал ошибки, принимающийся в триггер и с его выхода инвертирующий значение результата на а сумматорах по модулю два. При правиль- ной работе блоков контроля сигнал на входе, триггера подтверждается, что фиксируется сумматором по модулю два и записывается,как и сигнал с триггера в регистр контроля, 2 ил.

VO

«О

I

| Матричное устройство для возведения в квадрат | 1985 |

|

SU1439583A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Матричное устройство для возведения в квадрат | 1988 |

|

SU1509881A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-01-07—Публикация

1989-05-03—Подача