выходе устройства, и расишрение функциональных возмо 1 ностей устройства.

Она достигается тем, что, в преобразователь цифрового кода в аналоговый эквивалент, содержащий блок цифрового ввода, блок аналоговых величин, блок аиалоюаого суммирования и сглаживания, блок цифровой синхронизации и два тракта цифроаиа.К) ового нреооразсизаиия, состоящее каждый из б,тока цифровой памяти, к выходу которого подк.лючен иервый вход блока аналогового модулятора, первый вход каждого блока цифровой памяти подключен к первому выходу блока цифрового ввода, второй вход каждого блока аналогового модулятора иодключеи к выходу блока аналоговых величии, выходы блока цифровой синхронизации подключено: к соответствующим входам каждого б.кжа цифровой памяти и блока аналогово|-о модулятора, выходы блоков аналоговых модуляторов подключены к соответствующим входам блока аналогового суммирования и сглаживания, введены блок 101фроБого упреждения и блок цифрового заггаздывания, причем второй выход блока цифрово1О ввода .подключен ко входам блоков цифрового ч1реждения и цифрового запаздываиля, выход блока цифрового упреждения соединен с третьим входом первого блока цифровой памяти, а выход блока цифрового запаздывания соединен с третьим входом второго блока цифровой памяти.

Таким образом, преобразователь цифрового кода в аналоговый эквивалент выполняется на пара,1лельно-последовательной блок-схеме, включающей два параллельных тракта цифроаналогового преобразования. этом между вторым выходом блока цифрового ввода и третьи.м входо.м одного из трактов цифроаналогового преобразователя включен блок цифрового упреждения, а между вторы.м в)1ходо.м блока цифрового ввода и третьим входом другого тракта цифроаналогового преобразования - блок цифрового запаздывания, осуществляющие сдвиг временных циклов работы трактов на - г и -г соответственно.

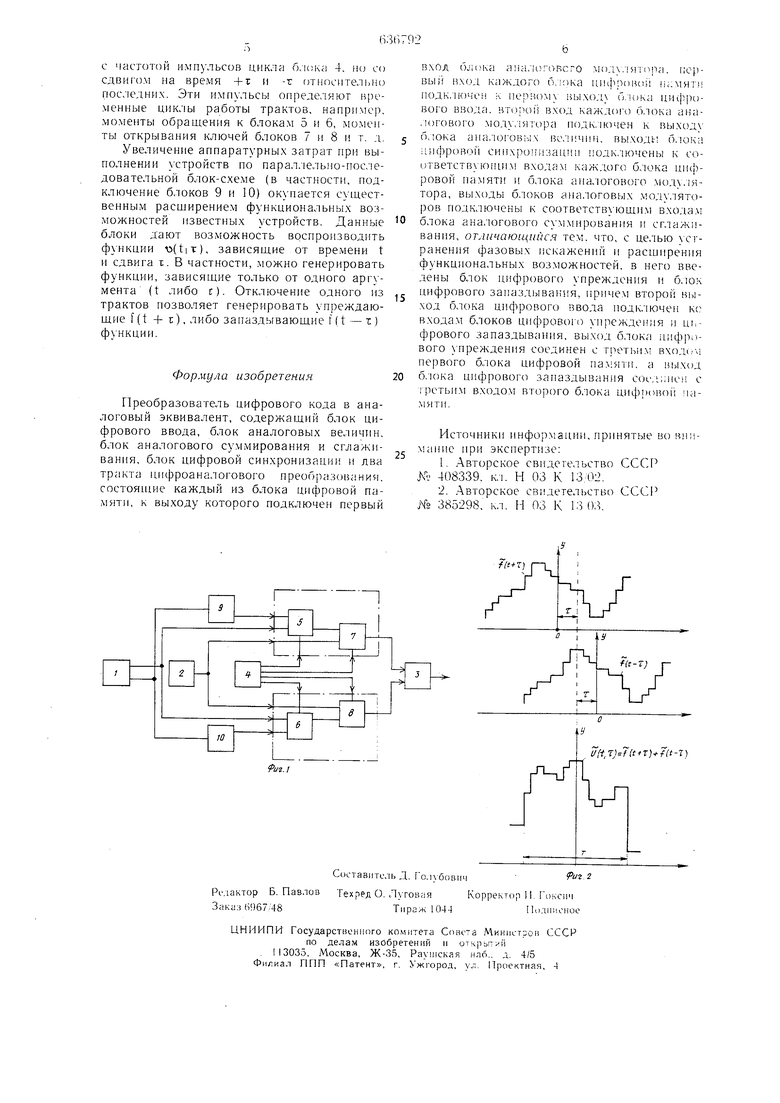

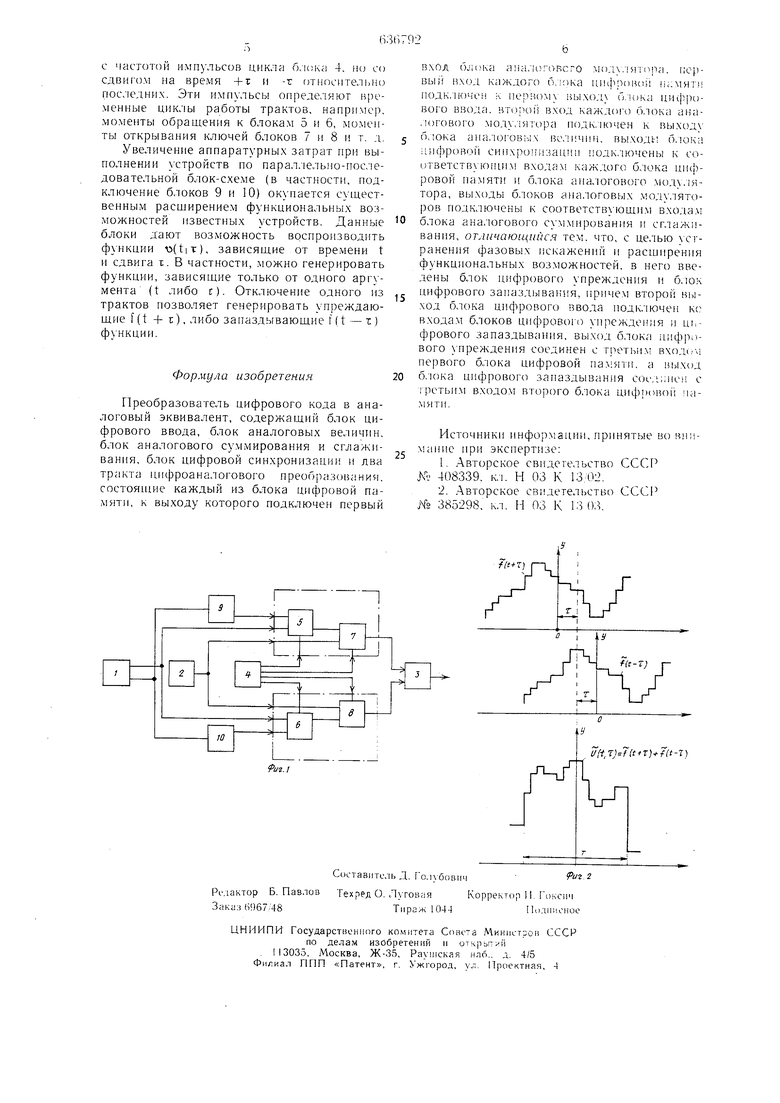

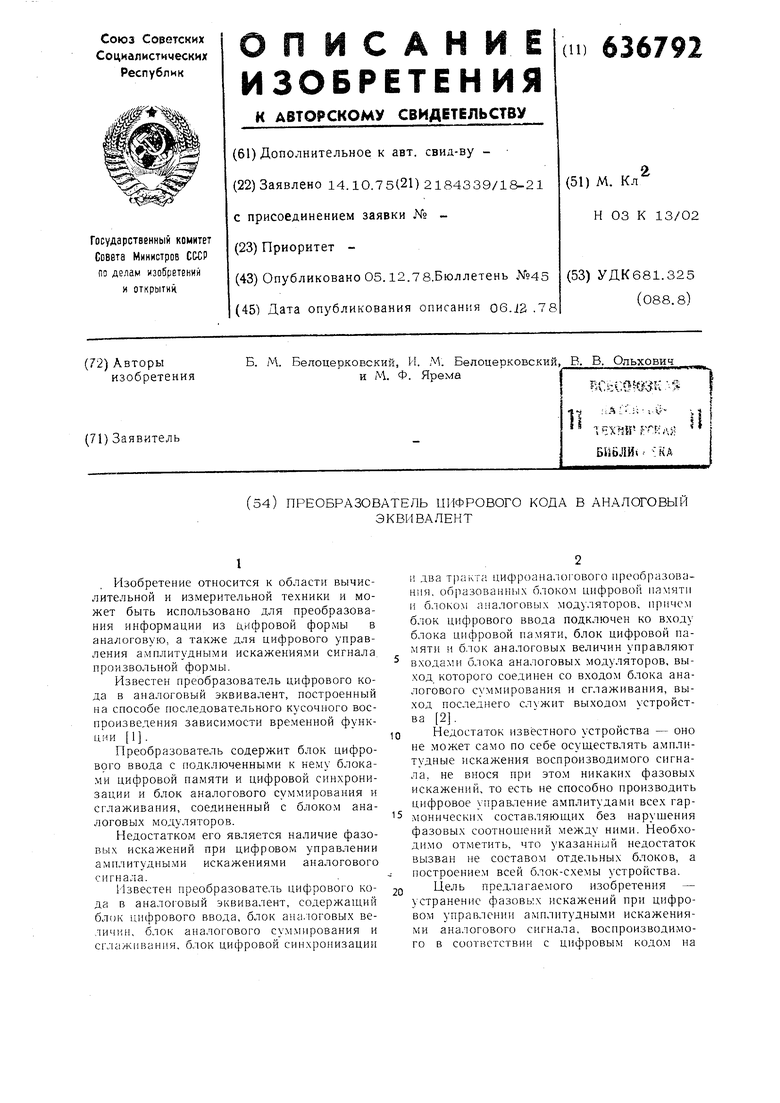

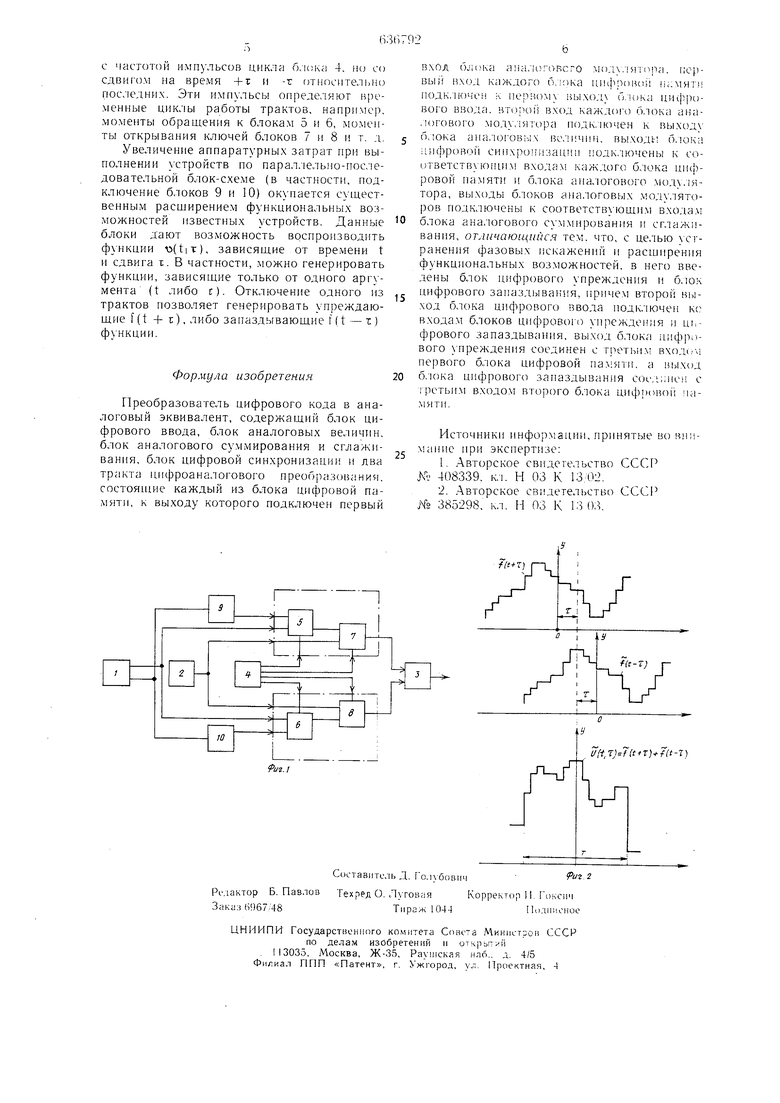

На фиг. 1 приведена структурная схема пре()б;)азопате,, на фиг. 2 - временная ди;upa i I;, поясняющая принцип его работы.

Схема (фиг. 1) содержит блок 1 цифрового ввода, блок 2 аналоговых величин, блок 3 аналогового суммирования и сглаживания, блок 4 цифровой синхронизации, блоки 5 и 6 цифровой памяти, блоки 7 и 8 аналоговых модуляторов, блок 9 цифрового упреждения и блок 10 цифрового за 1аздывания.

Благодаря сдвигу временных циклов работы трактов на -f-т и -т соответственно, первый тракт цифроаналогового преобразователя вырабатывает упреждающую запаздывающую ступенчатую структуру F(t + т: )V. Обе структуры совершенно и.аентичны, но

с.твииуть на 2i друг относите, 1)Но дру1а. После еуммирг)вания в 6;ioi e 3 ио.лучается Структура | t, г j (t - г ) - f (t -- г ), которая затем подвергается сглаживанию. Сдвиг г оп)еделяется чис.юм S, которое запоминается и блоке 1 и остается неизменным в течение отрезка времени, кратного периоду Т tr,- to. Из.меняя S, можно активно управлять формой KpuKofi 4)(tir).

Покажем, что ступенчатая структура э(ti г) действительно представляет собой амплитудно искаженный сигнал T(t) {какие-либо фазовые искажения одного сигнала по отношению к друго.му отсутствуют). Д.1Я этого представим f(t) рядом Фурье

Г(У-2 А, cosfK(0(1).

К-О

1де в оби1,ем случае

АГ,СОЗ foCO ccnsi,

20f h -) -f- «к(0). К - Тот же сигнал, сди.:. по времени в ту или сторону и;: р,с.1ич) с, записывается следующ ;м образом

f (t г г} JS Ai.cos f(t ±г).

где

f(l ±r.)-(p.cO)-k,t +

-f-cp(0;±ka;r f..(, 30 с.;1едовательно, сумма сигналов f (t т-т) и

I (I - т ) дает

Ct.t) Тс t ч-t) +-Г(1 - О - 2 .(cosff,(0k -

-Г koot i-ccs -k otrj} После т()ждоствеп1;ых тригонометрических пре ;браз1) из поеледнегО равенства по:|учаем

1 (t, С} S Aijcoskwot cos (f, /t) (2)

Видим, что по сравпению с исходным сигналом (I) преобразованный сигнал (2) содержит любую k-ю гармонику с из.мененной в ji cos k со о т раз амплитудой, но с неизменной фазой Фк;(Л). В частности, применение указанных операций (сдвига на -f г

и и последующего суммирования) к моп(гармоническо.му сигналу f (t) A,cos cuo t -т-q 1 (0) приводит к изменению TcxibKO амплитуды сигнала в ф; coscooc раз без искажения его |}х)рмы. Последнее может i-icno.ib,OBaH() д.1я осушести,чепия ц||(|1ровой ам ;:пту.и1ой модуляции гармор1пческого cnrna/ia.

Выполнение преобразовате. 1Я по параллельно-последовательной блок-схеме (фиг, 1) связано с подключением блоков 9 и 10 между вторым выходом блока 2 и третьи.ми входами блоков 5 и 6. Код числа S по BTOpOjMy выходу блока 1 поступает в блоки 9 и 10, где преобразуется в импульсы, следующие

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1987 |

|

SU1494210A1 |

| Формирователь частотно-модулированных сигналов | 1990 |

|

SU1732420A1 |

| Цифровой фильтр | 1986 |

|

SU1387174A1 |

| Цифровой фильтр с дельта-модуляцией | 1985 |

|

SU1347188A1 |

| Устройство для формирования сигналов передачи данных | 1980 |

|

SU1019659A1 |

| Устройство для телевизионной игры | 1977 |

|

SU736992A1 |

| СПОСОБ И УСТРОЙСТВО СИНТЕЗА, ПЕРЕДАЧИ, ПРИЕМА, АНАЛИЗА И ОЦЕНКИ МНОГОВАРИАНТНЫХ ПО ФОРМЕ, МНОГОПОЗИЦИОННЫХ И ЛОКАЛЬНЫХ ПО СПЕКТРУ СИГНАЛОВ | 2000 |

|

RU2160509C1 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ С ЛИНИЕЙ ПЕРЕДАЧИ | 2010 |

|

RU2420866C1 |

| ФОРМИРОВАТЕЛЬ РАДИОСИГНАЛОВ С ЦИФРОВЫМ ПРЕДЫСКАЖЕНИЕМ ЧЕТНЫМИ ГАРМОНИКАМИ | 2013 |

|

RU2538306C1 |

| РАДИОЛИНИЯ С АМПЛИТУДНО-ФАЗОМАНИПУЛИРОВАННЫМИ ШУМОПОДОБНЫМИ СИГНАЛАМИ | 1999 |

|

RU2144272C1 |

Авторы

Даты

1978-12-05—Публикация

1975-10-14—Подача