со оо

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1987 |

|

SU1494210A1 |

| Цифровой фильтр | 1987 |

|

SU1425840A1 |

| Цифровой фильтр с дельта-модуляцией | 1987 |

|

SU1418908A1 |

| Цифровой фильтр с дельта-модуляцией | 1988 |

|

SU1527713A1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1988 |

|

SU1587624A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1986 |

|

SU1424119A1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1989 |

|

SU1661968A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1987 |

|

SU1481893A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1988 |

|

SU1589383A1 |

| Цифровой фильтр | 1988 |

|

SU1617635A1 |

Изобретение относится к вычислительной технике. Его использование в устройствах цифровой обработки случайных процессов (фильтрация и спектральный анализ) позволяет повысить быстродействие цифрового фильтра. Цифровой фильтр содержит счетчик 3, блок 5 мультиплексирования блок 6 оперативной памяти, элемент ИЛИ-НЕ 7, генератор 10 импульсов, счетчики 11, 12, блок 13 постоянной памяти, источник 14 логического нуля, формирователь 15 импульсов, накапливающие сумматоры 16, 17 и цифроаналоговый преобразователь 18. Введение модулятора 1 дифференциальной импульсно-кодовой модуляции, перемножителя 2, сумматора 4, элемента ИЛИ-НЕ 8 и элемента. ЗАПРЕТ 9 обеспечивает вычисление свертки в формате многоуровневой дельта-модуляции.или дифференциальной импульсно-кодовой модуляции, разрядность которой меньше разрядности обычной импульсно-кодовой модуляции, а также перевод блоков 6 и 13 памяти в невыбранный режим для нулевых значений шагов квантования. 3 ил. а (Л

CDU.1

Изобретение относится к вычислительной технике и может быть использовано в устройствах цифровой обработки случайных процессов, например, при фильтрации и спектральном анализе.

Цель изобретения - повышение быстродействия цифрового фильтра.

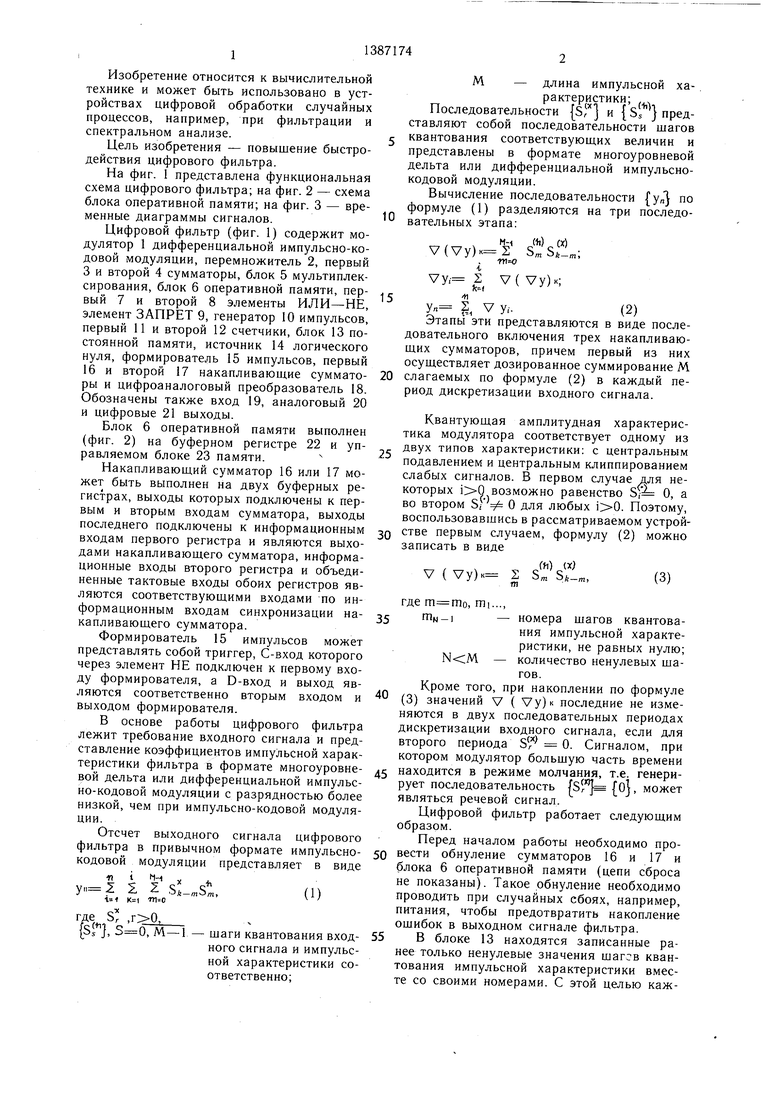

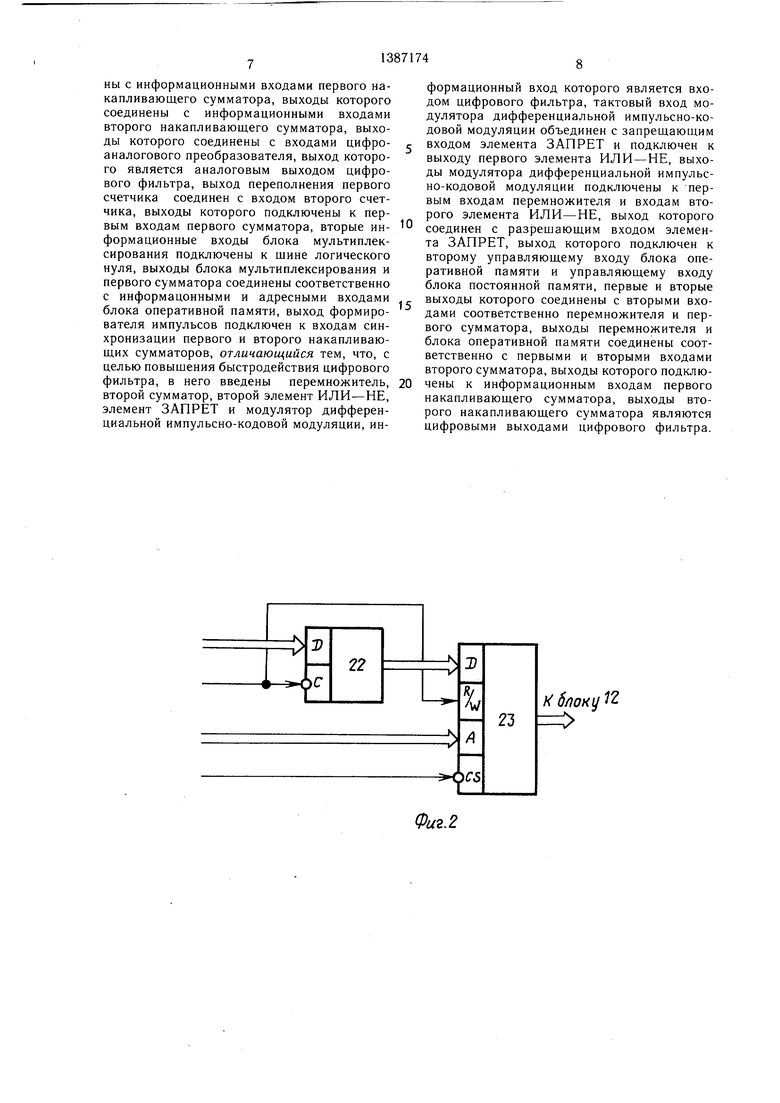

На фиг. 1 представлена функциональная схема цифрового фильтра; на фиг. 2 - схема блока оперативной памяти; на фиг. 3 - временные диаграммы сигналов.

Цифровой фильтр (фиг. 1) содержит модулятор 1 дифференциальной импульсно-ко- довой модуляции, перемножитель 2, первый 3 и второй 4 сумматоры, блок 5 мультиплексирования, блок б оперативной памяти, первый 7 и второй 8 элементы ИЛИ-НЕ, элемент ЗАПРЕТ 9, генератор 10 импульсов, первый 11 и второй 12 счетчики, блок 13 постоянной памяти, источник 14 логического нуля, формирователь 15 импульсов, первый 16 и второй 17 накапливающие сумматоры и цифроаналоговый преобразователь 18. Обозначены также вход 19, аналоговый 20 и цифровые 21 выходы.

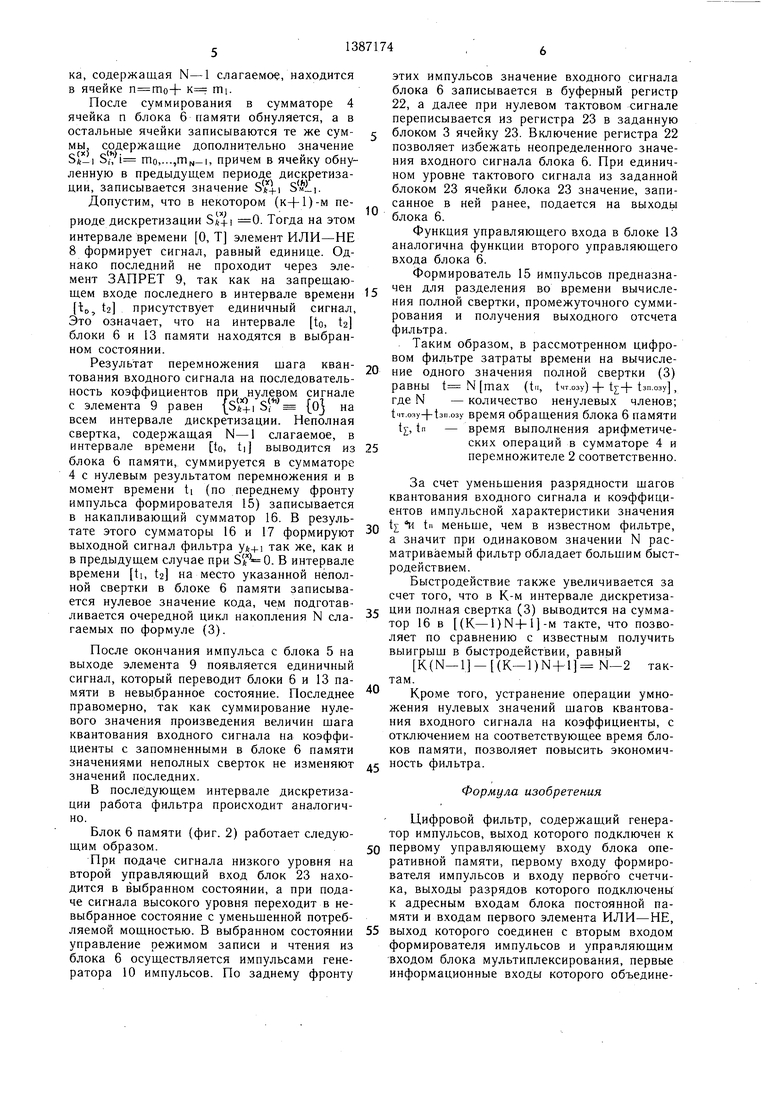

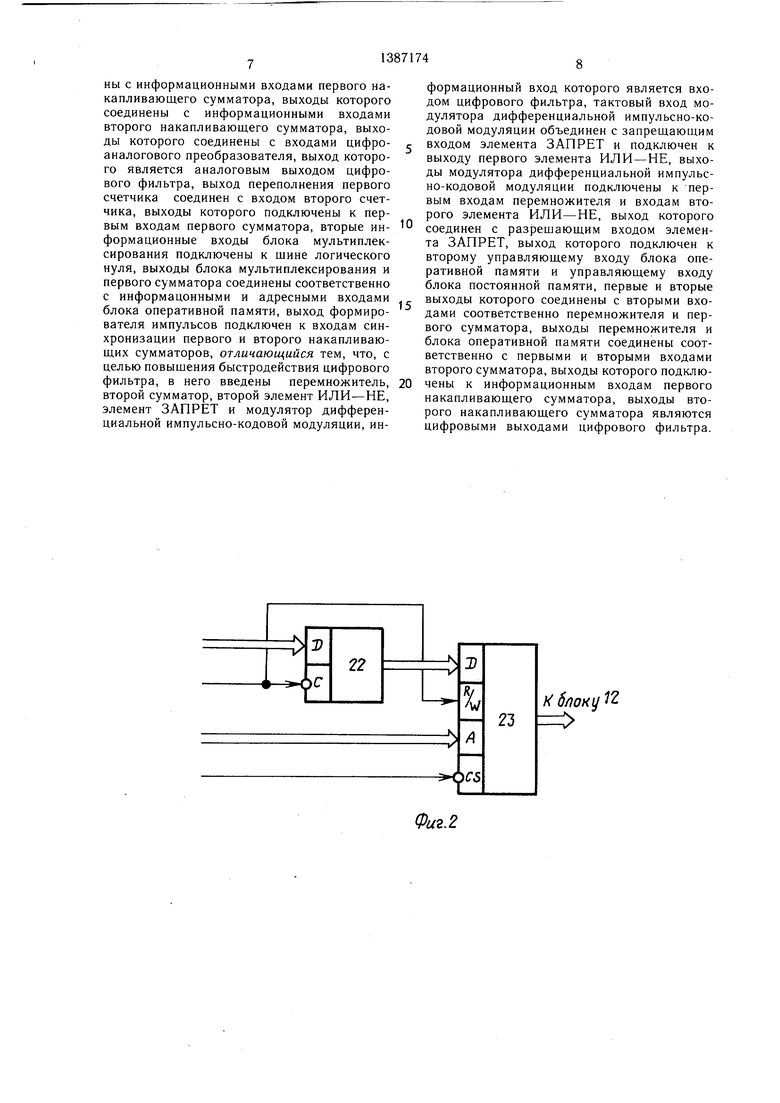

Блок 6 оперативной памяти выполнен (фиг. 2) на буферном регистре 22 и управляемом блоке 23 памяти.

Накапливающий сумматор 16 или 17 может быть выполнен на двух буферных регистрах, выходы которых подключены к первым и вторым входам сумматора, выходы последнего подключены к информационным входам первого регистра и являются выходами накапливающего сумматора, информационные входы второго регистра и объединенные тактовые входы обоих регистров являются соответствующими входами по информационным входам синхронизации накапливающего сумматора.

Формирователь 15 импульсов может представлять собой триггер, С-вход которого через элемент НЕ подключен к первому входу формирователя, а D-вход и выход являются соответственно вторым входом и выходом формирователя.

В основе работы цифрового фильтра лежит требование входного сигнала и представление коэффициентов импульсной характеристики фильтра в формате многоуровневой дельта или дифференциальной импульс- но-кодовой модуляции с разрядностью более низкой, чем при импульсно-кодовой модуляции.

Отсчет выходного сигнала цифрового фильтра в привычном формате импульсно- кодовой модуляции представляет в виде

п t ин ., . уг, 1 2 S,-n,S,(1)

i

S ,,

Мгде Ьг ,г

{srj,

-1 - щаги квантования входного сигнала и импульсной характеристики соответственно;

М - длина импульсной характеристики; . ,

Последовательности (S и {Sj } представляют собой последовательности щагов квантования соответствующих величин и представлены в формате многоуровневой дельта или дифференциальной импульсно- кодовой модуляции.

Вычисление последовательности {у„} по формуле (1) разделяются на три последо

вательных этапа:

М-1 tti) (X)

V(Vy) ,;

Vy.- 2 V(Vy)K;

t;-l

у„ S, Vy.-.(2)

Этапы эти представляются в виде последовательного включения трех накапливающих сумматоров, причем первый из них осуществляет дозированное суммирование М

слагаемых по формуле (2) в каждый период дискретизации входного сигнала.

Квантующая амплитудная характеристика модулятора соответствует одному из двух типов характеристики: с центральным подавлением и центральным клиппированием слабых сигналов. В первом случае для некоторых возможно равенство 5, О, а во втором Si О для любых . Поэтому, воспользовавшись в рассматриваемом устрой- стве первым случаем, формулу (2) можно записать в виде

W (Ю V ( Vy)K 2 Sm ,

(3)

где , гпь..,

niw-i- номера щагов квантования импульсной характеристики, не равных нулю; - количество ненулевых щагов.

Кроме того, при накоплении по формуле (3) значений V ( Vy) последние не изменяются в двух последовательных периодах дискретизации входного сигнала, если для второго периода S 0. Сигналом, при котором модулятор больщую часть времени находится в режиме молчания, т.е. генерирует последовательность /Sr (Oj, может являться речевой сигнал.

Цифровой фильтр работает следующим образом.

Перед началом работы необходимо про- вести обнуление сумматоров 16 и 17 и блока 6 оперативной памяти (цепи сброса не показаны). Такое обнуление необходимо проводить при случайных сбоях, например, питания, чтобы предотвратить накопление ощибок в выходном сигнале фильтра. В блоке 13 находятся записанные ранее только ненулевые значения щагсв квантования импульсной характеристики вместе со своими номерами. С этой целью каждое слово блока 13 разбито на две части. В части, соответствующей первым выходам

блока 13, содержится значение шага S, а в части, соответствующей вторым выходам блока 13, его номер i g (а/а О, М-1 J. Таким образом, всего используется N ячеек блока 13 памяти.

Тактовые импульсы (фиг. За) частотой (Т - период дискретизации) с выхода генератора 10 импульсов поступают на счетный вход счетчика 11 и первый управляющий вход блока 6 памяти, куда записываются произведения. По нулевому значению выходного кода счетчика 11 на выходе элемента ИЛИ-НЕ 7 формируется импульс (фиг. 36), по переднему фронту которого (в момент времени to) производится считывание выходного сигнала модулятора 1 (фиг. Зв), на информационный вход которого с входа 19 подается входной аналоговый сигнал. Выбор блоков 6 и 13 памяти производится при помощи сигнала на выходе элемента ЗАПРЕТ 9 при низком уровне которого блоки 6 и 13 находятся в выбранном, а при высоком уровне - в невыбранном состояниях. Управление режимом работы блока 6 памяти (чтение / запись) производится при помощи сигнала с генератора 10 (фиг. Зв), при высоком уровне которого производится чтение из блока 6, а при низком - запись в блок 6.

Допустим, что в данном периоде дискретизации Т выходной сигнал модулятора 1 S fe Ф 0. Это приводит к тому, что выходной сигнал элемента ИЛИ-НЕ 8 (фиг. Зг), а значит и сигнал с элемента 9 (фиг. Зд) равны нулю, т.е. блоки 6 и 13 находятся на протяжении указанного периода дискретизации Т в выбранном состоянии. На интервале О, Т значение сигнала 5 поступает на входы перемножнтеля 2, на другие входы которого последовательно подаются в циклическом порядке с первых выходов блока 13 памяти все N ненулевых значений шагов квантования ( , каждый на протяжении времени . Результат перемножения 5 %одается на первые входы сумматора 4, на вторые входы которого подается сигнал с выхода блока 6 памяти в режиме чтения.

Сумматор 4 суммирует на протяжении интервалов времени to, t|) t2, 1з и так далее выходные значения перемножителя 2 со знaчeниям f запомненных в блоке 6 сумм произведений щагов квантования на коэффициенты (неполных, т.е. содержащих менее N слагаемых сверток (3). В последующие интервалы времени ta, t4 и так далее, начиная с заднего фронта сигнала генератора 10 и при равенстве этого сигнала нулю (фиг. За), производится запись накопленной величины сигнала (соответствующей неполной свертке), в ту же ячейку блока 6 памяти через блок 5 мультиплексора.

0

5

0

5

0

5

0

5

Такое накопление сигнала в виде неполной свертки проводится на протяжении всех интервалов времени , кроме to, t2, когда появляется импульс с выхода элемента ИЛИ-НЕ (фиг. 36). В интервале времени toti сигнал с выходов блока 6 памяти, соответствующий неполной свертке и содержащий N-1 слагаемое, суммируется в сумматоре 4 с очередным значением выходного сигнала перемножителя 2. В результате этого суммирования он становится равным полной свертке (3). Импульс с элемента 7 на время t G toto переводит блока 5 мультиплексирования в другое положение, в результате чего в момент времени ti, т.е. по переднему фронту импульса формирователя (фиг. Зе), выходной сигнал сумматора 4 записывается в накапливающий сумматор 16, а в соответствующую ячейку блока 6 памяти в интервале времени ti,t2 записывается «О.

Накапливающий сумматор 16 формирует за период tits (время существования импульса формирователя 15) значение сигнала V УП, который по заднему фронту импульса формирователя 15 (момент времени ta записывается в сумматор 17, где суммируется с предыдущим отсчетом выходного сигнала фильтра уп-и в результате чего на цифровых выходах 21 фильтра формируется выходной сигнал ул в формате импульсно- кодовой модуляции. При помощи цифро- аналогового преобразователя 18 сигнал преобразуется в аналоговую форму у (t) и подается на аналоговый выход 20 фильтра. В последующие периоды дискретизации при . работа фильтра происходит аналогично.

Номера ячеек блока 6 памяти задаются рециркулирующими относительно номеров ячеек блока 13 памяти. Они вычисляются сумматором 3, суммирующим по модулю М код с вторых выходов блока 13, соответствующий последовательности номеров ненулевых щагов квантования ..., со значением кода на выходах счетчика 12, имеющего коэффициент пересчета М. Допустим, что в к-м периоде дискретизации значение выходного кода счетчика 12 тогда последовательность номеров ячеек блока 6 памяти имеет вид {п {(m4-K)modM то,..., (фиг. Зж, при то 0; ).

В этом -периоде дискретизации значение неполной свертки, содержащей N-1 слагаемое, находится в ячейке mo блока 6 и подается в интервале времени to, ti на сумматор 4, в результате чего на его выходах формируется полная свертка (3), а в указанную ячейку записывается нулевое значение кода. В следующем периоде дискретизации последовательность {п} смещается на единицу {п {(m--i-K)modM mi,...,, mo , свертка, содержащая N-1 слагаемо, находится в ячейке к mi.

После суммирования в сумматоре 4 ячейка п блока 6 памяти обнуляется, а в остальные ячейки записываются те же суммы, содержащие дополнительно значение то,...,, причем в ячейку обнуленную в предыдущем периоде дискретизации, записывается значение 5 м1.|.

Допустим, что в некотором (к+1)-м периоде дискретизации ST+i 0. Тогда на этом интервале времени О, Т элемент ИЛИ-НЕ 8 формирует сигнал, равный единице. Однако последний не проходит через элемент ЗАПРЕТ 9, так как на запрещающем входе последнего в интервале времени tp tg присутствует единичный сигнал. Это означает, что на интервале to, iz блоки 6 и 13 памяти находятся в выбранном состоянии.

Результат перемножения щага квантования входного сигнала на последовательность коэффициентов при нулевом сигнале с элемента 9 равен {Sft+iS (oj на всем интервале дискретизации. Неполная свертка, содержащая N-1 слагаемое, в интервале времени to, ti выводится из блока 6 памяти, суммируется в сумматоре 4 с нулевым результатом перемножения и в момент времени ti (по переднему фронту импульса формирователя 15) записывается в накапливающий сумматор 16. В результате этого сумматоры 16 и 17 формируют выходной сигнал фильтра yk+i так же, как и в предыдущем случае при . В интервале времени ti, t2 на место указанной неполной свертки в блоке 6 памяти записывается нулевое значение кода, чем подготавливается очередной цикл накопления N слагаемых по формуле (3).

После окончания импульса с блока 5 на выходе элемента 9 появляется единичный сигнал, который переводит блоки 6 и 13 памяти в невыбранное состояние. Последнее правомерно, так как суммирование нулевого значения произведения величин щага квантования входного сигнала на коэффициенты с запомненными в блоке 6 памяти значениями неполных сверток не изменяют значений последних.

В последующем интервале дискретизации работа фильтра происходит аналогично.

Блок 6 памяти (фиг. 2) работает следующим образом.

При подаче сигнала низкого уровня на второй управляющий вход блок 23 находится в выбранном состоянии, а при подаче сигнала высокого уровня переходит в не- выбрапное состояние с уменьщенной потребляемой мощностью. В выбранном состоянии управление режимом записи и чтения из блока 6 осуществляется импульсами генератора 10 импульсов. По заднему фронту

этих импульсов значение входного сигнала блока 6 записывается в буферный регистр 22, а далее при нулевом тактовом сигнале переписывается из регистра 23 в заданную

блоком 3 ячейку 23. Включение регистра 22 позволяет избежать неопределенного значения входного сигнала блока 6. При единичном уровне тактового сигнала из заданной блоком 23 ячейки блока 23 значение, записанное в ней ранее, подается на выходь

блока 6.

Функция управляющего входа в блоке 13 аналогична функции второго управляющего входа блока 6.

Формирователь 15 импульсов предназначен для разделения во времени вычисления полной свертки, промежуточного суммирования и получения выходного отсчета фильтра.

Таким образом, в рассмотренном цифровом фильтре затраты времени на вычисление одного значения полной свертки (3)

равны t N шах (t, 1чт.озу) tsn.oay,

где N - количество ненулевых членов;

t.iT.o3y-|--t3ri.o3y время обращения блока 6 памяти

tj;, tn - время выполнения арифметических операций в сумматоре 4 и

перемножителе 2 соответственно.

За счет уменьщения разрядности щагов квантования входного сигнала и коэффициентов импульсной характеристики значения

2 бньще, чем в известном фильтре, а значит при одинаковом значении N рас- матриваемый фильтр обладает больщим быстродействием.

Быстродействие также увеличивается за счет того, что в К-м интервале дискретизаЦии полная свертка (3) выводится на сумматор 16 в (К-1)N-|-1 -M такте, что позволяет по сравнению с известным получить выигрыщ в быстродействии, равный

K(N-1 -(К-1)N + 1 N-2 тактам.

Кроме того, устранение операции умножения нулевых значений щагов квантования входного сигнала на коэффициенты, с отключением на соответствующее время блоков памяти, позволяет повысить экономичность фильтра.

Формула изобретения

Цифровой фильтр, содержащий генератор импульсов, выход которого подключен к

первому управляющему входу блока оперативной памяти, первому входу формирователя импульсов и входу перво го счетчика, выходы разрядов которого подключены к адресным входам блока постоянной памяти и входам первого элемента ИЛИ-НЕ,

выход которого соединен с вторым входом формирователя импульсов и управляющим входом блока мультиплексирования, первые информационные входы которого объединены с информационными входами первого накапливающего сумматора, выходы которого соединены с информационными входами второго накапливающего сумматора, выходы которого соединены с входами цифро- аналогового преобразователя, выход которого является аналоговым выходом цифрового фильтра, выход переполнения первого счетчика соединен с входом второго счетчика, выходы которого подключены к первым входам первого сумматора, вторые ин- формационные входы блока мультиплексирования подключены к щине логического нуля, выходы блока мультиплексирования и первого сумматора соединены соответственно с информацонными и адресными входами блока оперативной памяти, выход формирователя импульсов подключен к входам синхронизации первого и второго накапливающих сумматоров, отличающийся тем, что, с целью повышения быстродействия цифрового фильтра, в него введены перемножитель, второй сумматор, второй элемент ИЛИ-НЕ, элемент ЗАПРЕТ и модулятор дифференциальной импульсно-кодовой модуляции, ин

с 0 0

формационный вход которого является входом цифрового фильтра, тактовый вход модулятора дифференциальной импульсно-кодовой модуляции объединен с запрещающим входом элемента ЗАПРЕТ и подключен к выходу первого элемента ИЛИ-НЕ, выходы модулятора дифференциальной импульсно-кодовой модуляции подключены к первым входам перемножителя и входам второго элемента ИЛИ-НЕ, выход которого соединен с разрешающим входом элемента ЗАПРЕТ, выход которого подключен к второму управляющему входу блока оперативной памяти и управляющему входу блока постоянной памяти, первые и вторые выходы которого соединены с вторыми входами соответственно перемножителя и первого сумматора, выходы перемножителя и блока оперативной памяти соединены соответственно с первыми и вторыми входами второго сумматора, выходы которого подключены к информационным входам первого накапливающего сумматора, выходы второго накапливающего сумматора являются цифровыми выходами цифрового фильтра.

f 2

Фи2.2

| Харатишвили Н | |||

| Г | |||

| Дифференциальная импульсно-кодовая модуляция в системах связи.- М.: Радио и связь, 1983, с | |||

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

| Цифровой фильтр | 1980 |

|

SU904201A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Цифровой фильтр | 1980 |

|

SU919054A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Цифровой фильтр | 1980 |

|

SU955512A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Цифровой фильтр с дельта-модуляцией | 1985 |

|

SU1347188A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-04-07—Публикация

1986-10-29—Подача