Изобретение относится к вычислительной технике и может быть использовано в сис темах цифровой обработки случайных процессов.

Цель изобретения - упрощение фильтра при числе коэффициентов импульсной характеристики 2 (k - целое число).

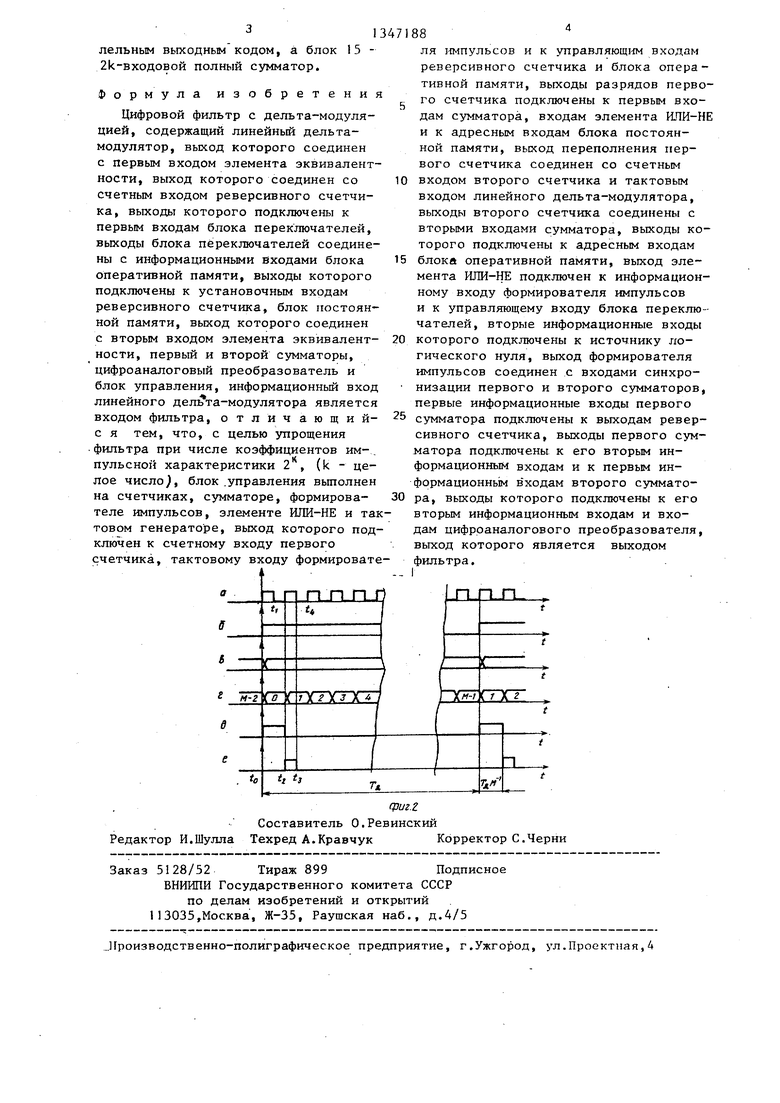

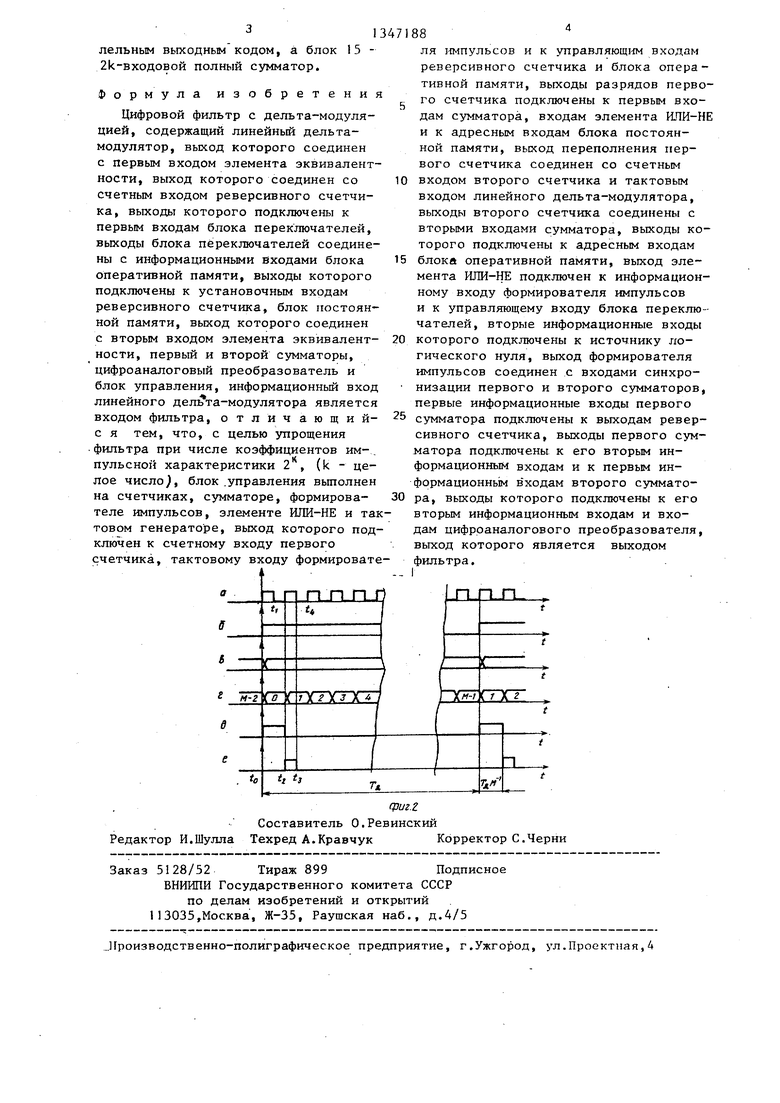

На фиг.1 показана функциональная схема цифрового фильтра с дель - та-модуляцией; на фиг.2 - временные диаграммы его работы.

Цифровой фильтр с дельта-модуляцией содержит линейньй дельта-модулятор 1 , блок 2 постоянной памяти, элемент 3 эквивалентности, реверсивный счетчшс 4, блок 5 переключателей, блок 6 оперативной памят

первый 7 и второй 8 сумматоры, цифро аналоговый преобразователь (ЦАП) 9 и блок 10 управления, включающий тактовый генератор 11, первьш 12 и второй 13 счетчики, элемент ШШ-НЕ 14, сумматор 15 и формирователь 16 импульсов . Кроме того цифровой фильтр содержит вход 17, источник 18 логического нуля и вькод 19 (фиг.1).

Цифровой фильтр с дельта-модуляцией работает следующим образом.

Тактовые импульсы (фиг.2 а) с выхода тактового генератора 11 с частотой М/Т, где М - число весовых коэффициентов; Тд - период дискретизации, поступают, на вход первого счетчика 12, на выходе переполнения которого формируется импульс с частотой Тд (фиг.2 б). По переднему фронту последнего производят считьшание выходного сигнала С } ЛДМ 1 . На интервале дискретизации 10,Т чение сигнала с ЛДМ 1 поступает (фиг,2 в) на один из входов элемента 3 эквивалентности, на второй вход которого последовательно подаются коэф

фициенты L, } , k o,M-1J ,каждый на протяжении времени Тд ( фиг. 2 г) . Порядок изменения коэффициентов постоянный и задается первым счетчиком 12. Результат перемножения

W (h

Li- Lц входного сигнала на коэффициенты подается на вход реверсивного счетчика 4. В интервалы времени t,,t, , производится чтение из блока 6 оперативной памяти и зались по установочным входам в реверсивный счетчик 4 величинг сигнала, соответствующего неполной

свертке. По заднему фронту тактового импульса (фиг.2 а) записанный в счетчике 4 сигнал суммируется с результатом перемножения входного сигнала на коэффициент импульсной характеристики. В интервалы ,1 и т.д. производится запись накопленной величины сигнала (соответствующего неполной свертке) в ту же ячейку блока 6 оперативной памяти через блок 5 переключателей. Переключатели блока 5 находятся в первом положении (DO UQ) - в этом случае отсутствует импульс (фиг.2 д) с выхода элемента ИЛИ-НЕ 14. Номера ячеек блока 6 оперативной памяти определяются вторым счетчиком-13 и сумматором 15, которые обеспечивают их рециркуляцию

(фиг.2 г),

Такое накопление сигнала в виде неполной свертки происходит на протяжении всех интервалов времени Т.

кроме to, tj, , когда появляется импульс (фиг.2 д) с выхода элемента ИЛИ-НЕ 14. Этот импульс переводит переключатели блока 5 в другое положений, при котором Uj U)2 0. В результате на протяжении интервала

времени t , происходит запись О в соответствующую ячейку блока 6 оперативной памяти. А в момент времени t (по заднему фронту тактового импульса) из сигнала, записанного в реверсивный счетчик 4, формируется сигнал, соответств ующий полной свертке (т.е. содержащий М слагаемых). В момент времени t по переднему фронту импульса с формирователя 16 (фиг . 2 е) производится суммирование указанного сигнала в сумматоре 7 с накопленньм в нем сигналом, а по заднему фронту импульса с формирователя 16 (в момент времени t) - суммирование выходного сигнала сумматора 7 с предьщущим отсчетом выходного сигнала фильтра в сум - маторе 8. Таким образом, в сумматоре 8 формируется текущий отсчет выходного сигнала фршьтрации в фор- мате импульсно-кодовой модуляции. При помощи ЦАП 9 сигнал у | преоб

в аналоговую форму y(t).

Таким образом, при выборе количества коэффициентов М 2. схема фильтра упрощается за счет того, что блоки 12 и 13 могут представлять собой k-разрядные счетчики с парал

лельным выходньм кодом, а блок 15 - 2k-BxoAOBoft полный сумматор.

Формула изобретени

Цифровой фильтр с дельта-модуляцией, содержащий линейный дельта- модулятор, выход которого соединен с первым входом элемента эквивалентности, выход которого соединен со счетным входом реверсивного счетчика, выходы которого подключены к первым входам блока переключателей, выходы блока переключателей соединены с информационными входами блока оперативной памяти, выходы которого подключены к установочным входам реверсивного счетчика, блок постоянной памяти, выход которого соединен с вторым входом элемента эквивалент- ности, первый и второй сумматоры, цифроаналоговый преобраэователь и блок управления, информационный вход линейного дельта-модулятора является входом фильтра, отличающий- с я тем, что, с целью упрощения .фильтра при числе коэффициентов им- пульсной характеристики 2, (k - целое число, блок .управления выполнен на счетчиках, сумматоре, формирова- теле импульсов, элементе ИЛИ-НЕ и тактовом генераторе, выход которого подключен к счетному входу первого счетчика, тактовому входу формировате188

ля Iiмпyльcoв И к управляющ11м входам реверсивного счетчика и блока оперативной памяти, выходы разрядов первого счетчика подключены к первым входам сумматора, входам элемента ИЛИ-Н и к адресным входам блока постоянной памяти, выход переполнения первого счетчика соединен со счетным входом второго счетчика и тактовым входом линейного дельта-модулятора, выходы второго счетчика соединены с вторыми входами сумматора, выходы которого подключены к адресным входам блоке оперативной памяти, выход элемента ИЛИ-НЕ подключен к информационному входу формирователя импульсов и к управляющему входу блока переключателей, вторые информационные входы которого подключены к источнику логического нуля, выход формирователя импульсов соединен с входами синхронизации первого и второго сумматоров, первые информационные входы первого сумматора подключены к выходам реверсивного счетчика, выходы первого сумматора подключены к его вторым информационным входам и к первым ин- формационнь1м в ходам второго сумматора, выходы которого подключены к его вторым информационным входам и входам цифрраналогового преобразователя, выход которого является выходом фильтра.

tpuz.Z

Составитель О.Ревинский Редактор И.Шулла Техред А.Кравчук Корректор С.Черни

Заказ 5128/52 Тираж 899Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035,Москва, Ж-35, Раушская наб., д.4/5

Лроизводственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фильтр с дельта-модуляцией | 1987 |

|

SU1418908A1 |

| Анализатор активности непрерывных сигналов | 1989 |

|

SU1658386A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1987 |

|

SU1481893A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1987 |

|

SU1425841A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1986 |

|

SU1424119A1 |

| Цифровой фильтр с дельта-модуляцией | 1988 |

|

SU1527713A1 |

| Цифровой фильтр | 1986 |

|

SU1387174A1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1987 |

|

SU1494210A1 |

| Цифровой фильтр с симметричной импульсной характеристикой | 1987 |

|

SU1495979A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1988 |

|

SU1589383A1 |

Изобретение относится к вычислительной технике. Его использование в системах цифровой обработки случайных процессов позволяет упростить фильтр, если число коэффициентов импульсной характеристики 2 , где k - целое число. Цифровой фильтр содержит линейный дельта-модулятор 1, блок 2 постоянной памяти (хранящий коэффициенты), элемент 3 эквивалентности, реверсивный счетчик 4, блок 5 переключателей, блок 6 рперативной памяти, сумматоры 7 и 8, цифроанало- говый преобразователь 9 и блок 10 управления. Выполнение блока 10 на тактовом генераторе 11, счетчик 12 и 13, элементе 14 ИЛИ-НЕ,,сумматоре 15 и формирователе 16 импульсов обеспечивает упрощение схемы фильтра. 2 ил. с (Л со 1 00 СХ) ю

| Электроника, 1977, т.50, № 21, с.42, рис.9 | |||

| Патент США 4167731, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Погрибной В.А | |||

| Бортовые системы обработки сигналов | |||

| - К.: Наукова | |||

| думка, 1984, с,107-108, рис.21. | |||

Авторы

Даты

1987-10-23—Публикация

1985-12-17—Подача