363

равляющего соединены с входом Сброс устройства, информационные входы per гистров соедине1&1 с входами Информация устройства, о т л и ч а ю щ е ес я тем,.что, с целью расширения диапазона формируемых задержек и длительностей импульсов, уменьшения дискретности задания задержки, упрощения программного управления, в него введены четвертый и пятый логические элементы И, четвертый и пятый логические элементы ИЛИ, третья управляемая линия задержки ва формирователя, причем .вход устройства соединен с входом первого формирователя и входом синхронизации задающего генератора, выход которого через второй формирователь соединен с одним из входом четвертого логического элемента И выход которого соединен с одним из входов четвертого логического элемента ИЛИ, а второй вход соединен с входом управления триггера управления и выходом пятого логического элемента ИЛИ, входы которрго соедине.ны с выходами первого и второго логических элементов ИЛИ, третий вход: четп./ вертого логического элемента И соединен с выходом триггера управления и иодним из входов пятого логического элемента И,. второй вход которого соединен с выходом первой управляемой линии задержки, входы управления которой соединены с выходами младших разрядов

регистра задания задержки импульсов а вход - с -выходом .четвертого логического элемента ИЛИ, со вторым входом которого соединены выход первого формирователя и вход третьей управляемой линии задержки, входы управления которой соединены с выходами разрядов с п-го по k-ий, где п число младших разрядов регистра импул.ьсов, равное количеству управляющих входов первой управляемой линии задержки, k - порядковый номер разряда регистра задания кода задержки импульсов, принимающий целочисленные значения от 2 до п регистра задания кода задержки импульсов, а выход - с входом установки единичного состояния триггера управления, выход пятого логического элемента И соединен с входом синхронизации счетчика импульсов, вход управления которого соединен с выходом третьего логического элемента И, а вход установки единичного состояния - с входом Сброс устройства, выход первого логического элемента И соединен с. входом установки нулевого состояния триггера формирующего, один из входов установки единичного состояния которого соединен с выходом второй управляемой линии, задержки, второй вход установки единичного состояния с входом Начальная запись устройства, а инверсный выход - с выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемое устройство формирования задержки и длительности импульсов | 1975 |

|

SU545232A1 |

| Многоканальный генератор импульсов | 1977 |

|

SU670067A1 |

| Устройство для задержки импульсов | 1981 |

|

SU993455A1 |

| Устройство для задержки импульсов | 1979 |

|

SU866723A1 |

| Многоканальное устройство для формирования импульсных последовательностей | 1982 |

|

SU1077539A1 |

| Многоканальное устройство для формирования импульсных последовательностей | 1987 |

|

SU1443745A1 |

| Умножитель частоты | 1988 |

|

SU1626315A1 |

| Устройство обработки данных спектрометрического гамма-каротажа | 1985 |

|

SU1285422A1 |

| Многоканальный генератор импульсов | 1980 |

|

SU936400A1 |

| Микропрограммное устройство управления с контролем | 1984 |

|

SU1280627A1 |

ПРОГРАММИРУЕМОЕ УСТРОЙСТВО ФОРМИРОВАНИЯ ЗАДЕРЖКИ.И ДЛИТЕЛЬНОСТИ ИМПУЛЬСОВ, содержащее счетчик импульсов, 'задаюи^ий генератор, управляющий триггер, регистр задания кода задержки импульсов, регистр задания кода длительности задержанных импульсов, формируюпщй триггер, канализирующий триггер, три логических элемента ИЛИ, логический элемент И-НЕ, две управляемые линии задержки, блок перезаписи кода, блок преобразования кода, три логических элемента И, одни из входов первого и второго которых соединены с входом синхронизации счетчика импульсов, а вторые входы соединены с выходом третьего логического элемента И, входы которого соединены с выходами каждого разряда счетчика импульсов, входы установки информа- 'ции каждого разряда которого соединены с выходами блока перезаписи кода, первая группа входов которого соединена с выходами старших разрядов регистра задания кода задержки и входами первого логического элемента ШШ, а вторая группа входов соединена с выходами блока преобразования кода.входы которого соединены с вьтодами старших разрядов регистра задания кода длительности задержанных импульсов и входами второго логического элемента ИЛИ, выход второго логического элемента ИЛИ соединен с управляющим входом триггера канализирующего и одним из входов логического элемента И-НЕ, второй вход которого соединен с третьим входом второго логического элемента И, с инверсным выходом триггера канализирующего и входом разрешения перезаписи кода за*- держки импульса блока перезаписи ко—, да, вход перезаписи кода длительности задержанных импульсов которого соединен с прямым выходом триггера канализирующего, выход логического элемента И-НЕ соединен с третьим входом первого логического элемента И, выход которого соединен с одним из входов третьего логического элемента ИЛИ, выход которого соединен., с входом синхронизации блока перезаписи кода и со счетным входом триггера канализирующего, выход второго логического элемента И соединен с вторым входом третьего логического элемента ШШ, одним из входов установки нулевого состояния триггера управляющего и входом второй управляемой линии задержки, управляющие входы которой соединены с выходами младших разрядов регистра задания кода длительности задержанных импульсов, третий вход третьего логического элемента ШШ соединены с входом "Начальная запись" устройства, вход установки в нулевое состояние триггера канализирующего, а также второй вход установки в нулевое состояние триггера уп-Q<9(ЛО)со(Х>&со00

Изобретение относится к измерительной технике и может быть использовано в, качестве устройства синхронизации больших измерительных систем требующих высокого быстродействия. Известно программируемое устройст во формирования задержки и длительности импульсов, содержащее счетчик импульсов, задающий генератор, триггер управления, вход которого соединен с входом устройства, а выход с задающим генератором. Недостатком устройства являются ограниченные функциональные возможности. Известно также устройство, состоя щее из задающего генератора, счетчика импульсов, регистров задания задержки и длительности формируемых импульсов, триггеров управляющего, канализирующего, формирующего, двух управляемых линий задержки, блока перезаписи кода, блока преобразования кдда,-логических элементов. В этом устройстве в 1,11 и TII режимах работы, в которых формирование задержки и длительности импульсов происходит при помощи счетчика импульсов и соответствующей управляемой линии задержки, запрет задающего генератора после того, как он выдал импульс, по которому счетчик срабатывает последний раз, происходит через время восстановления, равное .

Так как к приходу следующего входного запускающего импульса задающий генератор должен находиться в запре.щенном состоянии, величина программируемых задержек и длительностей импульсов не может быть более, чем

5-VTex- 6Это условие приводит к сужению диапазона формируемых задержек и длительностей импульсов в этих режимах. В 1,11 и III режимах работы величина задержки, которую можно запрограммировать на первой управляемой линии задержки, не может быть более, чем

AJI T --O

В противном случае задающий генератор запретится на такт позже по отношению к импульсу, по которому происходит последнее срабатывание счетчика импульсов, что приводит к сбою в работе устройства. Поэтому, если программируемая задержка импульса удовлетворяет условию .

Тг-п6Тг(п+1)-С(,, где ,1,2,3,..., . то она может задаваться с любой малой дискретностью, определяемой дискретностью первой управляемой линии задержки. Если же программируемая задержка импульса удовлетворяет условию

Тр-п-С„ Т ТгП,

то она может задаваться с определенной дискретностью.

Программное управление устройством затруднено, так как информация о величине Г t заносимая в регистры, поразрядно делится на две части, каждая из которых вычисляется отдельно. Поэтому информационное слово, заносимое в регистры, не совпадает с двоичным эквивалентом про-граммируемой величины.

. Цель изобретения - расширение ,, диапазона формируемых задержек и длительностей импульсов, уменьшение дискретности задания задержки импульсов, упрощение программного управления..

Для дoctижeния цели в устройство, содержащее счетчик импульсов, задающий генератор, триггер управления, регистр задания кода задержки импульсов, регистр задания кода длительности задержанных импульсов, формирующи триггер, канализирующий триггер, три логических элемента ИЛИ, логический

элемент И-НЕ, две управляемых линии задержки, блок перезаписи кода, блок преобразования кода, три логических элемента И, один из входов первого и второго которых соединены с входом синхронизации счетчика импульсов, а вторые входы соединены с выходами каждого разряда счетчика импульсов,

0 входы установки информации каждого разряда которого соединены с выходами блока перезаписи кода, первая группа входов которого соединена с . вьгходами старших разрядов регистра задания кода задержки и входами первого логического элемента ИЛИ, а вторая группа входов соединена с выходами блока преобразования кода, входы которого соединены с выходами старших разрядов регистра задания кода длительности задержанных импульсов и входами второго логического элемента ИЛИ, выход второго логического эле-г, мента ШШ соединен с управляющим

5 входом канализирующего триггера и одним из входов логического элемента И-НЕ, второй вход которого соединен с третьим входом второго логического элемента И, с инверсным входом канализирующего триггера и входом разрешения перезаписи кода задержки импульса блока перезаписи кода, вход перезаписи кода длительности задержанных импульсов которого соединен

g с прямым выходом канализирующего триггера, выход логического элемента И-НЕ соединен с третьим входом первого логического элемента И, выход которого соединен с одним из входов

0 третьего логического элемента ИЛИ, выход которого соединен с входом синхронизации блока перезаписи;кода и со счетным входом канализирующего триггера, выход второго логического

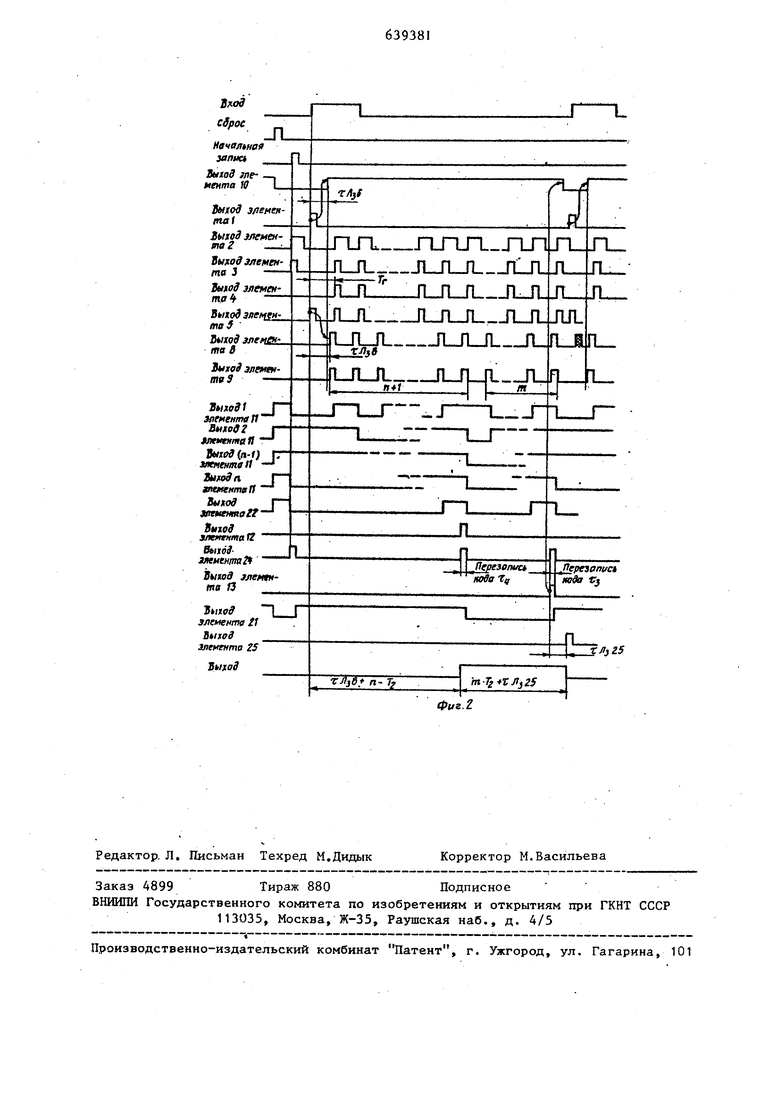

5 элемента И соединен с вторым входом третьего логического элемента ИЛИ одним из входов установки нулевого состояния управляющего триггера и входом второй управляемой линии задержки, управляющие входы которой соединены с выходами младших разрядов регистра задания кода длительности задержанных импульсов, третий вход третьего логического элемента ИЛИ соединен с входом Начальная запись устройства, вход установки в нулевое состояние катализирующего триггера, а также второй вход установки в .нулевое состояние управляющего триггера 76 соединены с входом Сброс устройства, информационные входы регистров соединены с входами Информация устройства, в него введены четвертьй и пятый логические элементы И, четвертьй и пятьй логические элементы ИЛИ, третья управляемая линия задержки, два формирователя, причем вход устройства соединен с входом первого формирователя и входом синхронизации задающего генератора, выход которого через второй формирователь соединен с одним из входов четвертого логического элемента И, выход которого, v соединен с одним из входов четвертого логического элемента ИЛИ, а второй вход соединен с входом управления управляющего триггера и выходом пятого логического элемента ИЛИ, вхо ды которого соединены с выходами пер вого и второго логических элементов ИЛИ, третий вход четвертог о логического элемента И соединен с выходом управляющего триггера и одним из вхо доз пятого логического элемента И, второй вход которого соединен с выходом первой управляемой линии задержки, входы управления которой сое .динены с выходами младших разрядов регистра задания кода задержки импульсов, а вход - с выходом четверто го логического элемента ШШ, с вторы входом которого соединены выход пер: вого формирователя и вход третьей управляемой линии задержки, входы уп равления которой соединены с выходами разрядов с п-го по k-ый, где п число младших разрядов регистра зада ния кода задержки импульсов, равное количеству управляющих входов первой управляемой линии задержки, k-порядковый номер разряда регистра задания кода задержки импульсов, приниг. мающий целочисленные значения от 2-х до п,. регистра задания кода задержки импульсов, а выход - с входом;установки единичного состояния управляющего триггера, выход пятого логического элемента И соединен с входом синхронизации счетчика импульсов, вход управления которого соединен с выходом третьего логического элемента И, а вход установки единичного состояния - с входом Сброс устройства, выход первого логического элемента И соединен с входом установки нулевого состояния формирующего триг гера, один из входов установки едиг ничного состояния которого, соединен с выходом второй управляемой линии задержки, второй вход установки единичного состояния - с входом Начальная запись устройства, а инверсный выход - с выходом устройства. На фиг, 1 представлена функциональная схема устройства; на фиг,2 временные диаграммы, поясняющие его работу. Устройство содержит счетчик I импульсов, задающий генератор 2, управляющий триггер 3, регистр 4 задания кода задерзди импульсов, регистр 5 задания кода длительности задержанных импульсов, формирующий триггер 6, канализирующий триггер 7, логические элементы ИЛИ 8-10, логический элемент И-НЕ 11, две управляемые линии 12 и 13 задержки, блок 14 перезаписи кода, блок 15 преобразования кода, логические элементы И 16-19, четвертый и Пятый логические элементы ИЛИ 20, 21, третью управляемую Линию 22 задержки, два формирователя 23, 24. Устройство работает следующим образом. Задержка импульсов формируется на двух элементах путем сложения задержек каждого из этих элементов: на управляемой линии 22 задержки и счетчике 1 импульсов. Каждая из составляющих общей задержки задается програмным путемУ на управляемой линии 22 задержки с минимальной выбранной дискретностью, на счетчике I импульсов с дискретностью, равной периоду задающего генератора 2, Аналогично фррмируется и длителльность задержанного импульса на том же счетчике 1 и управляемой линии 13 импульсов задержки. Для упрощения программного управления устройством необходимо выбирать значения задержки калодого из разрядов управляемой линии задержки в соответствии с весовыми коэффициентами двоичного кода,, а значение периода задающего генератора в два раза больше значения старшего разряда управляемой линии задержки. Например,при выбранной минимальной дискретности устройства, равной 1 НС, и четырехразрядных управляемых линиях 22 и 13 за- . держки значение задержек разрядов с первого по четвертый выбирается равным соответственно 1 не, 2 не, 4 НС, 8 НС. А значение периода задающего генератора 2 - равным 16 не. В этом случае максимальная величина задержки, задаваемая на управляемой линии задержки, меньше периода задаю щего генератора 2 на величину минимальной дискретности устройства. В известном устройстве выполнение этого ограничивается быстродействием входящих элементов в соответствии с условием. Введение на выходе управ ляемой линии 22 задержки элемента ИЛИ 21, управляемого от триггера 3 управления, позволяет выбирать макси мальное значение задержки, задаваемо на управляемой линии 22 задержки н широких пределах, в том числе равньгх и больших периода задающего генератора 2, Это позволяет упростить программное управление устройством и за держку импульсов задавать с минимальной дискретностью на всем рременном интервале, определяемом периодом i входных запускающих импульсов. Программное управление устройство в приведенном примере сводится к пег реводу задаваемой величины в двоичны код и занесению этого кода в соответ ствующий регистр: при задании задерж ки импульсов - в регистр 4 и при задании длительности задержанного импульса - в регистр 5. В случае, когда задаваемая величина о и Сц. равна или больше периода задающего генератора, в разряды регистров 4 и 5, управляющие работой счетчика 1 импулы сов, заносится информация, отличная от нуля. Когда же б и о -меньше периода задающего генератора, заносится нулевая информация, В связи с эти можно выделить четыре режима работы устройства: Рассмотрим работу устройства в I режиме. Устройство приводится в начальное состояние путем подачи импульсных сигналов на вход Сброс, а затем на вход Начальная запись. Импульсным сигналом Сброс управляющий регистр 3 и триггер 7 канализирующий приводятся в состояние О, счетчик 1 приводится в состояние 1. Затем в регистры 4 и 5 заносится информация о величине и С, после чего на вход Начальная запись подается импульсный сигнал, так как элемент ШШ 21 находистя в состоянии О, то на выходах элементов 16 и 17 также находится логический уровень О,поступающий на первый и второй входы элемента 10, поэтому импульсный сигнал Начальная запись, поступающий на третий вход элемента 10, проходит на выход элемента ИЛИ 10 и поступает на входы синхронизации блока 14 перезаписи кодов и триггера 7, канализирующего перезапись кодов, Так как канализирующий триггер 7 находится в : ; О, то уровень логический состоянии )t I It с его инверсного выхода поступает на вход разрешения перезаписи кода задержки, поэтому импульс, поступающий на вход синхронизации блока 14 перезаписи с выхода элемента 10, про изводит перезапись кода с регистра 4 . на счетчик 1, код устанавливается на инверсных выходах счетчика I, соответственно на прямых выходах счетчика 1 устанавливается код, обратный коду, записанному в регистр 4. По срезу импульса, поступающего с выхода элемента I О, канализирующий триггер 7 переводится в состояние I, Формирующий триггер 6 импульсом , Начальная установка переводится в состояние О на инверсном выходе, В этом состоянии устройство готово к работе. Так как в первом режиме работы устройства в разряды регистров 4 и 5, управляющих работой счетчика 1, записывается информация, от- личная от нуля, то на выходах элементов ИЛИ 8 и 9 находится потенциал логической 1, с выхода элемента . ИЛИ 9 этот потенциал поступает на вход разрешения контактирующего триггера 7, при поступлении на вход разрешения потенциала логической 1 триггер 7 работает как обычный счетчик-триггер на выходе элемента ИЛИ 21 потенциал логической 1, так как на первом и втором его входах потенциалы логической 1, этот потенциал поступает на второй вход элемента ИЛИ 20 и на вход управления управляющего триггера 3, при поступлении на вход управления управляющего триггера 3 уровня логической 1 он работает как обычный R-S-триггер, Входной запускающий импульсный сигнал с входа устройства поступает на .вход синхронизации задающего генератора 2 и вход формирователя 23, на выходе которого формируется короткий импульсный сигнал положительной полярности, соответствующий во времени фронту входного сигнала, Задающий генератор 2 работает в режиме непрерывной генерации с привязкой фазы генерации к фронту вхрдного запускающего инпульса. Эта привязка осуществляется путем запрета генерации по приходу фронта впускающего импульса на вход синхронизации генератора на время, равное одному периоду, после чего возобновляется )непрерывньш режим генерации, С выхода генератора 2 импульсы поступают на вход 24 формирователя, на выходе которого формируются короткие импульсные сигналы положительной полярности. С выхода формирователя 23 импульсный сигнал по- ступ.ает на вход yпpaвJiЙ eмoй линии 12 задержки и на второй вход злемента ИЛИ 20, На первом входе злемента ШШ 20 в этот момент времени находится уровень логического О, поступающий на вход этот с выхода элемента ИЛИ 20, на третий вход которого пост пает уровень логического О с выхода управляющего триггера 3, Поэтому импульсный сигнал, поступивший на ; второй вход элемента ИЛИ 20, проходи на его выход. Импульсный сигнал, пос тупивший на вход управляемой линии I задержки задержавшись на время, запрограммированное разрядах с п-го по k-ый регистра 4, поступает на вход установки .единицы управляющего триггера 3 и переводит его в состояние логической 1 по выходу. Так .как на входы управления линии 12 задержки заведена часть младших разрядов реги стра 4, то импульсный сигмал задержи вается на линии 12 задержки на время с гарантией меньше, чем на линии 22 задержки. Даже, если в k младших раз рядах регистра 4 запрограммирована нулевая задержка, уровень логической 1 на первом входе элемента , ИЛИ 21 и третьем входе элемента ИЛИ 20 устанавливается на время, равное собственной задержке линии 22 задерж ки, раньше, чем импульсный сигнал с формирователя 23, пройдя через элемент ИЛИ 20 и линию 22 задержки, пос тупит на второй вход элемента ШШ 21 Уровень логической 1, поступая на третий вход элемента ИЛИ 20, разреша ет прохождение импульсных сигналов с задающего генератора 2 через форми рователь 24 и логический элемент ИЛИ 20 на первый вход элемента ИЛИ 20, начиная с первого импульсного сигнала, синхронизированного по фронту входного запускающего импульса. С выхода элемента ИЛИ 20 импульсная последовательность, первый импульс которой образован импульсом с выхода формирователя 23, а последующие импульсами с выхода формирователя 24, поступает на вход управляемой линри 22 задержки. Задержавшись на управляемой линии 22 задержки на время, запрограммированное в младших разрядах регистра 4 и кратное минимальной дискретности устройства, импульсная последовательность, пройдя через элемент ИЛИ 21, на первый вход которого поступает разрешающий уровень логической 1. с выхода управляющего триггера 3, поступает на вход синхронизации счетчика -1 и первые входы . элементов И 16 и 17. Так как на прямых выходах счетчика 1 находится код, обратный коду, записанному в старшие разряды регистра 4, управляющие работой счетчика импульсов 1, то для того, чтобы перевести счетчик в состояние I по всем выходам, на его вход синхронизации необходимо подать количество импульсов, равное числу, записанному в старшие разряды регистра 4. Допустим в эти разряды записано число п, тогда с приходом п-го импульса на вход синхронизации счетчика 1 он переходит в состояние 1 по всем выходам, поэтому на выходе элемента И 18 уста-навливается потециал логической 1, поступающий на вторые входы элементйв И 16 и 17 и на вход управления счетчика 1 импульсов. При поступлении на .вход управления счетчика 1 импульсов уровня логической 1 он останавливает счет, при поступлении уровня логического О разрешается, работа счетчика по входу синхронизации. На третий вход элемента И 1 7 подается с .инверсного выхода канализирующего триггера 7 потенциал логического О, поступающий также на второй вход элемента И-НЕ 11, на первьш вход этого /элемента подается потенциал логической I с выхода элемента И 17. С выхода элемента И-НЕ 11 в потенциалллогической 1 поступает на третий вход элемента И 16. На втором и третьем входе элемента И 16 установились уровни ло 136 1, поэтому (п+1)-ый имгическойпудьс импульсной последовательности проходит через элемент 16 и поступает на вход установки нуля триггера 6 формирующего, переводя его в состояние логической 1 на инверсном выхо де, и. на первый .;вход элемента ИЛИ 21 Так как (п+1)-ьй импульс во времени сответствует п периодам тактовой час тоты задающего генератора 2, то на ; счетчике формируется временная задержка, кратная периоду задающего ге нератора, причем кратнойть равна чис лу,, записанному в разряды регистра, управляющие работой счетчика импульсов 1 . На этом заканчивается первый цикл работы устройства - цикл формирования задержки импульсов, Так как на втором и третьем входах элементов ИЛИ 10 находится потен циал логического О, то импульс, поступающий на его первый вход с выходм элемента И 16, проходит на входы синхронизации канализирующего триггера 7, канализирующего перезапись, и блока 14 перезаписи, канализирующий триггер 7 в этот момент времени находится в состояние I, поэтому разрешается перезапись кода длительности с регистра 5 на счетчик 1 , эта перезапись во времени осущеГ ствляется между (п+1) и (п+2) тактами импульсной последовательности. Но после этого же импульсного сигнала канализирующий триггер 7 переходит в состояние логического Q. Перезапись кода осуществляется следующим образом: с поступлением импульсного сигнала на вход синхронизации блока перезаписи кода на его выходах, соединенных с входами установки информа ции счетч-ика 1 импульсов, появляются импульсные сигналы. Счетчик в этот момент времени находится в состояние логической 1 по всем выходам и если в разряде регистра, с которого производится перезапись в данный раз ряд счетчика, занесена информация О О, то импульсы, поступающие на вхо подтвержды установки счетчика, дают состояние 1 разряда счетчика, если же в этом разряде регистра зане сена информация 1, то соответствующий разряд счетчика переводится в состояние логического О по выходу. На счетчике устанавливается код, обратный коду, занесенному в ре 1 гистр, с которого производилась перезапись. Если в старшие разряды регистра 5 записано число т, то это число, поступая на преобразователь кода 15, уменьшается на единицу, на выходе преобразователя кода получается число (т-1), это число записывается на счетчике 1 в обратном коде. Так как в первом режиме работы число m отлично от нуля, то на счетчике 1 импульсов устанавливается код, отличный от единицы по всем разрядам, поэтому на выходе элемента И 18 устанавливается уровень логического О, поступающий на вход управления счетчика 1 импульсов, разрешая его работу по входу синхронизации. Начиная от момента поступления (п+2) импульс импульсной последовательности на счетчике 1: ПРО.ИСХОДИТ отсчет (т-1) периодов частоты генератора 2, аналогично как и при отсчете числа, записанного в старшие разряды регистра 4, Так как период, во время которого происходит перезапись кода длительности импульса с регистра 5 на счетчик 1, между (п+1) и (п+2) тактами генератора 2 автоматически включается во второй цикл работы устройства - цикл, формирования, длительности задержанного импульса, то на выходе элемента 17, на третий вход которого поступает потенциал логической 1 с инверсного выхода канализирующего триггера 7, импульсный сигнал появляется через время, равное m периодам частоты генератора 2 от момента перехода триггера 6 формирующего из сос тояния О в состояние 1 на инверсном выходе в цикле формирования задержки импульса. С выхода элемента И 17 импульс поступает на вход управляемой линии 13 задержки, второй вход элемента ИЛИ 10 и вход установки триггера 3 управления. Поступив на управляемую линию 13 задержки, импульсный сигнал задерживается на время, запрограммированное в младщих разрядах регистра и кратное минимальной дискретности устройства. С выхода управляемой линии задержки импульсный сигнал поступает на вход Установки 1 формирующего триггера 6, переводя его в состояние логического О на инверсном выходе, Поступив на второй вход элемента ИЛИ 10, импульсный сигнал с выхода элемента И 17 проходит через элемент ИЛИ 10

и поступает на входы синхронизации блока 14 перезаписи кода, производя перезапись кода со старших разрядов регистра 4 на счетчик 1 импульсов, с и на вход синхронизации канализирующего триггера 7, канализирующе го пе резапись кодов, переводя его по срезу импульсного сигнала в состояние логической 1 (так как до этого Q он находился в состоянии логического О), Поступив на вход установки О управляющего триггера 3, импульсный сигнал с выхода элемента И 17 переводит его в состояние логического 15 О по выходу. Нулевой логический уровень устанавливается на третьем входе элемента И 20, запрещая прохождение тактовой частоты с задающего генератора 2, и на первом входе эле- 20 мента ИЛИ 21, запрещая прохождение сигналов с выхода управляемой линии

22 задержки на входы синхронизации счетчика 1, Так как величина запро-. граммированной задержки на управляе- 25 мой линии задержки может быть близкой к величине периода задающего генератора (например, быть на величину минимальной дискретности устройства ме меньше его), то с учетом собственных ЗО задержек элементов 4, 5, 8, 9, 10 и 13 запрет на третьем входе элемента ИЛИ 20 установится позже, чем через него пройдет и поступит на вход управляемой линии задержки очередной ,

импульс с генератора 2, следующий за импульсом, по которому произошло последнее срабатывание счетчика в ццкле формирования длительности задержанного импульса. Но на вход син- дд хронизации счетчика импульсов 1 этот импульс не пройдет, так как, задержавшись на управляемой линии 22 задержки, он поступает на второй вход элемента ШШ 21, на первом входе ко- дд торого уже установился запрещающий уровень логического О, поступающий с выхода триггера 3 управления. ,С приходом последующих запускающих импульсов на вход устройства оба цик- ,„ ла: цикл формирования задержки импульса и цикл формирования длительности задержанного импульса, повторяются. Причем, если запрограммированные величины Cl и . таковы, что к приходу следующего запускающего импульса на вход устройства, на управляемой ..линии задержки еще не закончился процесс прохождения послед-.

него импульсного сигнала в цикле формирования длительности задержанного импульса, то это не вызовет сбой в работе устройства, так как управляющий триггер 3 переводится в состояние логической 1 и разрешает прохождение сигналов с выхода элемента 22 на вход элемента 1 по отношению к фронту входного запускающего импульса с задержкой программируемой на управляемой линии 12 задержки. Введение управляемой линии 12 задержки снимает ограничение на диапазон задаваемых величин С. иоф. Требования к точности задания задержек и дискретности для управляемой линии задержки в несколько раз ниже, чем для управляемых линий 22 и 13 задержки, на которых собственно формируются ut . Временная диаграмма работы устройства в первом режиме показана на фиг.2. Условно показано, что в разряды регистра 4, управляющи работой счетчика 1, занесено число 10...01, а в разряды регистра 5, управляющие работой счетчика 1 через преобразователь 15 кода, число 11... .11 (младшие разряды слева).

Во(втором режиме работы в регист 4, в разряды, управляющие счетчиком, заносится нулевая информация, так какС, Tj., поэтому, с приходом импульса Начальная запись на прямых выходах счетчика устанавливается информация 11... 1. . С приходом входног запускающего импульса аналогично, как и в первом режиме работы, им- . п:ульсная последовательность с выхода элемента ИЛИ 20 поступает на- вход управляемой линии 22 задержки. Первый же импульс этой импульсной последовательности, поступающий на вход элемента ИЛИ 20 с выхода формирователя 23, пройдя через управляющую линию 22 задержки, и,задержавшись на ней на время, запрограммированное в младших разрядах регистра 4, через элемент ИЛИ 21, элемент И 16, поступит на вход установки нуля триггера формирующего, переводя его в состояние логической 1 на инверсном выходе, и через элемент ИЛИ 10 на вхо-ды синхронизации блока 14 перезаписи кодов и триггера 7, осуществляя перезапись кода длительности задержанного импульса со старших разрядов регистра 5, через преобразователь кода ,1 5 на счетчик импульсов 1, перево17дя канализирующий триггер 7 в противоположное состояние. Таким образом осуществляется формирование задержки импульса-, величина которой не более Т. Формирование длительности задержанного импульса происходит так же, как в первом режиме работы, В третьем режиме работы в регистр 5 в разряды, управляющие работой I . счетчика 1, записана нулевая информация, так как сТ.., поэтому на вып ходе элемента 9 находится потенциал логического нуля, этот потенциал поступает на вход разрешения триггера 7, ..канализирующего перезапись, запрещая его работу по входным сигналам синхронизации. После установки канализирующего триггера 7 в состояние О сигналом Сброс он будет находиться в этом состоянии все время работы устройства и с приходом импульсных сигналов с выхода элемента 10 будет осуществляться в каждом цикле перезапись только кода задержки с регистра 4 на счетчик , На тре тьем входе элемента I7 все время работы устройства находится потенциал логической 1, поступающий с инверс ного плеча триггера 7, На третьем входе элемента 16 также находится по тенциал логической 1, поступающий с выхода элемента 11, на первом входе которого все время работы находит ся потенциал логического О, поступающий с выхода элемента 9, Допустим в разряды регистра 4, управляющие работой счетчика, записано число п, с приходом п+1 импульса на вход син хронизации счетчика 1, импульсньй . сигнал вьщеляется одновременно на выходах элементов 16 и 17, с выхода элемента 16 импульсньй сигнал поступает на вход установки нуля формирующего триггера 6, таким образом, цикл формирования задержки в этом ре жиме такой же, как и в первом режиме работы. Импульсный сигнал с выхода .. элемента 16 поступает на вход управляемой линии 13 задержки, задерживается на нем на время, запрограммированное в младших разрядах регистра 5 кратное -минимальной дискретности устройства, .величина этой задержки меньше Тр, и с выхода линии 13 задержки поступает на вход установки единицы формирующего триггера 6. Импульсный сигнал с выхода элемента 17 поступает так же на вход установки 1 нуля триггера 3 управления, и. пройдя через элемент ИЛИ IQf на перезапись кода задержки на блок перезаписи, производя перезапись кода задержки со старших разрядов регистра 4 на счетчик 1 импульсов, В четвертом режиме работы в старшие разряды регистров 4 и 5, управляющие работой счетчика 1 импульсов, записана нулевая информация, так как .. и €ц. Tf . На выходе элемента ИЛИ ИЛИ 2Г устанавливается потенциал логического О, поступающий на вход управления управляющего триггера 3 и второй вход элемента ИЛИ 20, запрещая прохождение тактовой частоты с генератора 2 через формирователь 24, элемент ИЛИ 20 и элемент ИЛИ JO на вход управляемой линии 22 задержки, Уровень логического О, поступая на од управления управляющего триггера 3, удерживает его в состоянии логической 1 на выходе независимо от сигналов, поступающих на входы установки единицы и нуля, -Уровень логи-г ческой 1 с выхода триггера управления поступает на первый вход эле--, мента ИЛИ 21, разрешая прохождение импульсного сигнала с формирователя 23 через элемент ИЛИ 20 и управляемую линию 22 задержки на входы элементов И 16,и 17 и вход синхронизации счетчика 1 импульсов. Состояние по входам элементов 16, 17 и 11 такое же, как и в третьем режиме работы. Счетчик 1 все время работы находится в состоянии 11..I по прямым выходам, так как на него в обратном коде перезаписывается содержимое старших разрядов регистра 4. Поэтому импульсный сигнал, пройдя через упрявляемую линию 22 задержки и задержавшись на время, запрограммированное в младших разрядах регистра 4, выделяется на выходах элементов 16 и 17. С выхода элемента 16 этот сигнал поступает на вход установки нуля формирующего : триггера 6 с выхода элемента 17 через управляемую линию задержки, задержав-;: шись на ней на время, запрограммированное в младших разрядах регистра 5, на вход установки единицы формирующего триггера 6. Поступив на вход установки единицы формирующего триггера 6, импульсный сигнал переводит его в состояние логического на инверсном выходе независимо от того, окончился импульсный сигнал на -входе

устанрвки нуля формирующего триггера 6 или нет. Это. позволяет формировать в четвертом режиме работы задержанные импульсы минимальной длительности.

Устройство обеспечивает программное задание задержки и длительное ти импульсов на диапазоне, опJ.aefl)f4Jij

ределяемом периодом входных запускающих импульсов, с дискретностью в единицы и доли наносекунд. Программное управление устройством простое и удобное при использовании его в автоматизированных контрольно-измерительных системах, управляемых от ЭВМ с помощью специализированного языка общения ЭВМ с системой.

| Устройство задержки | 1972 |

|

SU442575A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-07-15—Публикация

1977-01-03—Подача