иен с третьим входом третьего логнческоро элемента И, вторым входом логического элемента И-НЕ и входом разрешения перезаписи кода задержки импульсов блока перезаписи кодов, вход разрешения перезаписи кода длительности импульсов которого соедине с прямым выходом триггера канализирующего, R вход которого соединен с S входом счетчика, входной шиной Сброс Их вторым входом триггера синхронизации 5 вход которого соединен через третью линию задержки с вторым входом третьего логического элемента ИЛИ, а выход триггера синхронизации соединен с вторым входом второго логического элемента И, входы управления первой и третьей линии задерж ки соответственно соединены с выходами младших разрядов и выходами старших разрядов в группе младших разрядов датчика кода задержки им- пульсов, входы управления второй линии задрежки соединены с выходами младших разрядов датчика кода дли тельности импульсов, а в каждом из n-m каналов выходы старших разрядов датчика кода задержки импульсов соединены с установочными входами счетчика и через последовательно соединенные первый логический элемент ИЛИ 6 первый логический элемент И, второй логический элемент ИЛИ - с тактовым входом счетчика и через второй логический элемент И - с первым входом синхронизации счетчика, первым R входом триггера синхронизации и через линию задержки - с R входом триггера выходного, первый S вход которого через первую схему задержки соединен с его выходом, а второй S вход - с входной шиной Сброс и вторым R входом триггера синхронизации, S вход которого через вторую схему задержки соединен с вторым входом второго логического элемента ШТИ,- выходы счетчика через третий логический элемент И соединен с вторым входом второго логического элемента И и входом управления счетчика, второй вход синхронизации которого соединен с входной шиной Запись, входы управления линии задержки соединены с выходами младших разрядов датчика кода задержки, при этом выход фазируемого генератора импульсов соединен с третьим входом каждого первого логического элемента И, а выход формирователя соединен с вторым входом третьего и второго логических элементов ИЛИ соответственно в m и n-m каналах.

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемое устройство формирования задержки и длительности импульсов | 1977 |

|

SU639381A1 |

| Программируемое устройство формирования задержки и длительности импульсов | 1975 |

|

SU545232A1 |

| Устройство для задержки импульсов | 1981 |

|

SU993455A1 |

| Многоканальный генератор импульсов | 1980 |

|

SU936400A1 |

| Устройство для задержки импульсов | 1979 |

|

SU866723A1 |

| Многоканальное устройство для формирования импульсных последовательностей | 1982 |

|

SU1077539A1 |

| Многоканальное устройство для формирования импульсных последовательностей | 1987 |

|

SU1443745A1 |

| Устройство для преобразования телевизионного стандарта | 1986 |

|

SU1343562A1 |

| УСТРОЙСТВО ФАЗИРОВАНИЯ ШКАЛЫ ВРЕМЕНИ ЭЛЕКТРОННЫХ ЧАСОВ | 1994 |

|

RU2084944C1 |

| Преобразователь угол-код | 1988 |

|

SU1596461A1 |

МНОГОКАНАЛЬНЫЙ ГЕНЕРАТОР ИМПУЛЬСОВ! содержащий формирователь и генератор импульсов, входы которых подключень! к сигнальной входной шине, и п каналов, каждый из m которых содержит датчик кода длительности импульсов, датчик кода задержки импульсов, счетчик, триггер синхронизации, выходной и канализирующий триггеры, первую, вторую и третью линии задержки, первый, второй, третий,четвертый и пятый логические элементы И^ первый, второй, тертий, четвертый и пя- тьй логические элементы ИЛИ, а каждый из n-m каналов содержит другие датчик кода задержки импульсов, счетчик, триггер синхронизации, выходной триггер, первую и вторую схемы .за->&,•' держки, линию задержки, первьй, второй и третий логические элементы И, первьй и второй логические элементы ИЛИ, причем в каждом из п каналов выход триггера синхронизации соединен с одним входом первого логического элемента И, отличающийся тем, что, с целью расщирения функциональных возможностей, в каждый из m каналов генератора введены преобразователь кода и блок перезаписи' кодов, J первая группа входов которого соеди-' • нена с выходами старших разрядов дат-^ члка кода задержки импульсов и 'черезпервьй и второй логические элементы ИЛИ - с входом управления триггера синхронизации и через последовательно соединенные первый логический элемент И, третий логический элемент ИЛИ, первую линию задержки, второй логический элемент И - с тактовым входом счетчика, входом третьего логического элемента И и через четвер- тьй логический элемент И - с R-BXO- дом триггера выходного и через чет-г вертый логический элемент ИЛИ - с тактовым входом триггера канализирующего с входом синхронизации блока перезаписи кодов, вторая группа входов которого через преобразователь кода соединена с выходами стар-^- ших разрядов датчика кода длительности импульсов и через пятьй лoгиt ческий элемент.ГРШИ - с вторым входом второго логического элемента ИЛИ, входом управления триггера канали- . зирующего и через логический элемент И-НЕ --С вторым входом четвертого логического элемента И, а выходы блока перезаписи кодов соедиенны с установочными входами счетчика, выходы которого через пятьй логический эле-, мент И соединены с входом управления счетчика, третьим входом четвертого логического элемента И и через второй вход третьего логического элемента И - с первым R входом триггера синхронизации, вюрым входом четвертого логического элемента ИЛИ и через вторую линию задержки - с первым S входом триггера выходного, второй S вход которого соединен с третьим входом четвертого логического элемента ИЛИ. и входной шиной "Запись", инверсньш выход триггера канализирующего соеди-с!бсл05^^ ^

Изобретение относится к импульсной технике, и может быть использовано в вычислительной и контрольно-из- , мерительной технике, в частности, в системах функционального контроля больших интегральных схем (БИС).

Известен многоканальный генератор импульсов,содержащий триггеры, линии задержки, элементы И и ИЛИ.

Недостатком такого устройства является малая точность задания временных параметров выходных импульсов.

Из известных устройств цаиболее близким по технической сущности является многоканальный генератор импульсов, содержащий формирователь и генератор импульсов, и п-каналов каждый из m которых содержит датчик кода длительности импульсов, датчик кода задержки импульсов, счетчик, триггер синхронизации, выходной и канализирующий триггеры, первую, вторую и

I

третью линии задержки, первый, второй

третий четвертый и пятый логические элементы -И, первый, второй, третий четвертый и пятый логические элементы ИЛИ, а каждый из n-m каналов содержит другие датчик кода задержки импульсов, счетчик, триггер синхронизации, выходной триггер, первую и вторую схемы задержки, линию задержки, первый, второй и третий логические элементы И, первый и второй логические элементы ИЛИ, причем в каждом из и каналов выход триггера синхронизации соединен с одним входом первого логического элемента И.

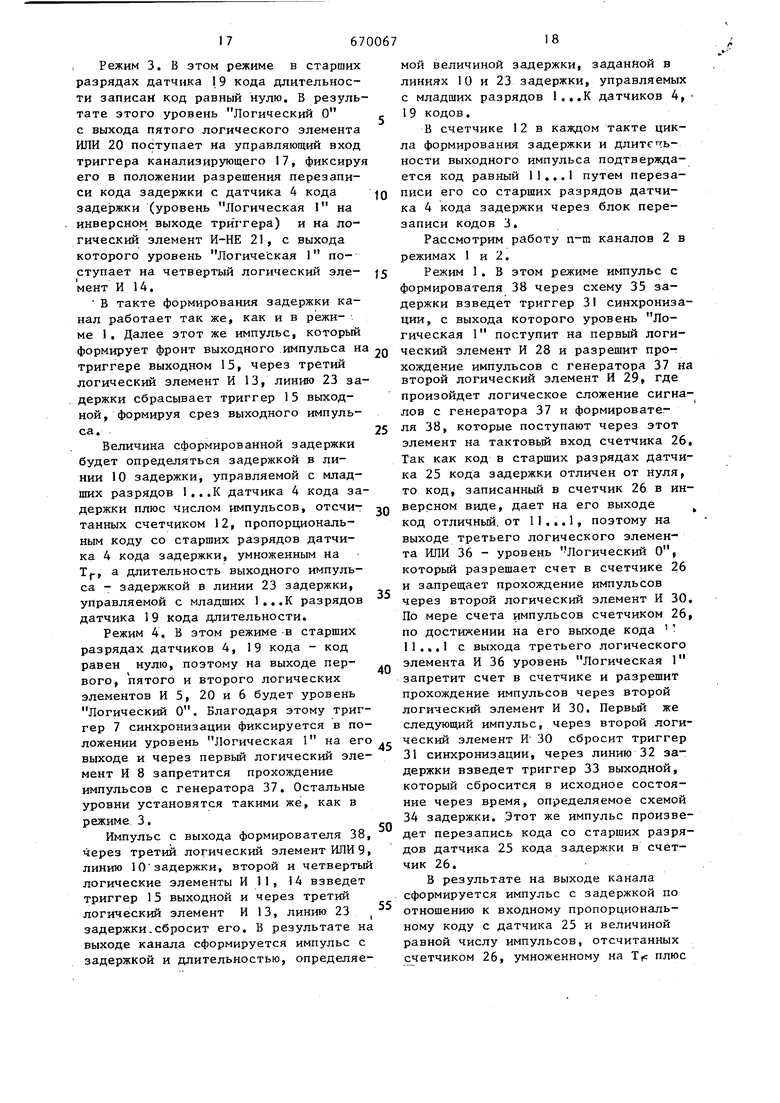

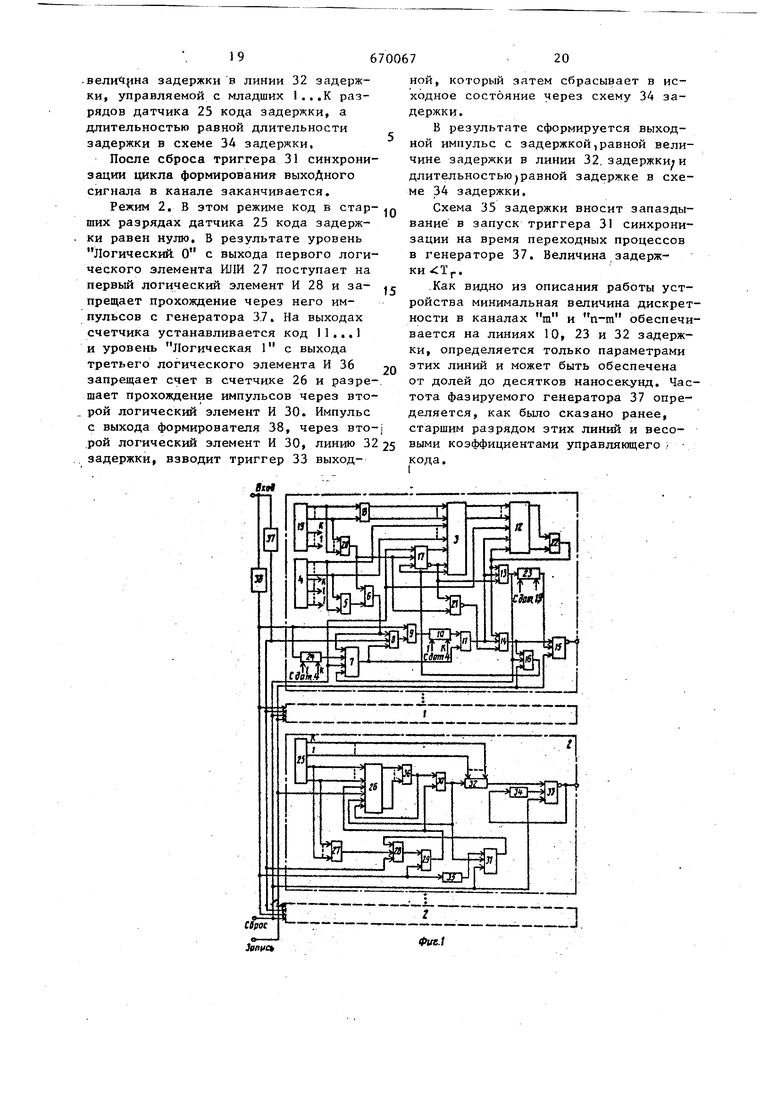

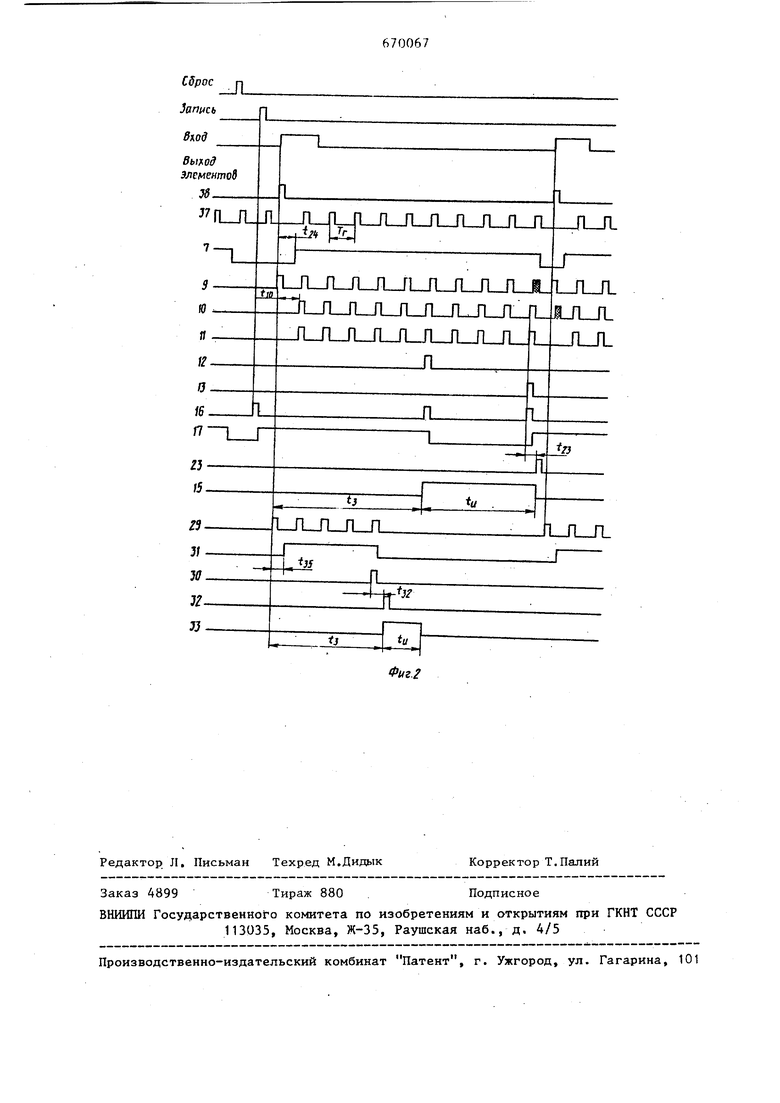

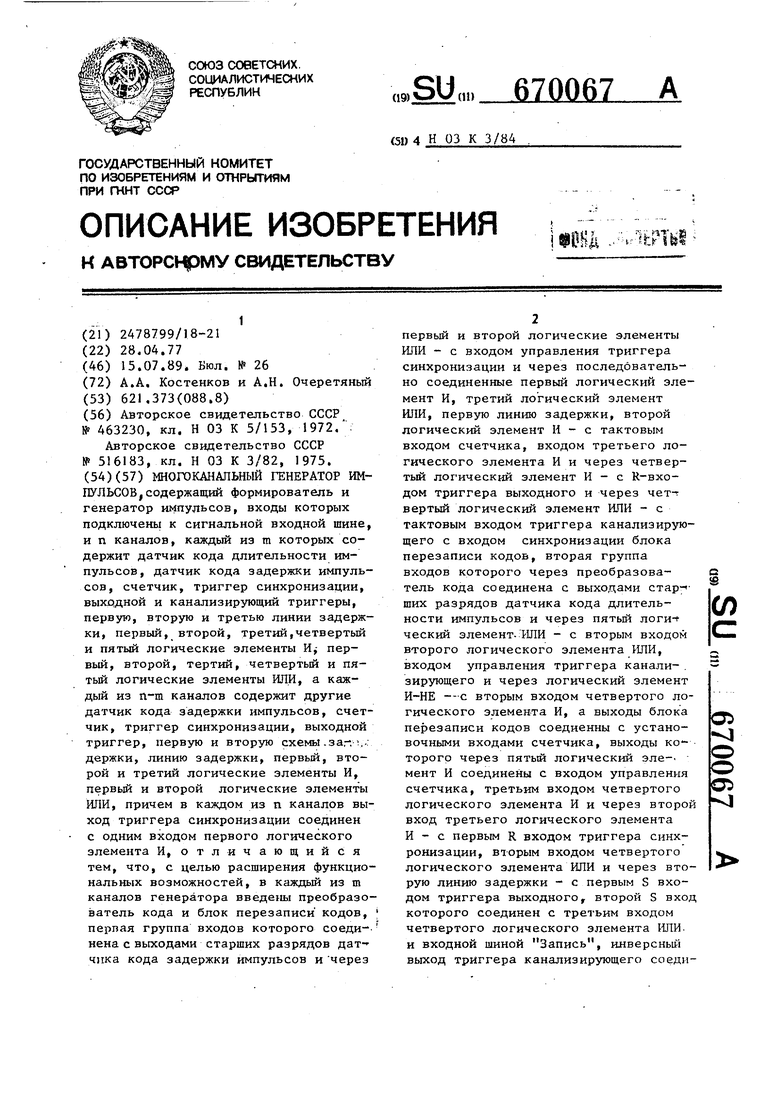

В известном генераторе задержка и длительность выходных импульсов с каналов задается с дискретностью равной периоду опорной частоты, при этом задержка в каналах отсчитывается относительно тактового импульса, выделенного из опорной частоты. 5 Это является недостатком известного устройства, так как для обесп чения дискретности в наносекундном диапазоне необходима высокая опорна частота - из-за чего возникают повы шенные требования к быстродействию элементов устройства. А если при эт требуетоя и большой диапазон выходных величин задержки и длительности импульсов (сотни наносекунд, единицы микросекунд), то возрастает разрядность счетчиков и схем сравнения. Все этоприводит к усложнению устрой ства. Например, для обеспечения величи дискрета в I не в диапазоне до 1 мкс требуется опорная частота в 1 ТТц и 10-ти разрядные счетчики и схемы сравнения. Кроме того, все каналы имеют одинаковое выполнение, что приводит к элементной избыточности в каналах, используемых только для формирования задержки импульсов при фиксированной их длительности. Это уменьшает надежность этих каналов и увеличивает их стоимость. Указанные недостатки ограничивают функциональные возможности известного генератора. Цель изобретения - расширение функциональных возможностей устройства. Цель дос тигается тем, что в много канальном генераторе импульсов, содержащем формирователь и генератор импульсов, входы которых подключены к сигнальной входной шине, и п кана лов, каждый из m которых содержит датчик кода длительности импульсов, датчик кода задержки импульсов, счетчик, триггер синхронизации, выходной и канализирующий триггеры, первую, вторую и, третью линии задерж ки, первый, второй, третий, четвертый и пятый логические элементы И, первый, второй, третий, четвертый и пятый логические элементы ИЛИ, акаждый из n-m каналов содержит дру гие датчик кода задержки импульсов, счетчик, триггер синхронизации, выходной триггер, первую и вторую схемы задержки, линию задержки, первый, второй и третий логические элементы И, первый и второй логические эле менты ИЛИ, причем в каждом из п кана лов выход триггера синхронизации соединен с одним входом первого логи 7 ческого элемента И, в каждьп из m каналов введены преобразователь кода и блок перезаписи кодов, первая группа входов которого соединена с выходами старших разрядов датчика кода задержки импульсов и через первьй и второй логические элементы ИЛИ - входом управления триггера синхронизации и через последовательно соединенные первый логический элемент И, третий логический элемент ИЛИ, первую линию задержки, второй логический элемент И - с тактовым входом счетчика, входом третьего логического элемента И и через четвертый логический элемент И с R входом выходного триггера и через четвертый логический элемент ИЛИ - с тактовым входом триггера канализирующего и входом синхронизации блока перезаписи кодов, вторая группа входов которого через преобразователь кода соединена с выходами старших разрядов датчика кода длительности импульсов и через пятьш логический элемент ШМ - с вторым входом второго логического элемента ИЛИ, входом управления триггера канализирующего и через логический элемент И-НЕ - с вторым входом четвертого логического элемента И, а выходы блока перезаписи кодов соединены с установочными входами счетчика, выходы которого через пятый логический элемент И соединены с входом управления счетчика, третьи входом четвертого логического элемента И и через второй вход третьего логического элемента И - с первым R входом триггера синхронизации, вторым входом четвертого логического элемента ИЛИ и через вторую линию задержки с первым S входом триггера выходного, второй S вход которого соединен с третьим входом четвертого логического элемента ИЛИ и входной шиной Запись, инверсный выход триггера канализирующего соединен с третьим входом третьего логического элемента И, вторым входом логического элемента И-НЕ и,входом разрешения перезаписи кода задержки импульсов блока перезаписи кодов, вход разрешения перезаписи кода длительности импульсов которого соединен с прямым выходом триггера канализирующего, R вход которого соединен с S входом счетчика, входной шиной Сброс и вторум R входом триггера синхронизации, S вход которого соединен-через третью линию задержки с вторым входом третьего .ло гического элемента ИЛИ, а выход триг гера синхронизации соединен с вторым входом Второго логического элемента И, входы управления первой и третьей линий задержки соответственно соединены с выходами младших разрядо и выходами старших разрядов в группе младших разрядов датчика кода задержки импульсов, входы управления второй линии задержки .соединены с вы ходами младших разрядов датчика кода длительности импульсов, а в каждом из n-m каналов выходы старших разрядов датчика кода задержки импульсов соединены с установочными входами счетчика и через последовательно соединенные первьш логический элемент ИЛИ, первый логический элемент И, второй логический .элемент ИЛИ . с тактовым входом счетчика и через второй логический элемент И-- с первым входом синхронизации счетчика, . первым R входом триггера синхронизации и через линию задержки - с R вхо дом триггера выходного, первый S вхо которого через первую схему задержки соединен с его выходом,а второй S вход - с входной шиной Сброс и вто рым R входом триггера синхронизации S вход которого через вторую схему задержки соединен с вторым входом второго логического элемента ИЛИ, вы ходы счетчика через третий логический элемент И соединен с вторым входом второго, .логического элемента И и входом управления счетчика, второй вход синхронизации которого соединен с входной шиной Запись, входы управления линии задержки соединены с выходами младших разрядов датчика кода задержки, при этом выход фазируемого генератора импульсов, соединен с третьим входом каждого первого логического элемента И,, а выход формирователя соединен с вторым входом третьего и второго логических элементов ИЛИ соответственно, в m и n-m каналах. Общее количество каналов п не менее двух, а количество каналов га из них - произвольное от О до п. На фиг,1 дана структурная электрическая схема многоканального генератора импульсов; на фиг. 2 - времен ные диаграммы, поясняющие работу его в одном из режимов. Устройство содержит п каналов, из которых m :каналов 1 формирования задержки и длительности импульсов и n-m каналов 2 формирования задержки импульсов с фиксированной длительностью. Каждьй из m каналов 1 содержит блок перезаписи кодов 3, первая группа входов которого соединена с выходами старших разрядов датчика 4 кода задержки импульсов и через первый и второй логические элементы ИЛИ 5 и 6 - с входом управления триггера 7 :. синхронизаод1И и через первый логический элемент И 8, третий логический элемент ИЛИ 9, первую линию 10 задержки, второй логический элемент И 11 - с тактовым входом счетчика 12,-входом третьего логического элемента И 13 и через четвертый логический элемента И 14 - с входом триггера 15 выходного и через четвертьй логический элемента ИЛИ 16 - с тактовым входом триггера 17 канализирующего и входом Синхронизации блока перезаписи кодов 3, вторая, группа входов которого через преобразователь 18 кода соединена с выходами старших разрядов датчика 19 кода длительности импульсов и через пятый логический элемент ИЛИ 20 - с вторым входом второго логического элемента ИЛИ 6, входом управления триггера 17 канализирующего и через логический элемент И-НЕ 21 - с вторым входом четвертого логического элемента И 14, а выходы блока перезаписи кодов 3 через установочные входы счетчика 12, его выходы, пятый логический элемент И 22 соединены с входом управления счетчика 12, третьим входом четвертого логического элемента И 14 и через второй вход третьего логического элемента И 13 - с первьм R входом триггера синхронизации 7, вторым входом четвертого логического элемента ИЛИ 16, и через вторую линию задержки 23 - с первым S входом триггера выходного 15, второй S вход которого соединен с третьим входом четвертого логич ского элемента ИЛИ 16 и входной шиной Запись. Инверсный выход триггера 17 канализирующего соединен с третьим входом третьего логического элемента И 13, вторым входом логического элемента И-НЕ 21, и входом разрешения перезаписи кода задержки импульсов блока

перезаписи кодов 3, вход разрешения перезаписи кода длительности импульсов которого соединен с прямым выходом триггера 17 канализирующего, R вход которого соединен с S входом счетчика 12, входной шиной Сброс и вторым R входом триггера 7 синхронизации, S вход которого соединен через третью линию задержки 24 с вторым входом третьего логического эле- ИЛИ 9 а выход триггера 7 синхронизации соединен с вторым входом второго логического элемента И 11 и первым входом первого логического элемента И 8, входы управления перво 10 и третьей 24 линии задержки соответственно соединены с выходами младших разрядов (1.,.К) и выходами старших разрядов в группе младших разрядов (1,,,К) датчика 4 кода задержки импульсов, входы управления второй линии задержки 23 соединены с выходами младших разрядов (1,..К) датчика 19 кода длительности импульсов.

В каждом из n-m каналов 2 выходы старших разрядов датчика 25 кода задержки импульсов соединены с установочными входами счетчика 26 и через первый логический элемент ИЛИ 27,. первый логический элемент И 28, второй логический элемент ИЛИ 29 - с тактовым входом счетчика 26 и через второй логический элемент И 30 - с первым входом синхронизации счетчика 26, первым R входом триггера 31 синхронизации и через линию 32 задержки - с R входом триггера выходного 33, первый S вход которого чере первую схему 34 задержки соединен с его выходом, а второй S вход - с : входной шиной Сброс и вторым R входом триггера 31 синхронизации, S вхо которого через вторую схему 35 задержки соединен с вторым входом второго логического элемента ИЛИ 29, а выход - с вторым входом первого логического элемента И 28. Выход счетчика 26 через третий логический элемент И 36 соединен с вторым входом второго логического элемента И 30 и входом управления счетчика 26, второй вход синхронизации которого соединен с входом Запись устройства. Входы управления линии 32 задержки соединены с выходами младших разрядов датчика 25 кода задержки импульсов.

Кроме того, на входе устройства предусмотрены общие для п каналов фазируемый генератор 37 импульсов, выходы которого соединены с третьим входом каждого первого логического элемента И 8 и 28 соответственно каналам m 1 и п-т 2 и формирователь 38 импульсов, выход .которого соединен с вторым входом третьего и второго логических элементов ИЛИ 9 29 соответственно m 1 и n-m 2 каналам. Число каналов тип определяется условиями применения и принима.ет целочисленные значения не менее двух для п каналов 2 и от О до п для m каналов 1.

Работа генератора импульсов многоканального основана на формировании в каналах 1 и 2 при поступлении на вход устройства запускающего импульса, выходного сигнала с задержкой относительно входного величиной, заданной соответственно каналам 1 и 2 в датчиках 4 и 25 кода задержки и длительностью, заданной в датчиках 1 кода длительности (для каналов 1) и фиксированной, определяемой схемой 34 задержки (для каналов 2).

Формирование производится путем подсчета счетчиками 12 и 26 числа импульсов, заданного в старших разрядах датчиков 4 и 25 кода задержки, с фазируемого генератора 37 импульсов, работающего в режиме непрерывной генерации с привязкой фазы выходного сигнала к входному импульсу запуска, задержанных соответственно на линиях 10 и 32 задержки, управляемых с младших разрядов указанных датчиков, с выдачей сигнала по концу счета и формирования фронта выходного импульса по этому сигналу. Последующее формирование среза вькодного импульса Приходится через время, определяемое:

-числом импульсов .той же последовательности что и при формировании задержки, отсчитанным от момента выдачи сигнала для формирования фронта заданным.в старших разрядах датчиков 19 кода длительности, подсчитанным

счетчиком 12 с вьщачей сигнала по ,концу счета и задержкой этого сигна:ла в линии 23 задержки, управляемой с младших разрядов датчика 19 кода длительности (для m .каналов 1);

-схемой задержки 34 (для n-m каналов 2). Значения задержки каждого из управляемых звеньев-линий 10,23,32 задержки, а также период следования импульсов фазируемого генератора 37 импульсов выбираются в соответствии с весовыми коэффициентами кода задаваемого .с датчиков 4, 19 и 25 кода, при этом величина периода равна весо вому коэффициенту разряда, следующему за старшим из разрядов, управляю щим линиям 10,23 и 32 задержки. На--.. пример, при.двоичном коде с датчиков 4,19 и 25 кода, минимальном дискрете выходных сигналов равном 1 не, ли ниях 10, 23 и 32 задержки с пятью уп равляемыми звеньями - задержки в каж дом звене выбираются в соответствии с номером звена (разрядом управляющего кода) - 1 не, 2 не, 4 не, 8 не, 16 НС, а период следования импульсов с фазируемого генератора 37 импульсов - равным 32 НС, тогда вес следую щих разрядов составит 64 не, 128 не и т.д. В зависимости от величины кода в датчиках 4 и 19 кода m каналов 1 возможны следующие режимы работы в этих каналах: В зависимости от величины кода в датчике 25 кода n-m каналов 2 возмож ны следующие режимы работы в каналах: 1 ,, где Тр период следования импульсов с фазируемого генератора 37 импульсов; величины задержки и длительности импульсов, обеспечиваемые на выходе каналов. Режимы работы каналов 1 и:2 независимы, т.е. в любом канале может быть задан любой из возможных для данного канала режим работы. Устройство приводится в состояни готовности к работе путем подачи предшествующих первому входному запускающему импульсу сигналов Сброс и Запись. По сигналам Сброс про изводится установка в начальное сос тояние триггеров 15 и 33 выходных триггеров 7 и 31 синхронизации счет чиков 12 и 26, триггера канализирую 6 щего 17. По сигналу Запись - запись кода задержки импульсов с датчиков 4 и 25 кода соответственно в счетчики 12 и 26 и переброс триггера 17 канализирующего в состояние разрешения записи кода длительности импульсов с датчика 19 кода длительности через блок перезаписи кодов 3 и счет- ; чик 2t По приходу входного запускающего импульса в фазируемом генераторе 37 импульсов производится привязка фазы его выходного импульса к фазе запуекающего импульса, причем первый импульс появится со сдвигом равным периоду колебаний генератора 37. С выхода формирователя 38 появится одиночный импульс, по фазе совпадающий с запускающим импульсом и длительностью равной длительности импульсов генератора 37. Временной сдвиг между импульсом генератора 37 и импульсом с формирователя 38 равен периоду колебаний генератора 37. Рассмотрим работу m каналов 1 в режимах 1,2,3,4. Режим 1. Импульс е формирователя 38 через линию 24 задержки взводит триггер 7 еинхронизации, поэтому на первый и второй логичеекие элементы И 8 и 11 поетупит еигнал разрешения Логическая 1. Кроме того, импульс с формирователя 38 поступает на третий логический элемент ШШ 9, на котором производится логическое сложение указанного импульса и выходных импульсов генератора 37. В результате на вход линии 10 задержки поступает последовательность импульсов, по фазе совпадающая с входным запуекающкм импульеом, е периодом равным Тр, которая задерживается на этой линии на величину пропорциональную управляющему коду,задаваемому на нее с выходов 1.,.К датчика 4 кода задержки. С выхода линии 10 задержки, через второй логический элемент И П, сигнал поступает на тактовый вход счетчика 12 и третий и четвертый логические элементы И 13 и 14, прохождение сигнала через которые запрещено уровнем Логический О, поступающего с пятого логического элемента И 22, так как код задержки, записанньй в.счетчик 12 со старших разрядов датчика 4 кода задержки, отличен от нуля из-за того,что . В счетчике 12 записывается обратный код. На третий и второй логические эле менты И 13, 14 приходят соответствен но уровни Логической О и Логическая 1 с инверсного выхода тригге- ра 17 канализирующего и логического элемента И-ПЕ 21. Счетчик 12 считыва ет выходные импульсы со второго логи ческого элемента И I1 и по номеру им ртульса на единицу меньшему, чем число заданного с датчика 4 кода задерж ки на его выходах устанавливается код 11 ... I,i Благодаря этому с выхода пятого логического элемента И 22 поступает уровень Логическая I, кото рый подается на вход управления 12 счетчика, запрещая дальнейший счет. Этот же уровень разрешает прохождекие сигнала через третий и четвертый логические элементы И 13, 14. Следую 1ЦИЙ импульс с выхода второго логичес кого элемента И 11, через четвертый логический элемент И 14, поступив на R вход триггера, выходного 15, взведет его в состояние Логическая 1 на инверсном выходе. Одновременно этот импульс через четвертьш логический элемент ИЛИ 16 по фронту произведет перезапись кода длительности импульсов с датчика 19 кода длительности в счетчик 12 через блок перезаписи кода 3 и преобразователь 18 кода, а по срезу - перебросит триггер 17 канализирующий. В резуль тьте разрешится перезапись кода задержки импульсов с датчика 4 кода задержки и поступит уровень Логнческая 1 на вход третьего логического элемента И 13 с выхода триггера канализирующего 17 и уровень Логический О на вход четвертого логичес кого элемента И-НЕ 21, что приводит к появлению уровня Логический О на входе четвертого логического элемента И 14. Записанный в счетчик 12 код длительности импульсов, также как и ранее код задержки, отличен от нуля, в результате уровень Логический о с выхода пятого логическог элемента И 22 разрешает счет в счетчике 12 и запрещает прохождение импульсов через третий и четвертый логические элементы И 13, 14, Так же как и в предыдущем случае, по появлении на выходах счетчика I2 кода 11 ... I, на выходе пятого логического элемента И 22 появится уровень Логическая 1 запрещающий счетв счетчике I2 и разрешающий прохождение порледующего импульса через третий логический элемент И 13. Следующий импульс, проходя через третий логический элемент И 13 и линию 23 задержки, сбрасывает триггер 15 выходной и тем самым обеспечивается срез выходного импульса. Величина задержки задается с младших 1...К разрядов датчика 19 кода задержки. Кроме того, этот импульс с выхода третьего логического элемента И 13 сбросит триггер 7 синхронизации, в результате чего поступит уровень Логический О на первый и второй логические элементы И 8, II и запретится прохождение импульсов с генератора 37 на счетчик 12 и через четвертый логический элемент ИЛИ 16 произведется по фронту импульса перезапись кода задержки в счетчик 12с датчика 4 кода задержки импульсов через блок 8 перезаписи кода, а по срезу - переброс триггера 17 канализирующего, разрешая перезапись кода длительности импульсов с датчика 19 кода длительности. На этом цикл формирования задержки и длительности выходного импульса с канала заканчивается и канал переходит в режим ожидания следующего запускающего импульса с формирователя 38. С приходом следующего запускающего импульса цикл повторяется. Как видно из принципа работы, сформированные величины задержки и длительности входного импульса с канала будут пропорциональны величине кода с датчиков 4 и 19 кода. Складываются они иэ величины заданной в линии 10 задержки и отсчитанного счетчиков 12 числа импульсов равного коду со старших разрядов датчика 4 кода задержки умноженного на Т,, (при формировании задержки) и отсчитанного счетчиком 12 числа импульсов равного коду со старших разрядов датчика 19 кода длительности умноженного на Тр и величины задержки заданной в линии 23 задержки. Длительность цикла равна сумме времени задержки и длительности выходного с канала импульса. Преобразователь кода 18 понижает код длительности импульсов (в старших разрядах) на 1 для компенсации |ПОтерч одного импульса при переходе с такта формирования задержки на такт формирования длительности выход ного импульса. Запрет на первый и второй логические элементы И 8, И с триг,гера 7 синхронизации поступает с некоторым запаздыванием относительно выходного импульса второго логического элемента И 11, Это запаздывание определяется задержкой на третьем логическом элементе И 13 и задержкой пере- ключения триггера 7 синхронизации. Если длительность импульса на входе второго логического элемента И 1 1 больше этой задержки, то на его выходе формируется 1да5пульс по длительности равный этой задержки. Если величина задержки, задаваемая в линии 10 задержки приближается к Т, то из-за задержки в упомяну той цепи на вход линии 10 задержки попадает часть импульса следующего за импульсом, соответствующим концу цикла формирования задержки и длительности импульсов. Этот импульс является помехой и он отсекается на втором логическим элементе И 11, так как в этом случае задержка в линии 10 больше, чем в упомянутой цепи и поэтому запрет с триггера 7 синхронизации на логический элемент И 11 придет раньше, чем этот импульс помехи достигнет выхода линии IО задержки. Если же длительность цикла формирования задержки и длительности выходного импульса канала приближается к периоду внешних запускающих устройство импульсов, то возможна следующая систуация; импульс помехи еще находится в линии 10 задержки, на ее вход уже поступает через трети логический элемент ИЛИ 9 импульс запуска следующего цикла с формирователя 38 и, таким образом, в линии 1 задержки находятся два импульса помеха и запускающий. Эта ситуация приведена на фиг.2. Заштрихованный импульс на выходе элементов 9, 10 и является помехой. Как видно из ди граммь помеха переходит в следующий цикл формирования задержки и длител ности. Для исключения этой помехи введена линия 24 задержки, которая управляется со старших разрядов 1.. в группе младших разрядов 1...К дат чика 4 кода задержки. Через нее про изводится включение триггера 7 синх ронизации. Величина задержки в ней задается относительно грубо и отслеживает задержки в.старших разрядах линии 10 задержки. При указанной выше ситуации, разрешение на второй логический элемент И 11 придет с не.которым небольшим опережением первого счетного импульса следующего цикла, что исключает помеху от предыдущего импульса следующего цикла. Номер разряда 1,начиная с которого подается управляющий код на линию 24 задержки, определяется задержкой в цепи: третий логический элемент И 13, триггер 7 синхронизации. Все сказанное выше иллюстрируется временными диаграммами, приведенными на фиг.2, где показаны сигналы с выходов элементов устройства, работающего в режиме 1, причем-индексы на фиг.2 соответствуют выходным напряжениям соответствующих элементов фиг.1. Режим 2. В этом режиме в старших разрядах датчика 4 кода задержки записан код, равный нулю, поэтому этот код будучи записанным в счетчик 12, на выходе счетчика 12 установит код П ... 1 . Благодаря этому с выхода пятого логического элемента И 22, уровень Логическая 1 будет подан на управляющий вход счетчика 12 и входы третьего и четвертого логических элементов И 13, 14, что.приведет к запрету счета в счетчике 12 и разрешение прохождения сигнала через четвертый, .логический элемент И 14. I - . Входной сигнал, проходя через линию 10 задержки, второй и четвертый логические элементы И 11, 14 взводит триггер 15 выходной, а далее последовательность работы до конца первого цикла такая же, как и в режиме 1 при формировании длительности выходного импульса. Величина сформированной задержки будет определяться кодом с датчика 4 кода задержки в младших разрядах 1...К, управляющих линией 10 задержки, а длительность выходного импульса - числом импульсов, о-тсчитанных счетчиком 12, пропорциональным коду со старших разрядов датчика. 19 кода длительности, умноженным на Т. плюс задержкой в линии 23 задержки, управляемой с младших разрядов 1...К датчика 19 кода длительности.

Режим 3. В этом режиме в старших разрядах датчика I9 кода длительности записан код равный нулю. В результате этого уровень Логический О с выхода пятого логического элемента ИЛИ 20 поступает на управляющий вход триггера канализирующего 17, фиксируя его в положении разрешения перезаписи кода задержки с датчика 4 кода задержки (уровень Логическая 1 на инверсном выходе триггера) и на логический элемент И-НЕ 21, с выхода которого уровень Логическая 1 поступает на четвертый логический элемент И 14,

В такте формирования задержки канал работает так же, как и в режиме 1, Далее этот же импульс, который формирует фронт выходного .импульса на триггере выходном 15, через третий логический элемент И 13, линию 23 задержки сбрасывает триггер 15 выходной, формируя срез выходного импульса.

Величина сформированной задержки будет определяться задержкой в линии 10 задержки, управляемой с младших разрядов 1...К датчика 4 кода задержки плюс числом импульсов, отсчитанных счетчиком 12, пропорциональным коду со старших разрядов датчика 4 кода задержки, умноженным на Т, а длительность выходного импульса - задержкой в линии 23 задержки, управляемой с младших 1,..К разрядов датчика 19 кода длительности.

Режим 4. В зтом режиме -в старших разрядах датчиков 4, 19 кода - код равен нулю, поэтому на выходе первого, пятого и второго логических элементов И 5, 20 и 6 будет уровень Логический О. Благодаря этому триггер 7 синхронизации фиксируется в положении уровень Логическая 1 на его выходе и через первый логический элемент И 8 запретится прохождение импульсов с генератора 37. Остальные уровни установятся такими же, как в режиме 3.

Импульс с выхода формирователя 38, через третий логический элемент ИЛИ 9, линию 10задержки, второй и четвертый логические элементы И 11, 14 взведет триггер 15 выходной и через третий логический элемент И 13, линию 23 задержки.сбросит его. В результате на выходе канала сформируется импульс с задержкой и длительностью, определяемой величиной задержки, заданяс в линиях 10 и 23 задержки, управляемых с младших разрядов 1.,.К датчиков 4, 19 кодов.

В счетчике 12 в каждом такте цикла формирования задержки и длитегсьности выходного импульса подтверждается код равный 1 1 ... 1 путем перезаписи его со старших разрядов датчика 4 кода задержки через блок перезаписи кодов 3.

Рассмотрим работу n-m каналов 2 в режимах 1 и 2.

Режим 1. В этом режиме импульс с формирователя 38 через схему 35 задержки взведет триггер 31 синхронизации, с выхода которого уровень Логическая 1 поступит на первый логический элемент И 28 и разрешит прохождение импульсов с генератора 37 на второй логический элемент И 29, где

произойдет логическое сложение сигналов с генератора 37 и формирователя 38, которые поступают через этот элемент на тактовый вход счетчика 26 Так как код в старших разрядах датчика 25 кода задержки отличен от нуля, то код, записанный в счетчик 26 в инверсном виде, дает на его выходе код отличньш. от 1 1 ... 1, поэтому на выходе третьего логического элемента ИЛИ 36 - уровень -Логический О, который разрешает счет в счетчике 26 и запрещает прохождение импульсов через второй логический элемент И 30. По мере счета импульсов счетчиком 26, по достижении на его выходе кода 1 1 ,. 41 с выхода третьего логического элемента И 36 уровень Логическая 1 запретит счет в счетчике и разрешит прохождение импульсов через второй логический элемент И 30. Первьй же следующий импульс, через второй логический элемент И 30 сбросит триггер 31 синхронизации, через линию 32 задержки взведет триггер 33 выходной, который сбросится в исходное состояние через время, определяемое схемой 34 задержки. Этот же импульс произведет перезапись кода со старших разрядов датчика 25 кода задержки в счетчик 26.

В результате на выходе канала сформируется импульс с задержкой по отношению к входному пропорциональному коду с датчика 25 и величиной равной числу импульсов, отсчитанных счетчиком 26, умноженному на плюс

велиЧ{ша задержки в линии 32 задержки, управляемой с младших 1.,,К разрядов датчика 25 кода задержки, а длительностью равной длительности задержки в схеме ЗА задержки,

После сброса триггера 31 синхронизации цикла формирования выхоДного сигнала в канале заканчивается.

Режим 2, В этом режиме код в старших разрядах датчика 25 кода задержки равен нулю, В результате уровень Логический О с выхода первого логического элемента ИЛИ 27 поступает на первый логический элемент И 28 и запрещает прохождение через него импульсов с генератора 3,7. На выходах счетчика устанавливается код I 1 ... 1 и уровень Логическая 1 с выхода третьего логического элемента И 36 запрещает счет в счетчике 26 и разрешает прохождение импульсов через второй логический элемент И 30. Импульс с выхода формирователя 38, через BTO.рой логический элемент И 30, линию 32 задержки, взводит триггер 33 выходЙхв

ной, который затем сбрасывает в исходное состояние через схему 34 задержки.

В результате сформируется выходной импульс с задержкой,равной величине задержки в линии 32. задержки и длительностью равной задержке в схеме 34 задержки.

Схема 35 задержки вносит запаздывание в запуск триггера 31 синхронизации на время переходных процессов в генераторе 37. Величина задержки 41.

.Как видно из описания работы устройства минимальная величина дискретности в каналах т и п-т обеспечивается на линиях 10, 23 и 32 задержки, определяется только параметрами этих линий и может быть обеспечена от долей до десятков наносекунд. Частота фазируемого генератора 37 определяется, как бьшо сказано ранее, старшим разрядом этих линий и весовыми коэффициентами управлякицего : кода.

.1,

| Многоканальный датчик одиночных импульсов | 1972 |

|

SU463230A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-07-15—Публикация

1977-04-28—Подача