(Л

С«9

сл

в автоматизированных комшшксах функ- цгюкальпого н параметрического йон- троля интегральных схем. Цель нзо- брете1шя - повышение быстродействия н точности формирования временных - интервалов. Повьшение точности фор- мафования временных интервалов до- стигается за счет введения оперативного запоминающего устройства 21 калибровочных кодов, информация в которое записывается на этапе калибровки управляемой линии 1 задержки. Таким образом устраняется ошибка задания времени задержки управляемой линией 1 задержки в зависимости от управляющего кода, который подается на адресный вход оперативного эапо-. минающего устройства 21 калябровоч- ых кодов с выхода регистра. 11 через блок 20 элементов ИЛИ. В режиме калибровки упр авление оперативным запоминающим устройством 21 калибровочных кодов осуществляется с выхода регистра 15. Режим работы y tpofiCTBa задается с помощью блока 22 выбора режима. Повышение быстродействия устройства в режиме управления в реальном масштабе времени достигается за счет введения регистров 16, 17. Синхронизация записи информации в регистр 16 осуществляется с выхода 26 синхронизации, а в регистр 17 - с выхода D-триггера 6. Устройство содержит также генератор 2 опорной кварцевой частоты, ключ 3, програм- мируемьй делитель 4 частоты, счетчик 5 импульсов, блок 7 управления, оперативное запоминающее устройство 8, сумматор 9, регистр 10, элементы ИЛИ 12, 13, линию 18 яадержки, D-триггер 19j каналы 23 формирования. 1 з.п. ф-лы, 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для формирования импульсных последовательностей | 1982 |

|

SU1077539A1 |

| Генератор псевдослучайных сигналов | 1986 |

|

SU1347166A1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2502128C2 |

| Мультимикропрограммная управляющая система | 1984 |

|

SU1241244A1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2500025C2 |

| Цифровой обнаружитель-измеритель частоты | 1989 |

|

SU1797127A1 |

| Устройство для временного программного управления | 1985 |

|

SU1290259A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Синтезатор интервалов времени | 1986 |

|

SU1406558A1 |

| УСТРОЙСТВО ЗАДЕРЖКИ ИМПУЛЬСОВ | 2008 |

|

RU2386208C1 |

Изобретение может быть нсполь- эовано для управления временными интервалами тестовых и синхронизирующих последовательностей сигналов

1

Изобретение относится к измерительной и вычислительной технике и может быть использовано для управления временными интервала-ми тестовых и синхро низирую11Ц1х последова тельпо- стей сигналов в автоматнзироваги к комплексах функционального н пара-метрического контроля БИС ОЗУ и БИС микропроцессоров, а также в качестве системы си1п ропизацни быстродейст вуюш,их ЭВМ.

Целью изобретения .является повы- шеине быстродейстпия н то -пюсти фор- 0lpoвaния оременных интервалов.

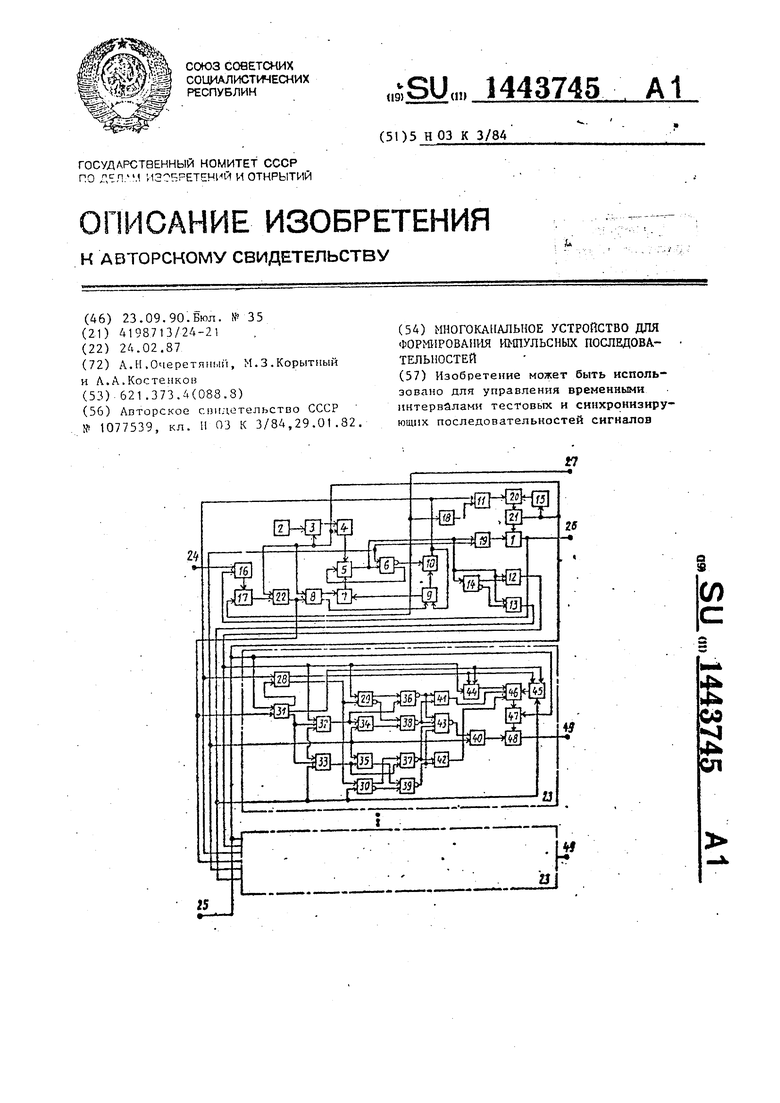

чертеже приведена функциональная схема предлагаемого устройства.

Многоканальное устройство для фомирования импульсных последователь- костей содержит управляемую линию задержки (УЛЗ) 1, генератор 2 опорной кварцевой частоты,, ключ .3, про- .граммируемый делитель 4 частоты, счетчик 5 импульсов, П триггер б, блок 7 управления, оперативное запоминающее устройство (ОЗУ) 8, сумматор 9, регистры 10, 11, элементы ИЛИ 12, 13, счетн лй триггер 14, регистры 5, 16, 1,7, яинию заде15жки (ЛЗ) 18, D-триггср 19, блок элементов 11ПИ 20, оперативное запоминающее устройство (ОЗУ) 21 калибровочных кодов, блок 22 выбора режима, каналы 23 формирования, адресную, шину 24, информационную шину 25,/выходы 26, 27 синхронизация.

Выход генеоатооа 2 опооной квар- ценой частоты через ключ 3 соединен

с входом программируемого делителя 4 частоты, выход которого соединен с входами синхронизации счетчика 5 импульсов, О-триггероо б и 19 и пер-, вым входом каждого канапа 23 формирооания. Вькоп счетчика 5 импульсов соединен с информационными входами D-триггеров 6 и 19, первыми входами элементов ИЛИ 12, 13 и входом счетного триггера 14, прямой н инверсный выходы которого соединены соот- ветствеяно с вторым входом элемен - та I Jll 12 и вторым входом элемента ИЛИ 13. Выходы элементов ИЛИ 12 и 13 соединены соответственно с четвертым и пятым входами каждого канала 23 формирования. Прямой выход D-триггера 6 соединен с входом управления счетчика 5 импульсов. Инверсный выход В-триггерл 6 соединен

с входами записи регистров 10, 17 и

через ЛЗ 18 ..с входом записи регистра 11, а также с выходом 27 синхронизации устройства. Выход регистра 10 соединен с первым входом сумматора 9, второй вход которого соединен с выходами младших разрядов ОЗУ 8. Выход регистра tO соединен также с информационным входом регистра 11 и третьим входом каждого канала 23 формирования. Выход преполнения сумматора 9 соединен с входом управления блока 7 управле

дом старших разрядов ОЗУ 8, а выход - с информационными входами счечика 5 импульсов. Информационные входы ОЗУ В, ключа 3, программируемого делителя 4 частоты, ОЗУ 21, регистра 15, блока 22 выбора режима и второй вход каждого канала 23 формирования, соединены с информационной шиной 25 устройства. Адресная шина 24 устройства через регистры 16, 17 и блок 22 выбора режима соединена с адресным входом ОЗУ 8 и шестым входом каждого канала 23 формирования. Выходы регистров 11 и 15 через блок элементов ИЛИ 20 соединены с адресными входами ОЗУ 21 калибровочных кодов, выходы которого соединены с входами управления УЛЗ 1, вход которой соединен с выходом D-триггера 19, а выход - с выходом 26 синхронизации и с входом записи регистра 16.

Каждый канал 23 (формирования содержит сумматор 28, D-триггеры 29, 30, ОЗУ 31, счетчики 32, 33 импульсов, D-триггеры 34, 35, элементы 36-39, блок АО тактируемой задержки, элементы ИЛИ 41,А2, элемент ИЛИ-НЕ 43, регистры 44, 45, мультиплексор 46, ОЗУ 47 калибровочных кодов, УЛЗ 48, а также вы.ход 49.

Выход старших разрядов ОЗУ 31 соединен с информационными входами счетчиков 32, импульсов, а выход, первой группы младших разрядов с первым входом сумматора 28, вто рой вход которого является третьим входом канала 23; Выход сумматора 28 соединен с входами регистров А4 и 45, а. его выход переноса соединен с информационными входами D-триггеров 29 и 30, Выход счетчика 32 импульсов соединен с информационным входом D-триггера 34 и пер0

вым входом элемента. ИЛИ-НЕ 36. Прямой и инверсный выходы D-триггера

29соединены соответстреннр с втог рым входом элемента ИЛИ-НЕ 36 и пер-« вым входом элемента ИЛЯ-НЕ 38, с v вторым входом которого соединен выход D-триггера 34. Выход счетчика

33 импульсов соединён с информационным входом D-триггера 35 и первым входом элемента ИЛИ-НЕ 37.. Пря- мой и инверсный выходы D-триггера

30соединены соответственно с вторым входом элемента ШШ-НЕ 37 н первым входом элемента ИЛИ-НЕ 39, второй вход которого соединен с выходом D-триггера 35. Выходы элементов ИЛИ-НЕ 36 и 38 соединены с входами элемента ИЛИ 41

0 и входами элемента ИПИ-НЕ A3. Выходы элементов ИЛИ-НЕ 37 и 39 соединены с входами элемента ИЛИ 42 и входами элемента ИЛИ-НЕ 43. Выход элемента ИЛИ-НЕ 43 соединен с инфор5 мационным входом блока 40 тактируемой задержки, вход синхронизации которого соединен с входами синхронизации П-триггеров 34, 35, счетчиков 32, 33.импульсов и с первым вхо0 дом канала 23 формирования. Выходы элементов ИЛИ 41 и 42 соединены с входами управления мультиплексора 46, инфориащюнные входы которого соединены с выходами регистров 44 и 45. Вьпход мультиплексора 46 соединен с адресными входами ОЗУ 47 калибровочных кодов, информационный вход которого соединен с информационным входом ОЗУ 31 и с вторым входом канала

0 23 формирования. ..

Выходы ОЗУ 47 калибровочных кодов соединены с входами управления . УЛЗ 48, выход которой япляется выходом канала 23. Вход записи регистра

с 44 соединен с входом синхронизации D-триггера 29, входом управления счетчика 32 импульсов и четвертым входом канала 23 формирования. Вход записи регистра 45 соединен с входом синхронизации D-триггера 30, входом управления счетчика 33 импульсов и пятым входом канала 23 формирования4 Первые информационные входы регистров 44 и 45 объединены между собой и соединены с информационным выходом сумматора 28. Вторые информацион йые входы регистров 44 и 45 объеди- . иены между собой и соединены с третьим выходом ОЗУ 31 (этот выход яв5

0

ляр гся вьосодом младшгхразрядов ОЗУ

31). Адресные втсод ОЗУ31 соеднаен

с шестым входом канала23 формирования .

Устройство работает следуюпхим образом.

Значение .периода Т, генератора 2 выбирается в соответствют с требуемой дискретностью S программного управления периодом следования сигналов на выходе 26 синхронизации и выходов 49 каналов 23 дискретностью Sj программного управления взаим НОИ задержкой сигналов на выходах ка налов 23 формирования, а также разрядностью кодов, снимаемых.с .младших разрядов ОЗУ 8,и 31, с использованием которых осуществляется управление

-УЛЗ 1 и 48, .

В общем виде значение Tj, определяется следующей зависимостью

TO

где S - дискретность управления соответствующего, временного параметра импульсной последова- .тельности;

m - разрядность кода, с использованием которого осуществляется управленпа соответствую- щей УЛЗ (разрядность регистров 11, А4, ,45).

Например, если S 1,25 не и разрядность кода, поступающего с, ОЗУ 8 на сумматор 9, равна 3, то Т 1,25х х2 10 НС.

При выбранном значении Т и заданной разрядности соответствующего кода управления в соответствии с Т S 2 требуемая дискретность программного управления определяется зависимостью

. S

Т«/2

tr

Если в рассмотренном вьше примере с выходов ОЗУ 31 на входы сумматора 28 и регистров 44, 45 считывается пятиразрядный код, то

п

10

F

0,3125 НС.

. Весовые коэффициенты разрядов кодов, поступающих на входы сумматора 28 каналов 23 формирования с соответствующих выходов ОЗУ 31 и с выхода регистра 10, должны совпадать. При

m

выполнении соотношения Т, - S-2 весовые коэффициенты разрядов кодов/ считываемых с соответствующего ОЗУ, определяются зависимостью

S 2

1-1

где Ср - весовой коэффициент i-ro разряда кода (рассматривается управление с использованием двоичного кода) .

Сам код, заносимый в. соответствующее ОЗУ, определяется зависимостью

N

J

Ч

J

0

t h

5

0

5

0

5

55

где N - заносимый в соответствии с J-M значением параметра управляющий код; j-e программно задаваемое значение параметра.

В начальный момент времени счетчик импульсов 5, регистры 10, 11, 16, 17-, счетный триггер 14 и D-триг- геры 19, 29, 30, 34, 35 приводятся в в нулевое состояние. D-триггер 6 и счетчики 32, 33 импульсов приводятся Б единичное состояние.

На зтапе подготовки устройства к работе в ОЗУ 8 и 31 заносятся коды требуемых значений соотнетственно периода следования сигналов на выходах 26, 27 синхронизации устройства и взаимной задержки сигналов на выходах 49 каналов формирования 23.

При подаче юманды по информационной шине 25 ключ 3 разоешает прохождение сигналов опорной частоты ,с выхода генератора 2 опорной кварцевой частоты на вход программируемого де лителя 4 частоты. С вькода делителя 4 частоты сигналы без деления или деленные в определенном соотношении (в зависимости от управления по информационной шине 25) поступают непрерывной последовательностью на входы синхронизации счетчика 5 импульсов, D-триггеров 6 и 19, а также на входы синхронизации счетчиков 32, 33 импульсов, D-триггеров 34, 35 и блока 40 тактируемой задержки каждого из каналов 23 формирования.

Уровень сигнала Логический О, поступая с прямого выхода D-тригге ра 6 на вход управления счетчика 5 импульсов, разрешает режим занесения информации в этот счетчик, а еди ничный уровень разрешает режим сче-

O :„

10

15

20

1Л43745 счетчиком 5 импульсов очередного временного интервала.

Значение задержки на ЛЗ 18 выбирается таким образом, что суммарная задержка раслространения сигналов через ЛЗ 18, регистр 11, блок элементов ИЛИ 20 и времени выборки ОЗУ 21 была бы не менее суммы собственной задержки УЛЗ 1 и максимальной иэ программно задаваемых на этой же УЛЗ.

Код с выхода регистра 11 через блок элементов ИЛИ 20 (при наличии нулевого кода на выходе регистра 15) поступает на адресные входы ОЗУ 21, на выходе которого считывается управляющш код УЛЗ 1. Воз- можность занесения в ОЗУ 21 на этапе калибровки требуемых кодов позволяет учесть возможную нелинейность закона управления УЛЗ 1 в зависимости от управляющего кода. Организация адресного управления ОЗУ 8 и 31 через промежуточные регистры 1 б fi 17 при синхронизации записи а пер- вьА из них с выхода 26 синхронизации устройства, а во второй - с выхода D-триггера 6.позволяет существенно повысить быстродействие устройства в режиме управления в реальном масштабе времени.

Условиями, определяющими, минимальный период следования сигналов, будут следующие:

а) к моменту занесения информации в двоичный счетчик 5 в начале очередного цикла формирования периода след;ования сигналов необходимо, чтобы на его информационных входах установился управляющий код, оп- ределяемлй изменением.состояния ОЗУ 8 (в зависимости -от изменения его адресного управления)р сумматора 9 и блока 7 управления, т.е.

чт ре тр

п л

н

25

30

35

40

45

WKUi

.{k)s t + t« -f t

де t

«т о

И

-в te.o

-время срабатывания регистра 17;

-задержка распространения сигналов в блоке 22; время выборки информации при изменений адреса из ОЗУ 8:

задержка распространения сигналов в блоке 7-управления;

0

10

3745

- минимальное время подготовки информационных вхо дов счетчика,5 по отноше нию к входу синхронизации Используя ту же элементную базу, что и в прототипе, а также применяя регистры 16 и 17, реализованные на триггерах микросхем 1500 серии ( . 1,5 не), имеем

1,5 + 1,5 3,5 + 3,5

+ 10 +

20 не;

15

б) для осуществления надежной записи очередного кода адресного управления в. регистр 16 необходимо выполнение

Тм„„ г

+ tL + t

16

c-D

5

где ta - t t

c-D

0

собственная задержка УЛЗ 1; максимальное задаваемое программно на УЛЗ 1 значение задержки; минимальное время подготовки регистра 16 по информационным входам относительно входа синхронизации.

Поэтому (k)

мик i

8,5 -4- 10,0 + ,19,5 НС.

1,0

40

Минимальный период работы устройства в реальном масштабе времени определяется из условия

Т (k) &

мни

макс

мин 1

(k).

j ллим 1

45

Очевидно, что в рассматриваемом примере Т д-ц., 20 не, т.е. быстро

действие устройства практически в два раза более высокое чем у прототипа.

Сигналы отрицательной полярности длительностью Т , образующиеся на

..выходе счетчика 5 импульсов, поступают на счетный триггер 14 и элементы ИЛИ 12 и 13. Переключаясь, счет- . ный триггер 1А определяет очередность поступления сигналов с выхода счетчика 5 импульсов через элементы ИЛИ 12, 13 на входы управления с оответга на пычнтапие. Занесение информации п счетчик 5 и счетчики 32 и 33 .каналов 23, осуществляется сигналом, поступагоишм на нход синхронизации этих счетчиков, при наличии уровня логического О на их входе управления. С приходом первого сигнала с выхода делителя 4 частоты на вход синхронизации D-триггера 6 осу- щёствлягтсп его переход из начального состояния логической 1 на прямом выходе в состояние логического О, так как в этот момент времени на его D-вход поступает уровень логического О с выхода счетчика 5 импульсов. С приходом второго сигнала опорной частоты осу- luec i пляется занесение с счетчик 5 импульсов кода с выхода блока 7. D-триггер 6 при этом переходит в состояние логической 1 на прямом выходе. Таким образом, на прямом выходе D-триггера 6 образуется сигнал отрицательноГ: полярности, а на инверсном выходе - сигнал положительной полярности длитeJTьнocтью TO , который поступает на вход занесе1П1я регистра 10 и заносит в этот регистр код, поступающий с выхода сумматора 9, а тдкже через ЛЗ 18 поступает на вход занесения регистра 1 1 .

На выходе D-триггера 19, информационный вход которого соедине) с ходом счетчика 5 импульсов, вырабатывается такой же сигнал, как и на прямом выходе D-триггерз 6. С выхода D-триггера 19 сигнал поступ-ает на вход УЛЗ 1, на которой задерживается на время, определяемое кодом, поступающим на ее входы управления с выходов ОЗУ 21.

С приходом второго сигнала на вхо синхронизации счетчика 5 происходит занесение, информации с выхода блока 7 управления в этот счетчик. Блок 7 в зависимости от управляющего воздействия, поступакзшего с выхода переноса сумматора 9, реализует две функции: при наличии на входе управления уровня логической (при наличии переноса на выходе сумматора 9) реализуется функция f А - 1, при наличии уровня логического О - функция f Л - 2, где А - код, поступающий с выходов старших разря- дов ОЗУ 8. jia первый вход блока 7.

В начальный момент времени перенос на выходе сумматора 9 отсутствует, так как на его вторые входы подается НУЛЕВОЙ код с выхода регистра 10. Поэтому блоком 7 реализуется функция . Код.счнтьгааемый с ОЗУ 8, определяется состоянием регистров 16 и 17 и выбранным режимом работы блока 22,

В зависимости от управления по- ступающего по информационной шине 25, блок 22 пропускает на адресные входы ОЗУ 8 либо коды с выхода регистра 17, либо коды той Tfe р1азрядно- сти, но заносимые по информационной шине 25 в блок 22. Режиму работы

устройства при управлении в реальном масштабе времени соответствует пер- вьй из этих режимов работы блока 22, а второй режим используется при эа- грузке ОЗУ 8 и 31 по информационной шине 25,

Начиная с третьего сигнала опорной частоты на входе синхронизации счетчик 5 импульсов начинает счет иа вычитание, продолжающийся до момента, пока счетчик не обнулится, при этом на выходе счетчика устанавливается уровень логического О, ко- TopbDi через такт устанавливается на вь1ходе 0-т,риггера 6. К этому моменту времени на выходах ОЗУ 8 и ОЗУ 31 кяналов формирования 23 устанавливаются за счет управления по адресным входам коды, определяющие соответственно значение второго периода следования сигналов и значения взаимной задержки сигналов на вьсходах 9 15аналов 23 формирования.

При наличии уровня О па входе управления счетчика 5 импульсов осуществляется его загрузка кодом, с выхода блока 7. D-триггер 19 в этом же такте переходит в уровень логи- ческой 1 на прямо м вькоде, а сигнал с его выхода поступает на вход ТЛЗ .1 и задерживается на время, кратное дискретности программного управления периодом следования сигналов на выходах устройства и пропорциональное управляющему коду, посту- пающеьгу с выхода регистра 11.

С выхода УЛЗ 1 сигнал выдается на вькод 27 синхронизации устройства, а также на вход записи регистра 16, производя запись кода адрес- кого управления в этот регистр и тем самым подготавливая перезапись этого кода в регистр 17,которая осуществляется при окончании отсчета

п.

ственно счетчиков 32, 33 импульсов каналов 23 формирования. (J выхода элемента ИЛИ 12 сигнал длительностью Т нулевым уровнем поступает на вход управления счетчика 32 импульсов, на вход занесения регистра 44 и вход синхронизации D-триг- гера 29 каждого канала 23, а с выхода элемента ИЛИ 13 в следующем периоде следования сигналов - на вход управления счетчика импульсов 33, на вход занесения регистра 45 и вход синхронизации D-триггера 30.

На этом заканчивается цикл формирования первого периода следования импульсов на выходах 49 устройства. От момента загрузки кода в счетчик 5 импульсов начинается цикл формирования второго периода следования импульсов.

Как указывалось выше, на входы, управления счетчиков 32 и 33 им-, пульсов сигналы подаются с выходов элементов ИЛИ 12 и 13. Уровень логического О на входах управления этих счетчиков разрешает режим занесения кода в соответствугощиГ счетчик со старших разрядов ОЗУ 31.

После установления на входе управления соответствующего счетчика 32 и 33 единичного уровня разрешается режим счета на вычитание.. На выходе счетчиков 32, 33 сигнал выделяется при достиженяи ими нулевого состояния.

Таким образом, после отсчета счетчиком 5 импульсов первого временного интервала, определяющего, со- ставляющую первого периода следования сигналов на выходе 27 синхронизации, кратную значению Т, импульсный сигнал выдается на.выходе элемента ИЛИ 12.

Импульснб1й сигнал длительностью Т полоясительной полярности, выраба- тываемый на инверсном выходе D-триггера 6, поступает также на вход за- писи регистра 17, осуществляет перезапись кода в этот регистр с выхода регистра 16. В свою очередь, этот новый код с выхода регистра 17 через блок 22 поступает на адресные входы ОЗУ 8.

В зависимости от наличия переноса на выходе переноса сумматора 28 D-триггеры 29 и 30 каналов 23формирования переводятся сигналом по входу синхронизации либо в состояние

10

15

20

25

4А374512

логической 1 прн наличии переноса, либо в состояние логического О при отсутствии переноса. В зависимости от этого сигнал с Ъыхода счетчика 32 импульсов поступает через первый элемент ШШ-НЕ 36 на вход элемента ИЛИ 41. без задержки, либо через элемент 38 с задержкой на один такт, осуществляемой в D-триг- гер 34.

С выходов элементов ИЛИ-НЕ 36, 38 сигналы через элемент ИПИ-НЕ 43 поступают на йнформационньЕЙ вход блока 40 тактируемой задержки. Аналогично сигнал с вьгхода счетчика 33 в зависимости от состояния D-триггера 30 поступает через элемент ИПИ-НЕ 37 или 39 на входы элемента ИЛИ 42 и через элемент ШШ-НЕ 43 на вход блока 40 тактируемой задержки. Блок 40 тактируемой задержки осу-. ществляет задержку сигнала, поступающего с выхода элемента ИЛИ-НЕ 43 на время, достаточное для установки требуемого кода на управляющих входах УЛЗ 48. Это время должно быть не менее времени срабатывания мультиплексора 46 и времени выборки информации при смене адреса из ОЗУ 47 вместе взятых.

Блок 40 такт1фуемой задержки осуществляет задер;кку входного сигнала на время, кратное периоду генератора 2 опорной кварцевой частоты. На

УЛЗ 48 сигнал, поступающий с вьгхода блока 40, задерживается на время, определяемое кодом, поступающ1 м на ее управляющие входы с вьгхода ОЗУ 47. В свою очередь, адресное управление ОЗУ 47 осуществялется через мультиплексор -6 кодами с выходом регистров 44 и 45. Если осуществляется задержка сигнала, который соответствует сигналу, выработанно му на выходе счетчика 32 и прошедшему через элементы ИЛИ-НЕ 36 или 38, 43, блок 40, то ryльтиплeкcop 46 подключает к адресным входам ОЗУ 47 выходы регистра 44. Если осуществля-. ется задержка сигнала, выработанного на выходе счетч1 ка 43, подключается регистр 45. УЛЗ 48 осуществляет задержку сигнала на время, определяемое управляющим кодом, считываемым

55 с младших разрядов ОЗУ 31. Этот код совместно с кодом, поступаюии1м на второй вход сумматора 28, определяет содержимое регистров 44 и 45. Пезо

40

50

реключенне мультиплексора 46 осуществляется сигналагг1И, поступающими с ыходов элементов ИЛИ 41 н 42.

Загрузка счетчиков 32 и 33 производится поочередно один раэ за два периода следования сигналов на выходе синхронизации 26 устройства. Как указывалось выше, эта очередность задается С использованием счетного триггера 14, Это обеспечивает возможность формирования задержки сигналов на выходе 49 каналов 23 формирования в диапазоне двух периодов следования сигналов на выходе синхронизации 26 устройства. .

Таким образом, задержка сигнала, формируемая на УЛЗ 8 и 48 в текущем цикле работы устройства, определяется тем кодом, который считывается с соответствующего ОЗУ 21 или 47 калибровочных кодов. В то же время сам считываемый с ОЗУ 21 или 47 код оп- ределяется кодом на их адресных входах. При этом задержка, формируемая на УЛЗ 48, пропорциональна коду, поступающему на адресный вход соответствующего ОЗУ.

Содержимое ОЗУ. 21 и 47 определяется на этапе калибровки, которая также является процедурой, подготавливающей устройство к работе. Калибровка состоит в определении содержимого ОЗУ 21 и ОЗУ 47.

Содержимое ОЗУ 21 и 47 калибровочных кодов определяется в следующей последовательности.

При определении содержимого ОЗУ 21 выбирается режим работ блока 22,, обеспечивающий неизменное значение адреса на его вькоде. Код, считываемый с ОЗУ 8, должен иметь нулевое значение в младших ра зрядах. В этом случае с выхода регистра 10 и соот- .ветственно регистра 11 вьщается -нулевой код.

Состояние адресных входов ОЗУ 21 в этом случае определяется с исполь- .эованием регистра 15, информация в который заносится по информационной шине 25. Каждому коду.в регистре 15 (его разрядаость совпадает с разряд- Юностью регистра 11) ставится в соответствие пропорциональное этому значение задержки, формируемой УЛЗ 1.

Значение калибровочного кода, заносимого в ОЗУ 21 по адресу, определяемому содержимым регистра 15, подбирается при измерении взаимной за5

0

держки сигналов на выходах 26, 27 синхронизащш устройства. При этом разрядность ОЗУ 21 определяется только конкретной реализацией УЛЗ 1, Это дает возможность более простой .реализации УЛЗ 1, например, с меньшей разрядностью, а также с произвольным законом управления задержкой в зави- симости от кода управления.

По тому же принципу производится определение содержимого ОЗУ 47 каждого канала 23 формирования. При этом состояние адресных входов ОЗУ 31 также остается неизменным. По данному адресу в ОЗУ 31 заносится информация, изменяющая во всех возможных комбинациях состояние выходов младших разрядов данного ОЗУ, соединенньгх с входом сумматора 28 и входами регистров 44 и 45. Каждому коду в этих разрядах ОЗУ 31 должна соответствовать определенная задержка, формируемая на УЛЗ 48 и пропор5 циональная этому, коду. Подбор этой задержки производится путем подбора требуемого кода управления УЛЗ 48, который заносится в ОЗУ 47 по информационной шине 25 по адресу, задаваемому кодом на выходе младших разрядов ОЗУ 31. Этот же код .присутствует и на выходе регистров 44 и 45. Через мультиплексор 46 этот код поступает на адресные входы ОЗУ 47..

Калибровочный код, заносимый по данному адресу в ОЗУ 47, определяется при измерении взаимной задержки сигналов между выходом синхронизации 28 и выходом 49 устройства.

Сформированные на выходах 49 каналов 23 формирования сигналы с программно заданной задержкой между каналами и длительностью T,j могут быть использованы для формирования сигналов с программно зада заемой длительностью. Для этого выход одного из каналов 23 подключается к первому плечу формирующего триггера, а любой другой из каналов 23 подключа- . ется к второму плечу формирующего ..триггера. Подключение выходов каналов 23 к группе формирующих триггеров может осуществляться с использовани5 ем универсального коммутатора. Работа устройства в случае, если программируемый делитель 4 частоты вы- дает деленную в зависимости от запро0

5

0

5

0

15

граммнроБанного коэффициента часто ту, кратную опорной, поступающей с выхода пенератора 2 опорной кварцевой частоты, аналогична описанной. Отличие состоит в том, что в мпад- Ш1ТХ разрядах ОЗУ 8 и 3Г программируется нулевая информация. Дискрет- .ность программного управления в этом случае равна периоду следования импульсов на выходе программируемого делителя частоты А.

Формула изобретения

1, Многоканальное устройство для формирования импульсных последовательностей, содержащее счетный триггер, управляемую линию задержки, выход которой является первым выходом синхроЕ1изации устройства, генератор опорной кварцевой частоты, выход которого через ключ соединен с входом программируемого делителя частоты, выход которого соединен с . первым входом счетчика импульсов и с первьм входом первого D-триг- гера, второй вход которого соединен с выходом счетчика импульсов, а первый выход - с вторым входом счет- иика импульсов, третий вход которого через блок управления соединен с первым выходом оперативного запоминающего устройства, второй выход которого подключен к первому входу сумматора, первый выход которого через первый регистр соединен со своим вторым входом и первым входом второго регистра, второй выхсд суммато- ра соединен с вторым входом блока управления, второГ вход первого регистра соеди 1ен с вторым выходом первого D-триггера, а также каналы формирования, первый вход, каждого

из которых соединен с выходом программируемого делителя частоты, второй вход каждого канала формирования соединен с информационной шиной устройства, с первым входом оперативного запоминающего устройства и вторыми входами ключа, и программируемого делителя частоты, отличающееся тем, что, с целью повышения быстродействия и точности формирования временных интервалов,

20

,д вьм входом блока элементов ИЛИ, вт рой вход которого соединен с вьосод третьего регистра, вход которого соединен с информационной шиной ус ройства, первым входом блока выбор режима и первыг-, входом оперативног запоминающего устрх)йс тва капиброво - ньгх кодов, второй вход которого со единен с вьосодом блока элементов ИЛИ, а выход - с первым входом уп25 равляемой линии задержки, второй

вход которой соединен с выходом вт рого D-триггера, первый вход котор го соединен с выходом счетчика импульсов и входом счетного триггера первый и второй выходы которого со единены соответственно с первыми в дами первого и второго элементов 5-1ЛИ, вторые входы которых объедине и соединены с входом счетного триг гера, второй вход второго D-тригге соединен с первым входом счетчика пульсов, выход управляемой линии задержки- соедине с первым входом четвертого регистра, второй вход к торого соединен с агтресной шиной, выход - с первым входом пятого регистра, второй вход которого соеди нен.с вторым выходом первого D-три гера, а выход - с вторым входом бл ка выбора режима, выход которого с единен с вторым входом оперативног запоминающего устройства и шестым входом каждого канала формирования 2. Устройство по п.1, о т л и - чающееся тем, что канал фо мирования содержит сумматор, с пер вого по четвертый О-триггеры, оперативное запоминающее устройство, первый, второй счетчики импульсов, с первого по пятый элементы ИЛИ-НЕ

30

35

45

50

него введены первый, второй элементы 55 блок тактируемой задержки, первый.

второй элементы ИЛИ, первый, второ регистры, оперативное запоминающее устройство калибровочных кодов,ну

ИЛИ, третий четвертый и пятый регистры, линия задержки, второй D- триггер, блок элементов ИЛИ, опера,

1443745 6

тивное запоминающее устройство ка- I либровочных кодов, блок выбора ре

жима, причем второй вьп{од первого D-триггёра соединен вторым выходом сигосронизации устройства и через ли- |НИ1о задержки - с вторым входом второ- го регистра, парный вход которого соединен с третьим входом каждого канала формирования, четвертый и пятый входы каждого из которых соединены соответственно с выходом первого н выходом второго элементов ИЛИ, выход второго регистра соединен с лервьм входом блока элементов ИЛИ, второй вход которого соединен с вьосодом третьего регистра, вход которого соединен с информационной шиной устройства, первым входом блока выбора режима и первыг-, входом оперативного запоминающего устрх)йс тва капибровоч- ньгх кодов, второй вход которого соединен с вьосодом блока элементов ИЛИ, а выход - с первым входом управляемой линии задержки, второй

вход которой соединен с выходом второго D-триггера, первый вход которого соединен с выходом счетчика импульсов и входом счетного триггера, первый и второй выходы которого соединены соответственно с первыми входами первого и второго элементов 5-1ЛИ, вторые входы которых объединены и соединены с входом счетного триггера, второй вход второго D-триггера соединен с первым входом счетчика импульсов, выход управляемой линии задержки- соедине с первым входом четвертого регистра, второй вход которого соединен с агтресной шиной, а выход - с первым входом пятого регистра, второй вход которого соединен.с вторым выходом первого D-триггера, а выход - с вторым входом блока выбора режима, выход которого соединен с вторым входом оперативного запоминающего устройства и шестым входом каждого канала формирования. 2. Устройство по п.1, о т л и - чающееся тем, что канал формирования содержит сумматор, с первого по четвертый О-триггеры, оперативное запоминающее устройство, первый, второй счетчики импульсов, с первого по пятый элементы ИЛИ-НЕ,

блок тактируемой задержки, первый.

второй элементы ИЛИ, первый, второй регистры, оперативное запоминающее устройство калибровочных кодов,нультиплексор, yпpaвпяe tyкJ линию задержки, причем первый выход сумматора соедннён с первцмй входами первого и второго D-триггеров, первый выход оперативного заломинающего устрой-, ства соединен с первым входом сумматора, второй выход оперативного запоминающего устройства соединен С первыми входами первого и рторого счетчиков импульсов, вторые входы которых объединены, выходы первого | второго счетчиков импульсов соответственно соединены с первыми входами третьего и четвертого D-триггеров и первого и второго элементов 1 ШИ-НЕ, вторые входы которых соединены соответственно с первыми выходами первого и второго D-триггеров, вторые выходы которых соединены соответственно с первыми входами третьего и четвертого элементов ИЛИ-НЕ : вторые которых соединены соот ; ветственно с выходами третьего и четвертого D-триггеров, вторые входы которых объединены и соединены с вторыми входами первого, второго счетчиков импульсов, с первым входом блока тактируемой задержки и с . первьм входом канала формирования, выход первого элемента 1ШИ-НЕ соединен с первыми входами первого элемета ШШ и - пятого элемента ИЛИ-ПЕ, вьгход третьего элемента ИЛИ-НЕ соеднен с вторыми входа ш перво-го эле- мента 1ШИ и пятого элемента ШИ-НЕ, выход второго элемента Rm-i-HE соединен с первым входом второго элемента ИЛИ к третьим входом пятого эле- . мента ИЛИ-ЯЕ, выход четвертого элемента ИЛИ-НЕ соединен с четвертью fвходом пятого- элемента ИЛИ-НЕ и вто

5

0

рьм входом второго элемента ИЛИ,второй вход первого О-тркггера соединен с третьим входом первого счетчика импульсов, с четвертым входом канала формирования и с первым входом первого регистра, второй вход которого соединен с вторым выходом сумматора и с первьм входом второго регистра, вьЕХоды которого соединены с первыми входами мультиплексора, вторые входы которого соединены с выходами первого регистра, а третий и четвертый входы соединены соответственно с выходами первого и второго,элементов ИЛИ, выход мультиплексора соединен с первым входом оперативного запоминающего устройства калибровочных кодов, выход которого соединен с первым входом управляемой линией задержки, второй вход которой соединен с выходом блока тактируемой задержки, второй вход которого соединен с выходом пятого элемента ИЛИ-НЕ, вто- 5 рой вход второго В-тригге.ра соединен с третьим входом второго счетчика импульсов, с пятым входом канала формирования и с вторьим входом второго регистра, третий вход которого соединен с третьим входом первого регистра и с третьим выходом опера- ративного запоминающего устройства, первый вход которого соединен с вторым входом оперативного запоминающего устройства калибровочных кодов и с вторым входом канала формирования, второй вход оперативного запоминающего устройства соединен с шестым входом канала формирования, а второй вход сумматора является третьи - входом канала форми- , рования.

0

5

0

| Многоканальное устройство для формирования импульсных последовательностей | 1982 |

|

SU1077539A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-09-23—Публикация

1987-02-24—Подача