ключей к первым входам первого и второго D-триггеров, первый выход оперативного запоминающего устройства соединен с первым входом сумматора, второй выход оперативного запоминающего устройства подключен к первым входам первого и второго счетчиков импульсов, вторые входы которых объединены, выходы первого и второго счетчиков импульсов соответ-i ствекно соединены с первыми входами третьего и четвертого D-триггеров и первого и второго элементов ШШ-НЕ, вторые входа третьего и четвертого D-триггеров объединены и подключены ко вторым входам счетчиков импульсов и к первым входам пятого и шестого D-триггеров, вторые входы которых соответственно подключены к выходам первого и третьего элементов ИЛИ-НЕ и второго и четвертого элементов ШШ-НЕ, второй вход первого элемента ИЛИ-НЕ подключен к первому выходу первого D-триггера, второй выход которого соединен с первым входом. третьего элемента ИЛИ-НЕ, второй вход которого соединен с выходом второго .D-триггера, выход четвертого D-триггера подключен к первому входу четвертого элемента ШШ-НЕ, второй вход которого соединен с первым выходом второго D-триггера, второй выход которого подключен ко второму

входу второго элемента ИЛИ-НЕ, причем второй вход первого D-триггера подключен к третьему входу первого счетчика импульсов,к первому входу канала формирования и к первому входу первого регистра, второй вход которого соединен со вторым выходом сумматора и с первым входом второго регистра, выходы которого подключены к первым входам мультиплексора, вторые входы которого соединены с выходами первого регистра, третий вход мультиплексора соединен с выходами пятого и шестого D-триггеров и первым входом управляемой линии задержки, второй вход которой соединен с выходом мультиплексора, выход управляемой линии задержки является выходом данного формирователя, импульсов, второй вход второго регистра подключен ко второму входу второго D-триггера, к третьему входу второго счетчика импульсов и к четвертому входу канала формирования, первый вход оперативного запоминающего устройства является вторым входом канала формирования, второй вход является третьим входом канала формирования, второй вход сумматора является шестым входом канала формирования, а вторые входы счетчиков импульсов являются пятым входом канала формирования.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для формирования импульсных последовательностей | 1987 |

|

SU1443745A1 |

| Способ магнитной записи асинхронных потоков цифровой информации и устройство для его осуществления | 1990 |

|

SU1788520A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Система для передачи телеизмерительной информации | 1982 |

|

SU1113832A1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| УСТРОЙСТВО ЗАДЕРЖКИ ИМПУЛЬСОВ | 2008 |

|

RU2386208C1 |

| Устройство для функционального контроля интегральных схем | 1988 |

|

SU1737465A1 |

| АВТОМАТИЧЕСКИЙ СЛЕДЯЩИЙ ДЕЛИТЕЛЬ ПЕРИОДОВ ИМПУЛЬСНЫХ СИГНАЛОВ | 1992 |

|

RU2105410C1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ВРЕМЕННОГО ИНТЕРВАЛА | 1991 |

|

RU2040854C1 |

1. МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ИМПУЛЬСНЫХ ПОСЛЕДОВATEЛЬНОСТЕЙ, содержащее генератор опорной кварцевой частоты, программируе1« 1й делитель частоты, выход которого соединен с первым входом счетчика импульсов, первый вход программируемого делителя частоты соединен с первым входом оперативного запоминающего.устройства, первый выход которого подключен к первому входу сумматора, выход которого через первый регистр подключен к своему второму входу и к первому входу второго регистра, выход которого подключен к первому входу управляемой линии задержки, выход которой соединен с вторьм входом второго регистра, второй вход управляемой линии задержки соединен непосредственно с первыми входами первого и второго элементов И-НЕ и через счетный триггер с вторыми входами первого и второго элементов И-НЕ, а также каналы формирования, первьй вход каждого из которых соединен с выходом первого элемента И-НЕ, второй вход каждого канала формирования подключен к первому входу оперативного запоминающего устройства, третий вход каждого канала формирования соединен с вторым входом оперативного запоминающего устройства, отличающееся тем, что, с целью повьипения быстродействия и повышения точности работы устройства, в него введены ключ, блок управления и D-триггер, причем выход второго элемента И-НЕ соединен с четвертым входом каждого . канала формирования, первый вход ,В-триггера подключен к первому входу и к пятому счетчика импульсов входу каждого канала формирования, а второй.вход подключен к выходу счетчика импульсов, первый выход ,- V D-триггера соединен со вторым вхо дом первого регистра и со входом счетного триггера, второй выход D-триггера подключен к второму входу Л счетчика импульсов, третий вход которого соединен с выходом блока управления, первый вход которого соединен со вторым выходом оперативного запоминающего устройства, второй I вход блока управления соединен с выходом, сумматора, а первый вход ключа соединен с выходом генератора опор ной кварцевой частоты, выход ключа подключен ко второму входу программируемого делителя частоты, второй вход которого подключен ко второму входу ключа, причем выход второго регистра соединен с шестым входом каждого канала формирования. 2. Многоканальное устройство для формирования импульсных последовательностей по п. 1, отличающееся тем, что каждый канал формирования состоит из двух формирователей импульсов, выходы которых подключены ко входам триггера, а каждый формирователь импульсов содержит сумматор, выход которого под

Изобретение относится к импульсной технике и может быть использовано для управлениявременными интервалами тестовых и синхронизирующих Яоследовательностей сигналов в автоматизированных комплексах функционального и параметрического контроля БИС оперативных запоминающих устройств (ОЗУ) и БИС микропроцессоров, а также в качестве системы синхрониза ции быстродействующих ЭВМ,

Известно многоканальное устройство для формирования импульсных последовательностей, содержащее генератор импульсов, формир рватель и п каналов формирования.

Недостатками этого устройства является то, что генератор импульсоз

работает в старт-стопном режиме, поэтому в качестве генератора импульсов не могут быть использованы высокостабильные и точные генераторы 5 опорной частоты с кварцевой стабилизацией, работающие в непрерывном режиме. Это существенно снижает точность формирования временных интервалов. Диапазон задания задержки

10 и длительности импульсов синхронизации в данном устройстве не может быть более периода их следования. Кроме того, отсутствует возможность ; управления периодом следования,

15 задержкой и длительностью импульсов синхронизации на частоте их следования (в реальном масштабе времени),

что снижает возможность функционального контроля БИС.

Наиболее близким техническим решением к данному изобретению является устройство для формирования импульсных последовательностей, содержащее генератор опорной кварцевой частоты, программный делитель частоты, соединенный со счетчиком импульсов, два блока формирования набора фаз тактовых частот, два селектора фаз тактовых частот, последовательно соединенные первый и второй регистры, первый и второй сумматоры, первый счетчик импульсов, первую управляемую линию задержки, первое ОЗУ, счетный триггер, выходы которого соединены с первыми и вторыми элементами И-НЕ и п каналов формирования.

Недостатком данного устройства является ограниченное быстродействие обусловленное тем, что необходимость ,выбора новой фазы тактовой частоты вначале каждого цикла формирования временных интервалов, обусловливает запрет тактовой частоты в конце каждого цикла на несколько периодов следования импульсов синхронизации.

Кроме того, погрешность, связанная с селективным выбором фазы тактовой частоты, снижает точность формирования задержки и длительности импульсов синхронизации.

Составляющими этой погрешности являются:

погрешность взаимного положения фаз на выходах блока формирования набора фаз тактовых частот;

погрешность, обусловленная разницей задержек распространения сигналов с разных входов каждого селектора фаз тактовых частот на его выходJ

погрешность, обусловленная разницей собственных задержек распространения сигналов через первый и второй селекторы фаз тактовых частот.

Целью изобретения является увеличение быстродействия и повышение точности устройства.

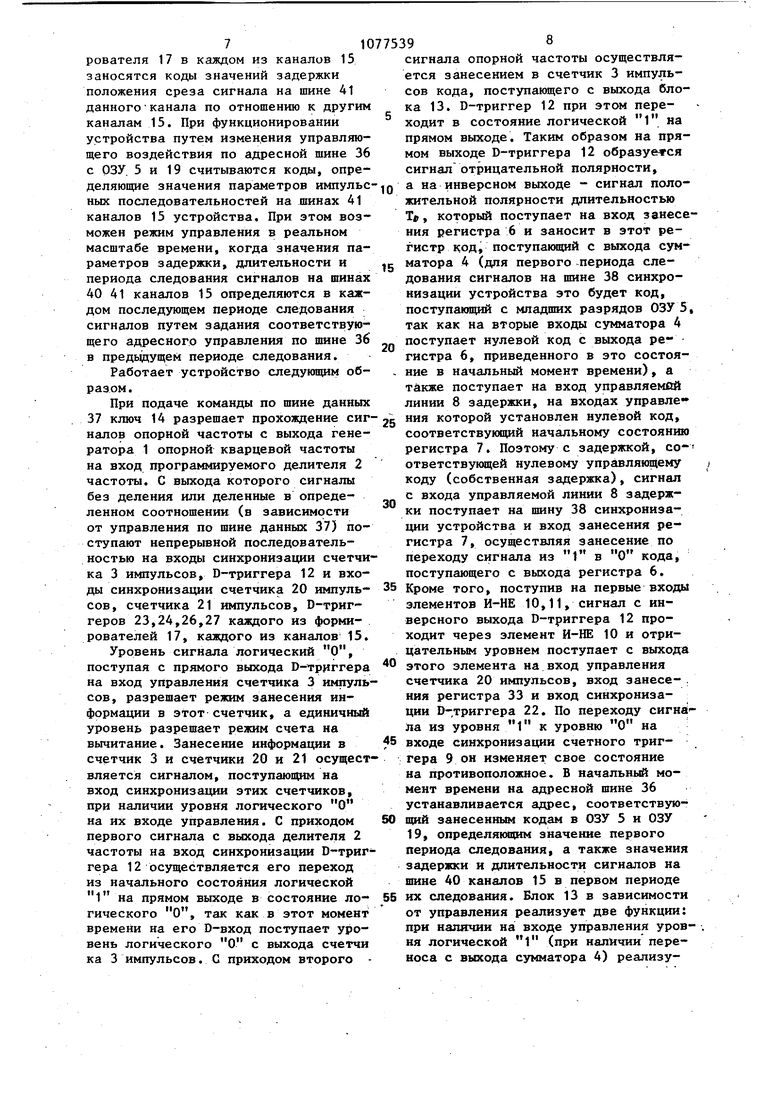

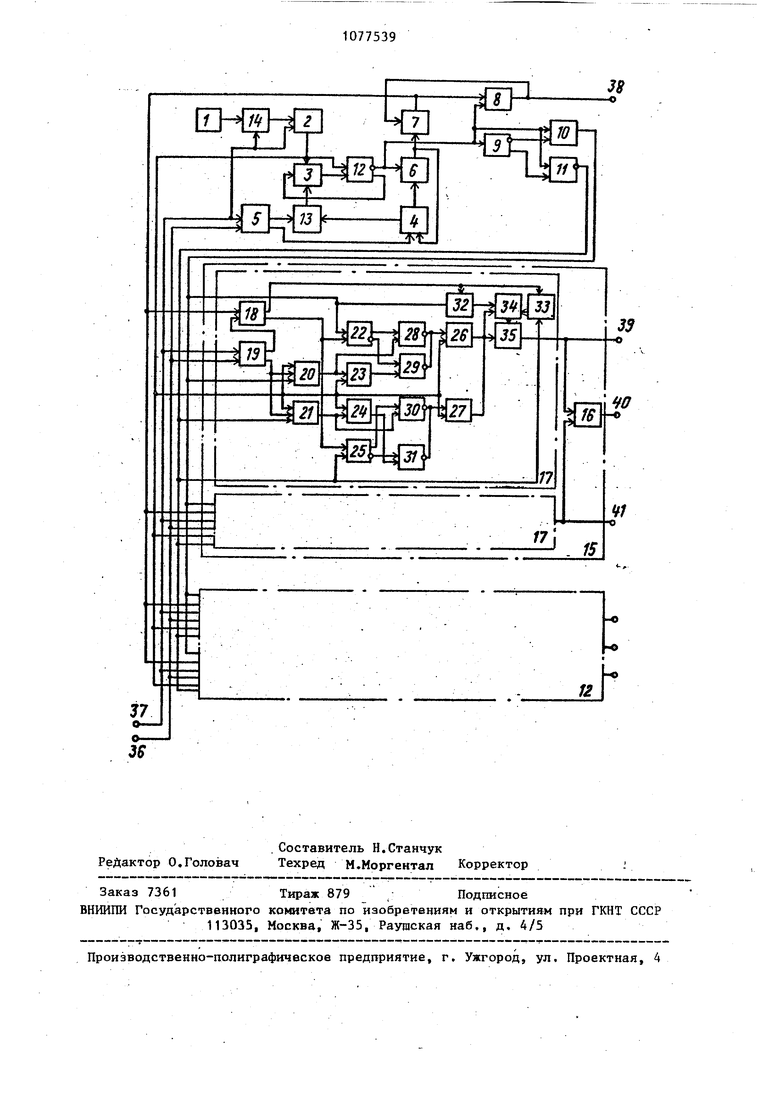

Поставленная цель достигается тем, что в многоканальное устройство для формирования импульсных последовательностей, содержащее генератор . опорной кварцевой частоты, программируемый делитель частоты, выход кото-55 ходы которых подключены ко входам рого соединен с первым входом счет- триггера, а каждый формирователь имчика импульсов, первый вход програм- пульсов содержит сумматор, выходкомируемого делителя частоты соединен . с первым входом оперативного запоминающего устройства, первый выход которого подключен к первому входу сумматора, выход которого через первый регистр подключен к своему второму входу и к первому входу второго регистра, выход которого подключен к первому входу управляемой линии задержки, выход которой соединен со вторым входом второго регистра, второй вход управляемой линии задержки соединен непосредственно с первыми входами первого и второго элементов И-НЕ и через счетный триггер со вторыми входами первого и второго элементов И-НЕ, а также каналы формирования, первый вход каждого из которых соединен с выходом первого зле мента И-НЕ, второй вход каждого канала формирования подключен к первому входу оперативного запоминающего устройства, третий вход каждого канала формирования соединен с вторым входом оперативного запоминающего yctройства, в него введены ключ, блок . управления и D-триггер, причем выход второго элемента И-НЕ соединен с четвертым входом каждого канала формирования, первый вход В-триггера подключен к первому входу счетчика импульсов и к пятому входу каждого канала формирования, а второй вход подключен к выходу счетчика импуль- сов, первый выход D-триггера соеди.; ней со вторым входом первого регистра и с входом счетного триггера, второй выход D-триггера подключен к второму входу счетчика импульсов, третий вход которого соединен с выходом блока управления, первый вход которого соединен с вторым выходом оперативного запоминающего устрой- ства, второй вход блока управления соединен с выходом сумматора, а первый вход ключа соединен с выходом 5 генератора опорной кварцевой частоты, выход ключа подключен ко второ- : му входу программируемого делителя частоты, второй вход которого подключен ко второму входу ключа, причем ; выход второго регистра соединен с шестым входом каждого канала формирования, а также тем, что в нем каждый канал формирования состоит из двух формирователей импульсов, выторого подключен к первым входам первого и второго D-триггеров, первый вход оперативного запоминающего устройства соединен с первым входом сумматора, второй выход оперативного запоминающего устройства подключен к первым входам первого и второго счетчика импульсов, вторые входы которых объединены, выходы первого и второго счетчиков импульсов соответственно соединены с первыми входа ми третьего и четвертого D-триггеров и первого и второго элементов ИЛИ-НЕ вторые входы третьего и четвертого D-триггеров объединены и подключены к вторым входам счетчиков импульсов и к первым входам пятого и шестого D-триггеров, вторые входы которых соответственно подключены к выходам первого и третьего элементов ИЛИ-НЕ и второго и четвертого элементов ИЛИ-НЕ, второй вход первого элемента ИЛИ-НЕ подключен к первому выходу первого D-триггера, выход которого соединен с первым входом третьего элемента ИЛИ-НЕ, второй вход которого соединен с выходом второго D-триг гера, выход четвертого D-триггера подключен к первому входу четвертого элемента ИЛИ-НЕ, второй вход которого соединен с первым выходом второго D-триггера, второй выход которого подключен к второму входу второго элемента ИЛИ-НЁ, причем второй вход первого D-триггера подключен к треть му входу первого счётчика, к первому входу каналов формирования и к первому входу первого регистра, второй вход которого соединен со вторым выходом сумматора и с перзвым входом второго регистра, выходы которого подключены к первым входам мультиплексора, вторые входы которого соединены с выходами первого регистра, третий вход мультиплексора соединен с выходами пятого и шестого триггеро и первым входом управляемой линии задержки, второй вход которой соединен с выходом мультиплексора, выход управляемой линии задержки является выходом данного формирователя импульсов, второй вход второго регистра подключен ко второму входу второго D-триггера, к третьему входувторого счетчика импульсов и к четвертому входу канала формирования, первый вход оперативного запоминающего устройства является вторым входом канала формирования, второй вход является третьим входом канала форми рования, второй вход сумматора является шестым входом канала формирования, а вторые входы счетчиков импульсов являются пятым входом канала формирования. Йа чертеже представлена функциональная схема многоканального устройства дпя формирования импульсных последовательностей. Устройство содержит генератор 1 опорной кварцевой частоты, программный делитель 2 частоты, счетчик 3 импульсов, сумматор 4, оперативное запоминающее устройство (ОЗУ) 5, регистры 6,7, управляемую линию 8 задержки, счетный триггер 9, элемент И-НЕ 10,11,- D-триггер 12, блок 13 управления, ключ 14, каналы 15 формирования, состоящие из триггера 16 и двух формирователей 17, калсдый из которых содержит сумматор 18, оперативное запоминающее устройство (ОЗУ) 19, счетчики 20, 21 импульсов, D-триггеры 22-27, элементы ИЛИ-НЕ 28-31, регистры 32,33, мультиплексор 34, управляемую линию 35 задержки, шину 36 данных, адресную шину 37, выходную шину 38 синхронизации, выходные шины 39, 40, 41. Шины начальной установки на чертеже условно не показаны. Значение периода Тд генератора 1 выбирается в соответствии с весовым коэффициентом младшего из разрядов кодов, поступающих из ОЗУ 5, 19 на счетчики 20, 21 и блок 13. Значения задержки звеньев управляемых линий. 8,36 задержки выбираются в соответствии с весовыми коэффициентами разрядов кодов, поступающих с младших разрядов ОЗУ 5 и 19 на сумматоры 4 и 18. В начальный момент времени счетчик 3 импульсов, регистры 6,7, счетный триггер 9, D-триггеры 22-27, триггер 16 приводятся в нулевое состояние, D-триггер 12, счетчики импульсов 20 и 21 приводятся в единичное состояние. В ОЗУ 5 и 19 заносятся коды тре буемых эначений параметров импульсных последовательностей. В ОЗУ 5 заносятся коды значений периода следования импульсов на шине 38 синхронизации и на шинах 40 каналов 15, в ОЗУ 19 в каждом из каналов 15 заносятся коды значений задержки положения фронта сигнала на шине 40 данного канала сигналов, на шинах 40 других каналов 15, в ОЗУ 19 формирователя 17 в каждом из каналов 15 заносятся коды значений задержки положения среза сигнала на шине 41 данногоканала по отношению к другим каналам 15. При функционировании устройства путем измен,ения управляющего воздействия по адресной шине 36 с ОЗУ. 5 и 19 считываются коды, определяющие значения параметров импульс ных последовательностей на шинах 41 каналов 15 устройства. При этом возможен режим управления в реальном масштабе времени, когда значения параметров задержки, длительности и периода следования сигналов на шинах 40 41 каналов 15 определяются в каждом последующем периоде следования сигналов путем задания соответствующего адресного управления по шине Зб в предьщущем периоде следования. Работает устройство следующим образом. При подаче команды по шине данных 37 ключ 14 разрешает прохождение сиг налов опорной частоты с выхода генератора 1 опорной кварцевой частоты на вход программируемого делителя 2 частоты. С выхода которого сигналы без деления или деленные в определенном соотношении (в зависимости от управления по шине данных 37) поступают непрерывной последовательностью на входы синхронизации счетчи ка 3 импульсов, D-триггера 12 и входы синхронизации счетчика 20 импульсов, счетчика 21 импульсов, D-триггеров 23,24,26,27 каяздого из формирователей 17, каждого из каналов 15. Уровень сигнала логический О, поступая с прямого выхода D-триггера на вход управления счетчика 3 импуль сов, разрешает режим занесения информации в этот счетчик, а единичный уровень разрешает режим счета на вычитание. Занесение информации в счетчик 3 и счетчики 20 и 21 осущест вляется сигналом, поступающим на вход синхронизации этих счетчиков, при наличии уровня логического на их входе управления. С приходом первого сигнала с выхода делителя 2 частоты на вход синхронизации D-триг гера 12 осуществляется его переход из начального состояния логической

1 на прямом выходе в состояние ло-55 их следования. Блок 13 в зависимости

гического О, так как в этот моментот управления реализует две функции:

времени на его D-вход поступает уро-при наличии на входе угфавления уроввень логического О с выхода счетчиня логической 1 (при наличии перека 3 импульсов. С приходом второго -носа с выхода сумматора 4) реализусигнала опорной частоты осуществляется занесением в счетчик 3 импульсов кода, поступающего с выхода блока 13. D-триггер 12 при этом переходит в состояние логической 1 на прямом выходе. Таким образом на прямом выходе D-триггера 12 образуется сигнал отрицательной полярности. а на инверсном выходе - сигнал положительной полярности длительностью Тц, который поступает на вход занесения регистра 6 и заносит в этот регистр код, посту пакнций с выхода сумматора 4 (для первого периода следования сигналов на шине 38 синхронизации устройства это будет код, поступакиций с младших разрядов ОЗУ 5, так как на вторые входы сумматора 4 поступает нулевой код с выхода регистра 6, приведенного в это состояние в начальный момент времени), а также поступает на вход управляемой линии 8 задержки, на входах управле ия которой установлен нулевой код, соответствующий начальному состоянию регистра 7. Поэтому с задержкой, со- ответствующей нулевому управляющему коду (собственная задержка), сигнал с входа управляемой линии 8 задержки поступает на шину 38 синхронизации устройства и вход занесения регистра 7, осуществляя занесение по переходу сигнала из 1 в О кода, поступающего с выхода регистра 6. Кроме того, поступив на первые входы элементов И-НЕ 10,11, сигнал с инверсного выхода D-триггера 12 проходит через элемент И-НЕ 10 и отрицательным уровнем поступает с выхода этого элемента на вход управления счетчика 20 импульсов, вход занесе- . НИИ регистра 33 и вход синхронизации 0-,триггера 22. По переходу сигнй ла из уровня 1 к уровню О на входе синхронизации счетного триггера 9 он изменяет свое состояние на противоположное. В начальный момент времени на адресной шине 36 устанавливается адрес, соответствующий занесенным кодам в ОЗУ 5 и ОЗУ 19, определяющим значение первого периода следования, а также значения задержки и длительности сигналов на шине 40 каналов 15 в первом периоде ется функция f( А-1, при наличии на входе управления уровня логического О реализуется функция , где А - код на входе блока 13 Для начального момента времени перенос на выходе сумматора 4 отсутствует, так как на вторые входы его подается код 0000 с выхода регистра 6. Поэтому блок. 13 реализует функцию f 2 . Начиная с третьего сигнала опорной частоты на входе синхронизации счетчик 3 импульсов начинает счет на вычитание продолжающийся до момента, пока счетчик 3 не обнулится, при этом на выходе счетчика 3 устанавливается уровень логического О через такт опорной частоты устанавливается на выходе D-триггера 12. К этому моменту времени на выходах ОЗУ 5 и ОЗУ 19 устанавлива,ют за счет управления по адресной шине 36 коды, определяющие значения параметров импульсных сигналов импульсной последовательности на шинах 39,40,41 каналов 15 устройства во втором периоде их следования. При наличии уровня О на входе управления счетчика 3 импульсов осуществляется его загрузка кодом с выхода блока 13. D-триггер 12 в этом же такте переходит в уровень логической 1 на прямым выходе, а сигна с его инверсного выхода, поступив Ни вход первой управляемой линии задержки, и задержавшись на время S-6 , где S. - дискретность задания периода следования импульсов синхронизации, в- код, поступающий с выходов регистра 7 на входы управления управляемой линии задержки, поступает на шину 38. Этот же сигнал с инверсного выхода D-триггера 12 заносит код с выходов сумматора в регист 6, а также, поступив на первый вход элемента И-НЕ 11, на второй вход которого поступает уровень логической 1 с прямого выхода счетного триггера 9, поступает ровнем логического о с выхода элемента И-НЕ 11 на вход управления счетчика 21 импульсов, на вход занесения регистра 33 и 1вход синхронизации D-триггера 25 каждого канала 15. Сигнал с шины 38 устройства осуществляет также занесение кода в регистр 7. При этом оканчивается цикл формирования первого периода следования импульсов на шине 38 устройства. От момента загрузки кода в счетчик 3 импульсов начинается цикл формирования второго периода следования импульсов . Формирование положения фронта и среза импульсов на выходе каналов 15 осуществляется следукщим образом. Как указьшалось, на входы управления счетчиков 20, 21 импульсов сигналы подаются с выходов элементов И-НЕ 10 и 11. Уровень логического О на входах управления этих счетчиков разрешает режим занесения кода в счетчик с 1 старших разрядов второго ОЗУ 19. После занесения кодов в счетчики 20,21 разрешается режим счета на вычитание, на выходе счетчиков 20,21 сигнала выделяется при достижении ими нулевого состояния. В зависимости от наличия переноса на выходе переноса сумматора 18, D-триггеры 22,25 переводятся сигналом по входу синхронизации либо в состояние логической 1 при наличии переноса, либо в состояние логического О при отсутствии переноса. В зависимости от этого сигнал с выхоДа счетчика 20 импульсов поступает через элемент ИЛИ-НЕ на вход D-триггера 26 без задержки, либо через элемент ИЛИ-НЕ с задержкой на один такт, осуществляемой на D-триггере 23. Сигнал с D-входа D-триггера 26 с задержкой на такт поступает на вход управляемой линии 36 задержки, на которой задерживается на время, пропорциональное коду, занесенному в регистр 33, В регистры 32,33 кода заносятся с выхода сумматора 18, на первые входы которого подается код с выхода регистра 7, а на вторые входы - с выходов т-младших разрядов ОЗУ 19. Сигнал с выхода D-триггера поступает также на вход селекции мультиплексора 36 и переклк|чает мультиплексор 34 через время не менее чем максимальная задержка сигнала на управляемой линии 35 задержки таким образом, что он коммутирует на входы управления управляемой задержки код с выходов регистров 33. Во втором периоде следования сигналов на шинах 39-41 каналов 15 загрузка кода с 1-старших разрядов ОЗУ 19 осуществляется в счетчик 21 импульсов, а с выходов сумматора 18 - в регистр 33, 34. В остальном работа счетчика 21 импульсов элементов ШШ-НЕ 30 и 31 D-триг.геров 26,24 и 25 аналогична работе счетчика 20 импульсов ИЛИ-НЕ 28,29, D-триггеров 22,23,26. Сигнал с выхода D-триггера 27 поступает на вход управляемой линии 35 задержки. Сигна лы с выхода управляемой линии 35 задержки формирователя поступают на шину 39 канала 15 и на R - вход триг гера 16, определяя тем самым положение фронта сигнала на шине 40 канала 15. За счет того, что счетчики 20, 21 импульсов загружаются один раз за два периода следования сигналов на шине 38. синхронизации устрой ства возможно формирование задержки и длительности импульсов на шинах 39,40,41 каналов 15 в пределах двух периодов их следования. Работа всех формирователей 17 аналогична. С выхода управляемой линии 35 задержки формирователя 17 сигналы поступают на шину 41 каналов 15 и S - вход триггера 16, определяя положение среза сигнала на шине 40 канала 15. Таким образом, на шинах 38,39,40, 41 устройства формируются импульсные последовательности сигналов с программно управляемыми значениями пара- Q лов метров сигналов. На шине 38 синхронизации устройства выдаются сигналы положительной полярности, период следования которы определяется состоянием выходов ОЗУ 5, которые могут изменяться от перио да к периоду следования в зависимости от внешнего управления по адресной шине 36. На шине 40 каналов 15 выдаются сигналы, следующие с тем же периодом следования, что и на шине 38 устройства. Причем взаимное положение этих сигналов в различных каналах 15 друг по отношению к другу в пределах данного периода следования, а именно положение фронта и среза сигнала, определяется состоянием выходов ОЗУ 19 формирователей 16 соответственно. Так как адресная шина 36 соединена со всеми ОЗУ параллельно, то изме

нение периода следования, положения фронта и среза импульсов синхронизации на всех шинах каналов 15 проис-

временем запрета опорной частоты, необходимым для выбора новой фазы опорной частоты в начале каждого цикла. ходит одновременно (при изменении адресного управления). В том случае, если адресное управление остается неизменным устройство выдает импульсные последовательности в обычном генераторном режиме, без изменения параметров сигналов от периода к периоду следования. На шинах 39 каналов 15 сигналы выдаются синхронно с положением фронта и среза импульса соответственно на шине 40 каналов 15. Работа устройства в случае, если делитель 2 частоты выдает деленную в зависимости от запрограммированного коэффициента частоту, кратную опорной, поступающей с выхода генератора 1 опорной кварцевой частоты, аналогична описанной. Отличие состо ит в том, что в m младших разрядах ОЗУ 5 и ОЗУ 19 программируется нулевая информация. Дискретность программного задания значений параметров сигналов в этом случае равна периоду сигналов на выходе делителя 2 частоты. Таким образом, в данном устройстве по сравнению с известными, формирование временных параметров сигнана выходах каналов 15 с требуемой дискретностью программирования S, много меньшей периода TO сигналов опорной частоты, с возможностью управления в реальном масштабе времени, осуществляется при тактировании счетчиков импульсов и триггеров непрерывной последовательностью сигналов опорной частоты. Это исключает составляющие погрешности формирования временных интервалов, обусловленные селективным выбором фазы опорной частоты в начале каждого цикла формирования воеменных интервалов, присущие прототипу. Также за счет того что сигналы опорной частоты тактируют счетчики импульсов непрерывной последовательностью, эти счетчикт импульсов могут работать с коэффициентами пересчета, ограниченными только техническими характеристиками амих счетчиков и не ограниченными

J7

ooзе

/5

в

f

| Многоканальный генератор импульсов | 1977 |

|

SU670067A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Фирма Fairchied США, The .high resolution timingsystem, 1979. | |||

Авторы

Даты

1989-01-15—Публикация

1982-01-29—Подача