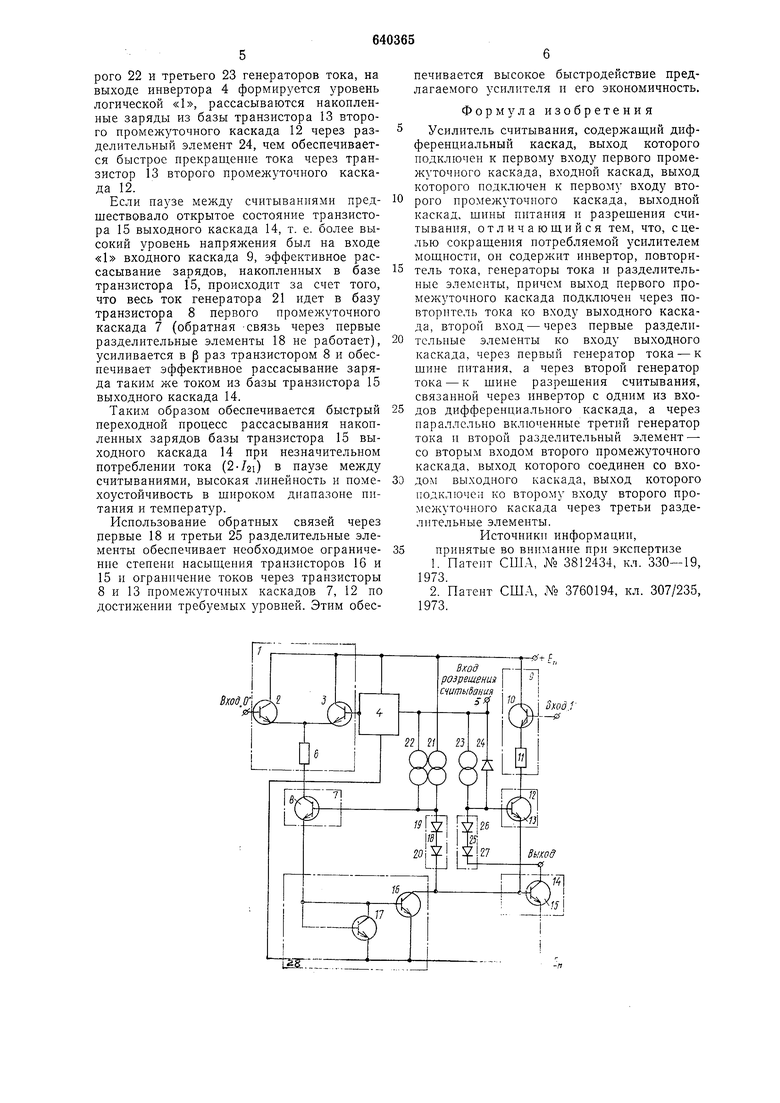

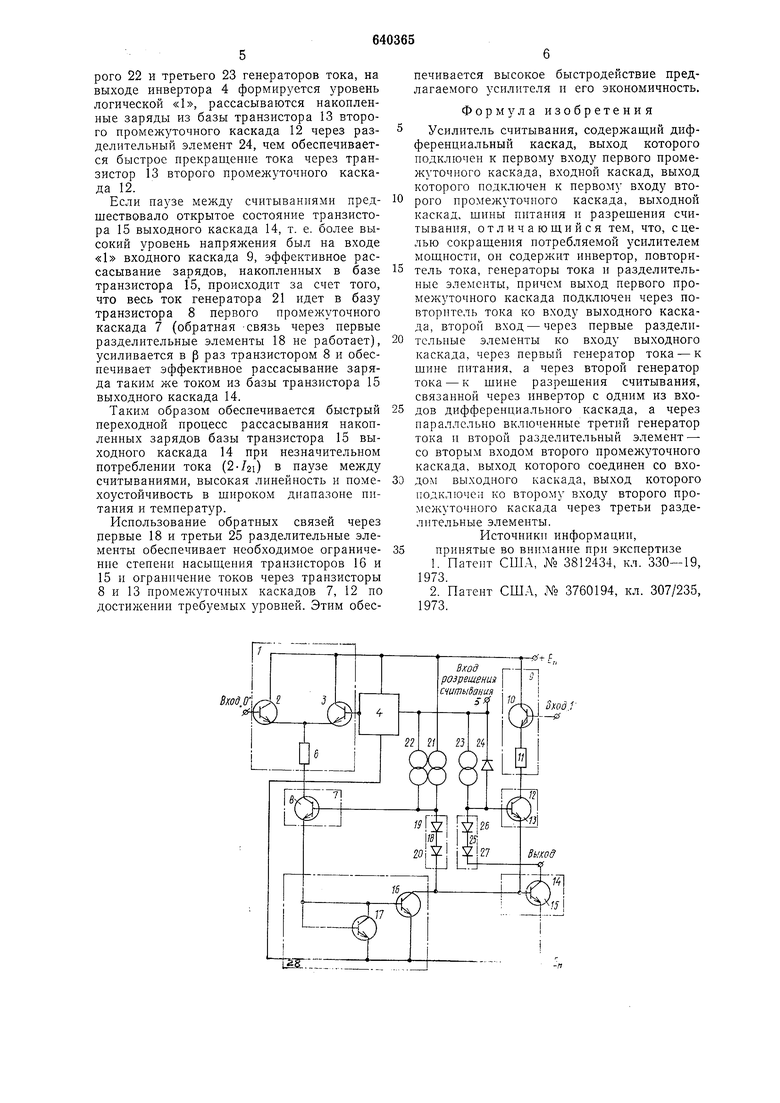

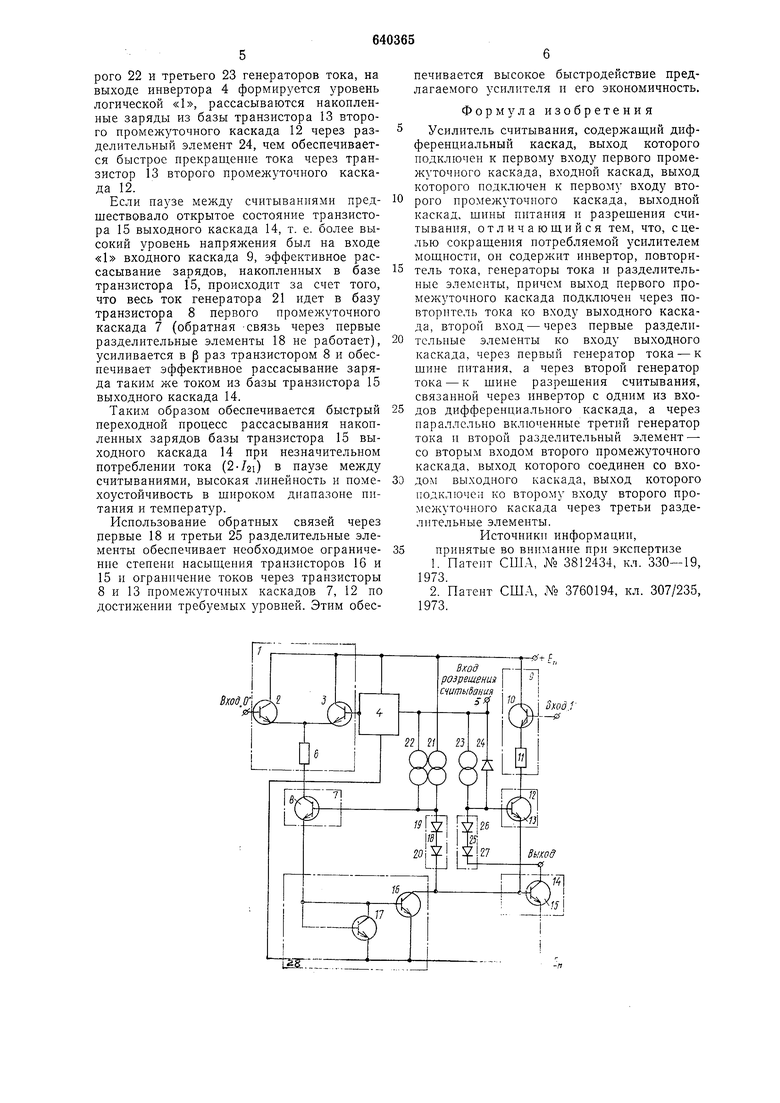

5 разрешения считывания, а также резистор 6, связывающий выход дифференциального каскада - эмиттеры транзисторов 2 и 3 с первым входом нервого промежуточного каскада 7 - коллектором транзистора 8.

Входной каскад 9 содержит транзистор 10, база которого связана с входом «1 заноминающего устройства, и резистор И, связывающий выход входного каскада 9- эмиттер транзистора 10 с иервым входом второго промежуточиого каскада 12 - коллектором транзистора 13.

Выходной каскад 14 содержит выходной транзистор 15, база которого соединена с выходом второго промежуточного каскада 12 - эмиттером транзистора 13 и коллектором 16, база которого связана с базой н коллектором транзистора 17 и выходом первого промежуточного каскада 7 - эмиттером транзистора 8.

База выходного транзистора 15 через первые разделительные элементы 18, содерлсащие последовательно соединенные диоды 19 и 20, подключена ко второму входу первого промежуточного каскада 7 - база транзистора 8, которая через первый генератор тока 21 связана с шиной питания -J-fn, а через второй генератор тока 22 - с шиной 5 разрешения считывания, к которой также через параллельно включенный третий генератор тока 23 и второй разделительный элемент - диод 24 подключен второй вход второго промежуточиого каскада 12 - база транзистора 13, которая связана через третьи разделительпые элементы 25, состоящие из последовательно соединенных диодов 26 и 27, с выходом усилителя - коллектором транзистора 15.

Диоды 19, 18, 24, 26, 27 подключены к базам транзисторов 8 и 12 полярностью, соответствующей полярности базовых областей упомянутых транзисторов 8, 12 относительно их эмиттеров или коллекторов.

Усилитель считывания работает следующим образом.

В паузе между считываниями транзистор 13 второго промежуточного каскада закрыт, а транзистор 8 первого промежуточного каскада 7 находится в активном режиме, определяемом постоянным током генератора тока 21 (/ 21), который распределяется между входом транзистора 8 первого промежуточного каскада и первыми разделительными элементами 18 на базу транзистора 15 выходного каскада 14.

Коэффициент передачи повторителя тока 28 равен единице. Поэтому входной ток повторителя тока 28 - /Б8(И-р) равен току /21-/Б8 в цепи первых разделительных элементов 18, т. е. /БЗ (l+p)/2i-/БВ,

откуда /Б8 , где /БВ - базовый ток

+ р транзистора 8 первого промежуточного

каскада 7, а р - коэффициент усиления по току транзистора 8.

Поэтому общее потребление усилителя в паузе между считываниями не превышает (2-/21), уровень напряжения при этом на базе транзистора 15 выходного каскада 14 равен Уоэ8+ бУ1б - 19- 20, чем обеспечивается надежное закрытое состояние транзистора 15.

При считывании на шине 5 разрешения формируется уровень логической «1, открывается транзистор 13 второго промежуточного каскада 12 через управляемый импульсом разрешения третий генератор тока 23 и увеличивается входной ток транзистора 8 первого промежуточного каскада 7 через управляемый импульсом разрешения второй генератор тока 22 так, что входные токи транзисторов 8 и 13 промежуточных каскадов 7, 12 становятся одинаковыми. Разделительный элемент 24 при этом закрыт.

Пнвертор 4 формирует на входе транзистора 3 дифференциального каскада 1 логический «О.

Усилитель отрабатывает разность потенциалов между входами «О и «1 запоминающего устройства. Б зависимости от того, на каком входе более высокий уровень

напряжения, открывается транзистор 16 повторителя тока 28 или транзистор 14 выходного каскада 14. При равенстве потенциалов на входах «О или «1 токи через транзисторы 8, 13 равны, и транзистор 16

обеспечивает закрытое состояние транзистора 15, чем исключается возможность появления помех на выходе при переходных процессах в запоминающем устройстве. Уровень выходного напряжения на выхоДе усилителя - коллекторе транзистора 15 при наличии более высокого уровня напряжения на входе входного каскада 9, чем на входе «О дифференциального каскада 1, определяется разницей /эб12 + эб14- f 26-

-и27 и может при необходимости задаваться в пределах 0,1-0,3 В.

При наличии более высокого уровня напряжения на входе «О дифференциального каскада 1, чем на входе «1 входного

каскада 9, напряжение на базе транзистора 15 определяется из выражения /эб8+, + эб1б- 19- 2о которое аналогично вышеприведенному выражению для определения напряжения в паузе между считываниями.

Согласование входного сопротивления усилителя с выходным сопротивлением запоминающего устройства и ограничение токов при переходных процессах считывания

обеспечивают резисторы 6 и 11 соответственно дифференциального 1 и входного 7 каскадов.

После прекращения импульса разрешения считывания (формируется зфовень логического «О) прекращаются токи от вто

| название | год | авторы | номер документа |

|---|---|---|---|

| Операционный усилитель | 1972 |

|

SU468254A1 |

| Восстановитель постоянной составляющей импульсных сигналов напряжения | 1982 |

|

SU1069148A1 |

| Интегральный усилитель для стереофонической аппаратуры магнитной записи | 1979 |

|

SU1003138A1 |

| УСИЛИТЕЛЬ СЧИТЫВАНИЯ | 1973 |

|

SU374656A1 |

| Усилитель записи - считывания | 1989 |

|

SU1674250A1 |

| Широкополосный операционный усилитель | 1983 |

|

SU1223338A1 |

| Операционный усилитель | 1980 |

|

SU970638A1 |

| Амплитудный детектор | 1978 |

|

SU718884A1 |

| Операционный усилитель | 1973 |

|

SU470815A1 |

| Операционный усилитель | 1989 |

|

SU1721614A1 |

Авторы

Даты

1978-12-30—Публикация

1976-04-05—Подача