3 7

//

/Jo-I

Т D

19

7

19

Л15

Ю

-оЈ об

О

2

Ю СП

о

-r

Ис

ю

Изобретение относится к вычислительной технике и может быть использовано при построении интегральных микросхем.

Целью изобретения является повышение быстродействия.

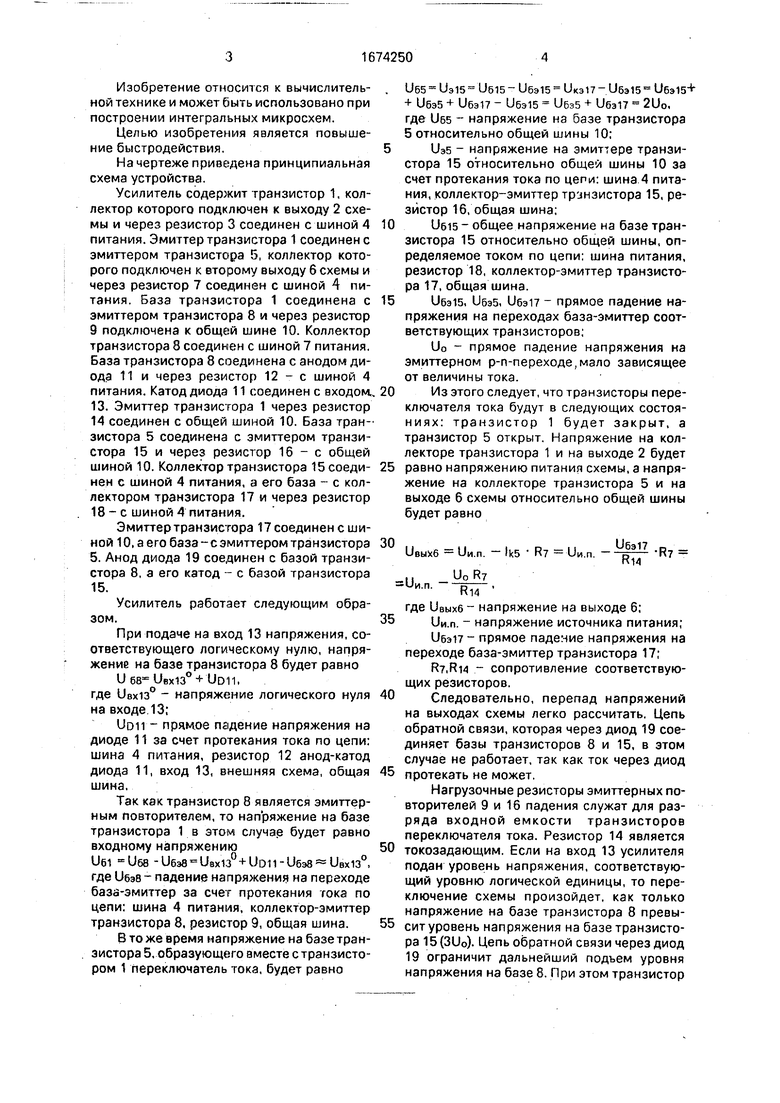

На чертеже приведена принципиальная схема устройства.

Усилитель содержит транзистор 1, коллектор которого подключен к выходу 2 схемы и через резистор 3 соединен с шиной 4 питания. Эмиттер транзистора 1 соединено эмиттером транзистора 5, коллектор которого подключен к второму выходу б схемы и через резистор 7 соединен с шиной 4 питания. База транзистора 1 соединена с эмиттером транзистора 8 и через резистор 9 подключена к общей шине 10. Коллектор транзистора 8 соединен с шиной 7 питания. База транзистора 8 соединена с анодом диода 11 и через резистор 12 - с шиной 4 питания. Катод диода 11 соединен с входом 13. Эмиттер транзистора 1 через резистор 14 соединен с общей шиной 10. База транзистора 5 соединена с эмиттером транзистора 15 и через резистор 16 - с общей шиной 10. Коллектор транзистора 15соеди- нем с шиной 4 питания, а его база - с коллектором транзистора 17 и через резистор 18 - с шиной 4 питания.

Эмиттер транзистора 17 соединен с шиной 10, а его база - с эмиттером транзистора 5. Анод диода 19 соединен с базой транзистора 8. а его катод - с базой транзистора 15.

Усилитель работает следующим образом.

При подаче на вход 13 напряжения, соответствующего логическому нулю, напряжение на базе транзистора 8 будет равно

U68-UBX13°+UD11.

где Uexi3° - напряжение логического нуля на входе 13;

UDII прямое падение напряжения на диоде 11 за счет протекания тока по цепи: шина 4 питания, резистор 12 анод-катод диода 11, вход 13, внешняя схема, общая шина.

Так как транзистор 8 является эмиттер- ным повторителем, то напряжение на базе транзистора 1 в этом случае будет равно входному напряжению

U61 - U68 - Убэв- UBx13°+ UD11 - U638 « UBx13°,

где Убэв - падение напряжения на переходе база-эмиттер за счет протекания тока по цепи: шина 4 питания, коллектор-эмиттер транзистора 8, резистор 9, общая шина.

В то же время напряжение на базе транзистора 5, образующего вместе с транзистором 1 переключатель тока, будет равно

U65 Ua15 U&15 - 1)бэ15 1)кэ17 - 1)бэ15 - U6315 + УбэБ + 11бэ17 11бэ15 U635 + 11бэ17 - 2UO,

где U65 - напряжение на базе транзистора 5 относительно общей шины 10;

1)э5 - напряжение на эмиттере транзистора 15 относительно общей шины 10 за счет протекания тока по цепи: шина 4 питания, коллектор-эмиттер транзистора 15, резистор 16, общая шина:

1)б15 - общее напряжение на базе транзистора 15 относительно общей шины, определяемое током по цепи: шина питания, резистор 18, коллектор-эмиттер транзистора 17, общая шина.

U6315, 11бэ5. 11бэ17 - прямое падение напряжения на переходах база-эмиттер соответствующих транзисторов;

Do - прямое падение напряжения на эмиттерном р-п-переходе,мало зависящее от величины тока.

Из этого следует, что транзисторы переключателя тока будут в следующих состояниях: транзистор 1 будет закрыт, а транзистор 5 открыт. Напряжение на коллекторе транзистора 1 и на выходе 2 будет равно напряжению питания схемы, а напряжение на коллекторе транзистора 5 и на выходе 6 схемы относительно общей шины будет равно

Квыхб Уи.п. - IkS R7 Un.n. - t -R7

RH

ии.п. UoR7R14

где 11Выхб - напряжение на выходе 6;

ии.п. - напряжение источника питания;

11бэ17 - прямое падение напряжения на переходе база-эмиттер транзистора 17;

R7.Ri4 - сопротивление соответствующих резисторов.

Следовательно, перепад напряжений на выходах схемы легко рассчитать. Цепь обратной связи, которая через диод 19 соединяет базы транзисторов 8 и 15. в этом случае не работает, так как ток через диод протекать не может.

Нагрузочные резисторы эмиттерных повторителей 9 и 16 падения служат для разряда входной емкости транзисторов переключателя тока. Резистор 14 является токозадающим. Если на вход 13 усилителя подан уровень напряжения, соответствующий уровню логической единицы, то переключение схемы произойдет, как только напряжение на базе транзистора 8 превысит уровень напряжения на базе транзистора 15 (3U0). Цепь обратной связи через диод 19 ограничит дальнейший подъем уровня напряжения на базе 8. При этом транзистор

1 откроется, а транзистор 5 закроется. Напряжения на выходах схемы 6 и 2 в этом случае будут: Увыхб Уи.п;

U0R3

Uebix2 UM п.

R14

Из описания работы схемы следует, что напряжение на базе открытого транзистора переключателя тока лишь незначительно превышает уровень 2U0, что делает возможным, не опасаясь насыщения транзистора, увеличить-величину перепада по сравнению с прототипом на инверсном выходе усилителя примерно на 2Uo, а на прямом - на Uo. Формула изобретения Усилитель записи-считывания, содер- жащий дифференциальный каскад, коллекторы первого и второго транзисторов которого являются выходами усилителя и соединены соответственно с первыми выводами первого и второго резисторов, вторые выводы которых соединены с шиной питания, эмиттеры транзисторов дифференциального каскада объединены и соединены с первым выводом третьего резистора, генератор тока на транзисторе, база которого соединена с первым выводом третьего резистора, второй вывод которого соединен с эмиттером транзистора генератора тока и с шиной нулевого потенциала. первый и второй эмиттерные повторители на транзисторах, коллекторы которых соединены с шиной Питания, отличающийся тем, что, с целью повышения быстродействия усилителя, эмиттеры транзисторов эмиттер- ных повторителей соединены соответственно с базами первого и второго транзисторов дифференциального каскада и с первыми выводами четвертого и пятого резисторов, вторые выводы которых соединены с шиной нулевого потенциала, базы транзисторов первого и второго эмиттерных повторителей соединены соответственно с первыми выводами шестого и седьмого резисторов, вторые выводы которых соединены с шиной питания, база транзисторов первого эмит- терного повторителя соединена с анодами первого и второго ограничительных диодов, база транзистора второго эмиттерного повторителя соединена с катодом второго ограничительного диода и с коллектором транзистора генератора тока, кэтод первого ограничительного диода является входом усилителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь уровня сигнала для усилителя считывания | 1983 |

|

SU1134966A1 |

| Усилитель считывания | 1986 |

|

SU1368918A1 |

| Усилитель считывания | 1988 |

|

SU1580441A1 |

| Усилитель считывания | 1985 |

|

SU1280450A1 |

| Формирователь логических перепадов | 1987 |

|

SU1531157A1 |

| Усилитель считывания | 1986 |

|

SU1316045A1 |

| УСИЛИТЕЛЬ МОЩНОСТИ | 1990 |

|

RU1748611C |

| Логический элемент | 1982 |

|

SU1058061A1 |

| Эмиттерно-связанный элемент | 1988 |

|

SU1629985A1 |

| Усилитель считывания | 1984 |

|

SU1231600A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении интегральных микросхем. Цель изобретения - получение на выходах буферного каскада большего логического перепада без резкого снижения быстродействия. Усилитель содержит дифференциальный каскад на транзисторах 1 и 5 с эмиттерными повторителями на входе транзистора 15, источник опорного напряжения на транзисторе 17, ограничительные диоды 11 и 19. Усилитель характеризуется отсутствием насаждения транзисторов за счет ограничения входного сигнала уровнем, не превышающим верхнего опорного уровня, изменяемого входным сигналом. 1 ил.

| Устройство управления записью-считыванием информации для полупроводникового запоминающего устройства | 1986 |

|

SU1367040A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Усилитель считывания | 1986 |

|

SU1368918A1 |

| кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1991-08-30—Публикация

1989-05-31—Подача