элемента разрешения, выполненного (з влде м,ноговходОВОго элемента НЕ-И, выход которого соедилен с вторыми ;входа1М,и вентилей, выходы Которых являются выходами 6л10,ка преобразования синдрома в вектор ошибки.

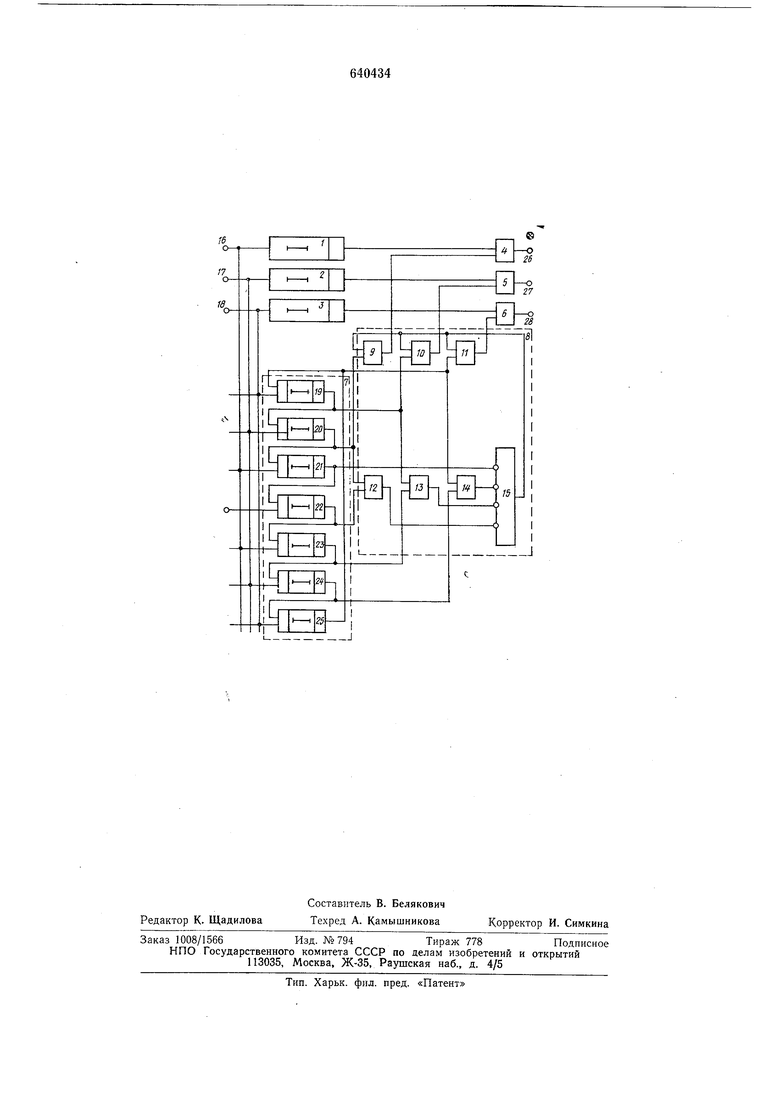

На чертеже пред-ставлена структурная элекиричеокая схема устройства для ИСтаравленяя «шибок в кадалах /связи с побайтной лвредачей .информации для байта ,из трбх Д|вом41ных символов.

Устройство содержит буферные регистры I/-3, ,по числу ДВОИЧ1НЫХ элементов в байте, выходы которых подключены к первым входам соответствующих -корректирующих сумматоров 4-6, вторые входы .которых 4eipe3 последовательно соединенные кольцевой регистр 7 вычисления синдрома, состоящий из элементов задержки ,и сумматоров по модулю два, и бло1К 8 преобразо,ва1ния синдрома в вектор о-ши&ки, состОЯ-щшй из вентилей 9-11, cyMMiaTopOB 12-14 И элемента /5 разрешетаия, соединены с вхойа-ми .16-18 буферных регистров , причем кольцевой регистр 7 вычисления синдроiM-a состоят из одинаковых ячеек 19-25 «по числу байтов в ,коде, из которых одна ячейка 21 принята за центр кольцевого регистра 7 вычисления синдрома, при этом первый вход -каждой ячейки 19-25 соединен с выходом предыдущей, вторые входы я-чеек 19, 20, 21, 23, 24, 25, равноотстоящих от ячейки 22, следующ-ей после центральной ячейки 21 ло ходу сдвига кольцевого регистра 7 вычисления синдр-oMia, о-бъединены и являются входа1ми аюльцевого регистр.а 7 вычисления синд1р-ома, а выходы первых ячеек 20, 19, 25 мз каждой я-ары ячеек 20 я 22, 19 .и 23, 25 л 24, равноотстоящих от центра, соединены ic пэрвьш-и входами соответствующих вентнл-ей 9-1/7 и сумматоров 12-il4 бло«а 8 иреобразования оиндро-ма в вектор ошибки, причем вторые .входы сумматоров 12-14 с-оедин-ены с выходами соответствующих вторых ячеек 22-24 указанных пар ячеек 20 и 22, ,19 и 23, 25 и 24 кольцевого регистр.а 7 вычисления аинд-рома, .выход центральной ячейКИ KOTOiporo и выходы сумматоров 12-14 подключены к входам элемента 15 р«азр-еш-ен1ия, выполненного в виде многоВходового элемента Н-Е-И, выход KOToiporo соединен с вторыми входами вентилей 9-11, вых-оды Которых являются .выходами блока 8 лреобразованвя синдрома в вектор ошибки, и ВЫХОДЫ 26-28.

Устройство работает следующим образом.

Байты поступают на входы 16-18 устройства ПОочередНО с тактом в одну -еди1ни|цу.времени и подаются (В буферные регистры /- я ячейки /5-25 кольцевого регистра 7. Перед началам npHCMia кольцевой регистр 7 обнуляется.

РаССМОтрим ход вьгаисления синдрома. Числ-о элементов Оиндром-а равно числу

строк Проверочной матрицы, и -каждый элемент определяется как результат сложения по м-одулю два содержимого тех разрядов кода, которые отмечены е(Диницами в соответствующей стр-оке нроверочной -матрицы. Проверочная матрица 1кода вмеет вид

, 5Яо, SWo, ..., S«//o,

где Яо - приведенная исходная подматрица (-она же подматрица первого байта Я,

0010100 1

I 0100010 1000001 J

(Размер байта b 3, число байтов . Подматрица каждого следующего байта -абразуется .из подматрицы предыдущего Сявигом на одну строку вверх);

S - оператор .циклического сдвига строк подматрицы на одну строку -вверх.

-При этом в-ектор - столбец синдрома

определяется как

С 1Х, + SX, + , + ... -г ,, где вектор-столбец

Xi Xi,, Xt,, Х„ О, X,,, X;,, Xty,

где Х; -содержимое /-того р.азряда /-того байта, .а сложение производится по модулю два. Отсюда следует, что если -поврежден -i-тый байт блока и вектор ошибки этого байта е, е, , то синдром имеет вид

С-5--1 ен, е.,, е„ О, е,, в.,, е,т.

В /кольцевом репистре 7 (вычисление .с-индром.а производитоя в соответствии с формулой

5-6-С S- S- |5-1 fS- S-1 О + Х, 4+ Х., + ...+Х,

которая получается из приведенной ранее путем умножения обеих частей ее на оператор 5 и вынесения общих множителей за скобки.

-Вычисление синдрома завер-щается в течение седьмого такта .и поступление сигнал-ов -на входы устройства прекращается. -С восьмого по четырнадцатый такт байты принятой инфор.мацин поступают из ячеек .памяти буфер.ных регистр-ов 7-3 через корректирующие сумматоры 4-б1на выходы 26-28 устр-ойст1ва, а сигналы -синдрома в 1КОЛЬцево.м регистре 7 сдвигаются с каждым тактом на о.дну ячейку. Пр.и выдаче из ячеек памяти буфер.ных -регистров

1-3 Н0Врежд1енн-ого байта прямой и зеркалыный отражен.ный векторы аипнала ошибок этого байта 1расположены на выходах кольцевого регистра 7 симметрично относительно нуля на выходе центральной ячейки 21. Эта оим-метрня обна1руж,ивается цосредCTBQM -сумматоров ,12-14 и элем-ента 15. П|р.и этом вместе с вектором прииятого лойреждеиного байта иа корректирующие сумматдры 4-6 через вентил1И поступает такж-е И вектор аш,иб,ки этого байта. В ipeзультате с выходов 26-28 онимается инфо/рмащия € исправленными ошибками. Построение устройства при других размерах байта аналогично.

Использоваиие изобретения позволит предельно упростить устройство исправления ошлбок для различных разм е/ров байта Ь, удовлетворяющих условию 2Ы-1 - простое число, и, в частности, для общепринятого байта Ь 8. Кольцевой регистр 7 и блок 8 приобретают однородную структуру. Число ячеек 19-25 кольцевого регистра 7 лишь на единицу больше наинизшей теоретической траницы.

.Блок 5 предельно упрощен, емкость ячеек ламяпи буферных регистров -3 .и число ко;рректируюших сумматоров 4-6 минимальны, что приводит к снижению веса, габаритов, стоимости :и повышению надежности устройства.

Формула и 3 о б ip е т ея и я

Устройство для исправления ошибок в каналах связи с побайтной передачей инфармации при длине кода, равной простому числу, на единицу превышающему удвоенный размер банта, содержащее буферные регистры, по числу двоичных элементов в байте, выходы которых подключены к первым входам соответствующих корректирующих сумматоров, вторые входы которых через последовательно соединенные кольцевой регистр вычисления синдрома, состоящий из элементов задержки и сумматоров по модулю два, и блок преобразования синдрома ,в вектор ошибки, состоящий из вентилей, сумматоров и элемента разрешения, соединены с входами буферных регистров, отличающееся тем, что, с целью упрощения устройства, кольцевой регистр вычисления синдрома состоит из одинаковых ячеек по числу байтов в жоде, из которых одна принята за центр кольцевого регистра вычисления синдрома, при этом первый вход каждой ячейки соединен с выходом предыдущей, вторые входы ячеек, равноотстоящих от ячейки, следующей после централыной ячейки по ходу сдвига кольцевого регистра вычисления синдрома, объединены 1И 1Я,вляются входами кольцевого регистра вычисления синдрома, а выходы первых ячеек из каждой пары ячеек, равноотстоящих от центра, соединены с первыми входами соответствующих вентилей .и сумматоров блока преобразования Синдрома в вектор ошибки, ,приче1М вторые входы сумматоров соединены с выходами соответствующих вторых ячеек указанных пар ячеек кольцевого регистра вычисления синдрома, выход центральной ячейки которого И выходы сумматоров подключены « входам элемента разрешения, 1вьшолненного в виде многовходового элемента , выхОд которого соединен с вторыми входами вентилей, выходы -которых ЯВЛЯЮТСЯ выходами блока преобразования синдрома в вектор ошибки.

Источник 1информадш1, принятый во внимание гори Э(кспертизе:

1. D. Mandelbaum, Some easily decoded efficient burst error correiting codes. Information and Control, V. 23, 1973, p. 234-244.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения местоположения ошибок в строке матричного накопителя | 1980 |

|

SU896691A1 |

| Устройство защиты от ошибок внешней памяти | 1981 |

|

SU1018119A1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| Матричное вычислительное устройство | 1990 |

|

SU1833890A1 |

| Устройство обнаружения и исправления ошибок в кодах Рида-Соломона | 1986 |

|

SU1381719A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| Устройство для защиты от ошибок в памяти | 1982 |

|

SU1151969A1 |

| Устройство для исправления ошибок в блоке памяти | 1978 |

|

SU868841A1 |

Авторы

Даты

1978-12-30—Публикация

1976-06-02—Подача