второй группой входов третьего блока перемножения, группа вьпсодов которого соединена с группой входав третьего блока элементов И, выход первого элемента ИЛИ-НЕ соединен с вторыми входами четвертого элемента ВДИ-НЕ и первого элемента И. выход которого соединен с вторым входом второго эле мента и, выход третьего элемента ИЛИ-на соединен с первьшн входами первого элемента И и четвертого элемента ИЛИ-НЕ, выход которого соединен с вторым входом третьего элемента И, выход которого соединен с первым входом элемента ИЛИ и с управляющим вНодом третьего блока элвг ментов И, группа выходов которого соединена с первой группой входов третьего сумматора, выход второго элемента ЙЛИ-НЕ соединен с первыми входами третьего и второго элементов И, выход второго элемента И соединен с вторым выходом элемента, ИЛИ,

выход которого соединен с управляющим; :входрм второго бЛока элементов И, группа выходов которого соединена с второй группой входов третьего сумматора, группа выходов которого является ,группой выходов вычислителя рцибРК, кроме того в устройство введены первый и второй коммутаторы, причем группы выходов блока вычисления синдромов соединены с соответствующими группами входов первого коммутатора, четьфе группы выходов которого - соединены с соответствуилцими труппамк входов вычислителя ошибок, группа выходов которого соединена с первой группой входов второго коммутатора, три группы выходов которого соединены с соответствующими группами ,вх6дов первого блока буферной памяти, три других группы входов второго коммутатора соединены с соответстг

вующими группами выходов блока кодеров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство обнаружения и исправления ошибок в кодах Рида-Соломона | 1986 |

|

SU1381719A1 |

| Устройство для защиты от ошибок в памяти | 1982 |

|

SU1151969A1 |

| Устройство кодирования и вычисления синдромов помехоустойчивых кодов для коррекции ошибок во внешней памяти ЭВМ | 1989 |

|

SU1656689A1 |

| Устройство для исправления ошибок | 1987 |

|

SU1432787A1 |

| Устройство для исправления ошибок | 1984 |

|

SU1216832A1 |

| Кодек на основе кода Рида - Маллера первого порядка | 1990 |

|

SU1777243A1 |

| Устройство декодирования циклических кодов | 1990 |

|

SU1735996A2 |

| Декодирующее устройство для исправления ошибок | 1985 |

|

SU1295531A1 |

| Устройство для исправления стираний | 1989 |

|

SU1633498A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ КАСКАДНОГО КОДА РИДА-СОЛОМОНА | 1993 |

|

RU2036512C1 |

УС5 РОЙСТВО ЗАЩИТЫ ОТ ОШИБОК ВНЕШНЕЙ ПАМЯТИ, ссщержашее последовательносо циненные тремя группами свядей приёмный сдвиговый регистр, блок кодерОВ, первый блок элементов U и блок вычислеиия сиидасялрв. а также вычЕИОпите Фь ошибок, -выходной сумматор по модулю два, первый и второй блоки буферной памяти, выходы KOTOIXJX соединены соответственно с первьо4 и вторым входами выходного сумматора по модутпо два, выход которого является выходом ycTjionftcTBa три группы входов второго блока буферной памяти соединеиы с тремя группами выходов приемного сдвигового регистра, вход которого является входом устройства о т л ич а ю щ ее с л тем, что, с целью упрощения устройства при перёмежеиий символов кода Рида-Солсшона, вычислитель ошибок содержит блок сумматоров. первый, вхррой и третий блоки перемножения, первый и второй блоки возведения в квадрат, блок нахозкдения обратного элемента, первый, второй и третий сумматоры, первый, второй(Третий и четвертый элементы ИЛИ-НЕ. первый, второй и третий элементы И. элемент 1ШИ, ТВорой и третий блоки элементов И. причем первая группа входов вычислителя ошибок, соединена с первыми группами входов блока сумматоров и первого блока перемножения, груьпа выходов которого соединена с первой группой входов первого сумматора, вто-, рая группа входов вычислителя ошибок соединена с второй, третьей и четвертой группами входов блока сумматоров, с группой входов первого блока возведения в квадрат и с группой входов второго блока эле1.«ентов И, третья группа входов вычислителя ошибок (соединена с пятой и шестой группами входов блока сумматоров и с второй группрй вхрдов первого блока перемиожения, ;четвертая группа входов вычислителя ошибок соединена с седьмой и восьмой групп 1ми входов блока су1 маторов, группа выходов первого блока возведения в квадрат соединена с второй группой входов первого суьадатора, группа выходов которого соединена с группой входов перйого элемента ШШ-НЕ, первая и третья 00 группы выходов блока сумаатрров соединены с соответствующими группами входов второго блока перемножения, группа .выходов которого соединена с первой группой входов второго сумсо матора, вторая группа выходов блока сумматот ов соединена с группой входов второго блока возведения в квадрат группа выходов которого соединена с первой группой входов третьего блока перемножения и второй группой входов второго сумматора, группа выходов которого соединена с группрй .ВХОДО1В второго элемента ИЛИ-НЕ. четвв1 тый выход блока сумматоров соединеи с группой входов третьего элемента ИЛИ-НЕ и группой входов блока нахождения обратного элемента. группа выходов кбторого соединена с

Изобретение относится к вычислительной технике, а именно к специализированным вычислительным устройствам защиты от ошибок внешней памяти ЦВМ, и может быэув использовано дл автоматического контроля и исправления ошибок.

Известно устройство ппя. кодирования и декодирования помехоустойчивого кода Рида-Соломона PC-кода ) в си темах хранения и передачи данных, со держащее буферную память информационных час$ей кодавых слов, кодер, декодер, включающий блок вычисления и хранения синдромов и параллель но поеледовательнай ВЕлчислитель локаторов и значений ошибок, и выходной сумматор по модулю двар J.

Известное устройство характеризуется относительно большой сложностью вычислителя даже при небольшом числе исправляемых х:имврлов, равном трем.

Известно такяш устройство для обнаружения и исправления оЬщбок в оптико-механичеоком 83У, осаованное на БЧХгкоде и пере1уюжении. двоичных символов кодовых слов. Упрощение данного устройства достигается применением коза/ исправля1швего .небольшое число независимых одноСитовьос ошибок. При 3foH для сохранения эффективности устройства в его кодере идекодере содержатся дополнительно перемежатель я деперемежательСз }

Недостатком устройства является ;сло58ность перемежателя и деп€ ремежа теля, внесение на диски ЗУ существенной дополнительной избыточности в связи с отбрасыванием неисправимых- декодером секторов дорожек, а : также снижение скорости обмена информацией с ВЗУ повторной перезаписи .

Наиболее близким по технической сущности к изобретение является устройство для декодирования недвоичных БЧХ-кодов, в частности и PC-кодов, имеющее по сравнению с другими известными устройствами меньшую сложность при достаточно высоких исправляющей способности и быстродействии. Указанное устройство содержит последовательно соединенные друг с другом приемный сдвиговый регистр; блок кодеров, блок вентилей, блок вычисления и хранения синдромов, (вычислитель ошибок, блок буферной памяти и выходной сумматор по модулю дваСЗ. и

Недостаток устройства - сложность вьлчислителя ошибок, который даже при небольшом числе исправляемых ошибок, равном двум, содержит 25 блоков элементов И, для управления которыми (а .тёисже Для организации сдвигов информации ) требуется 33 микрооперации устройства управления.

Цель .изобретения - упрощение устройства при перемежении символов кода Рида-Соломона.

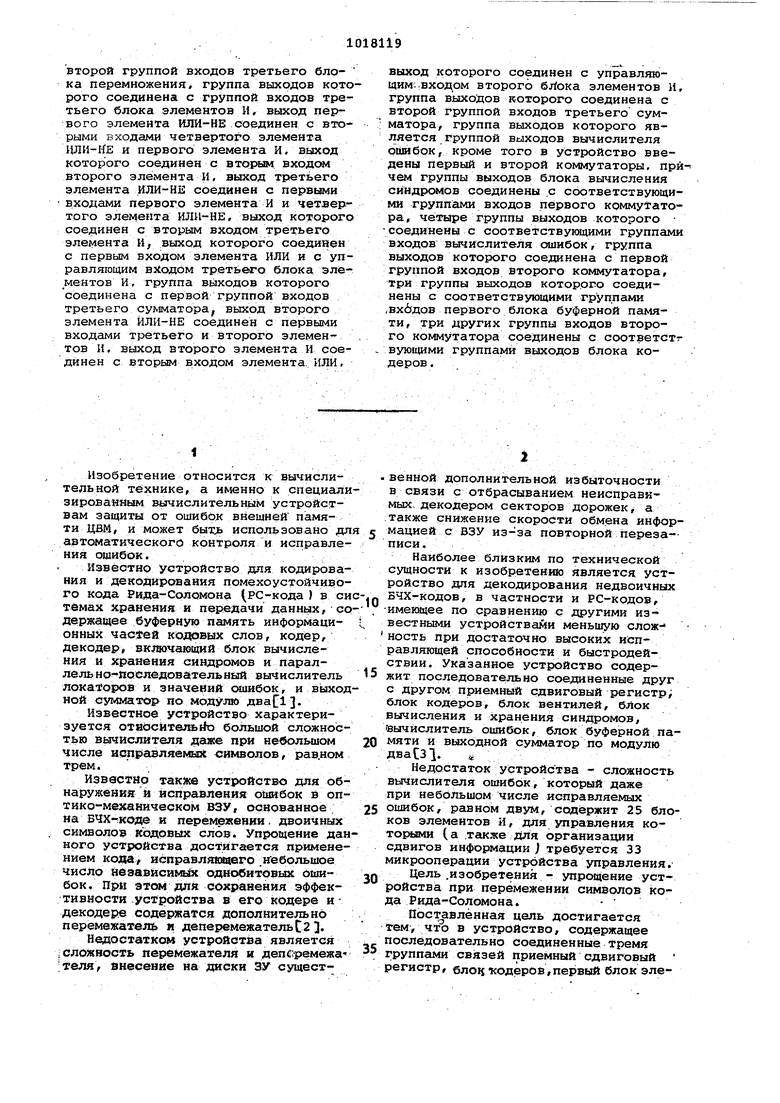

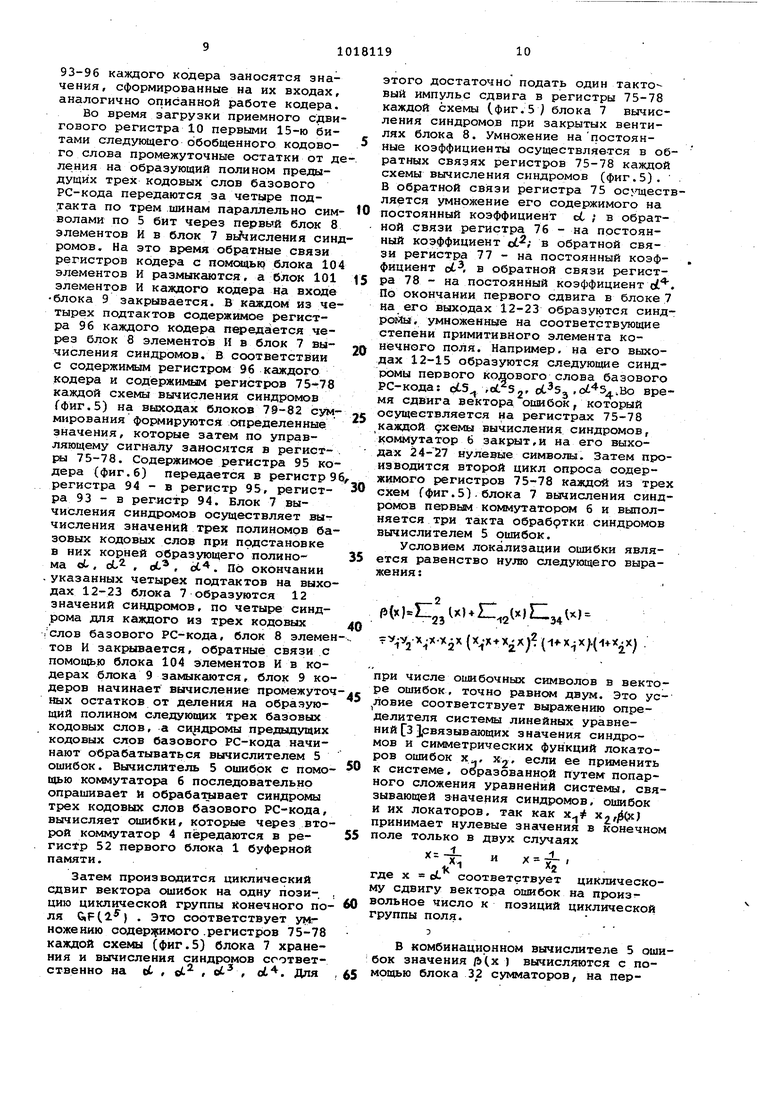

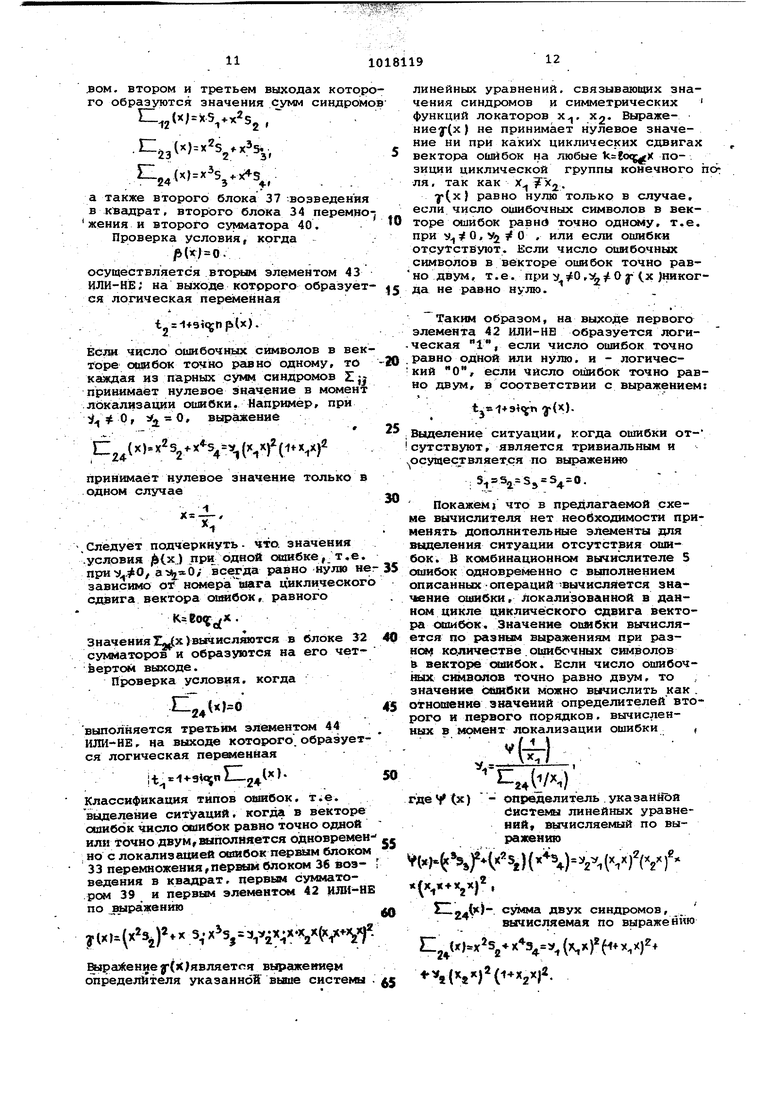

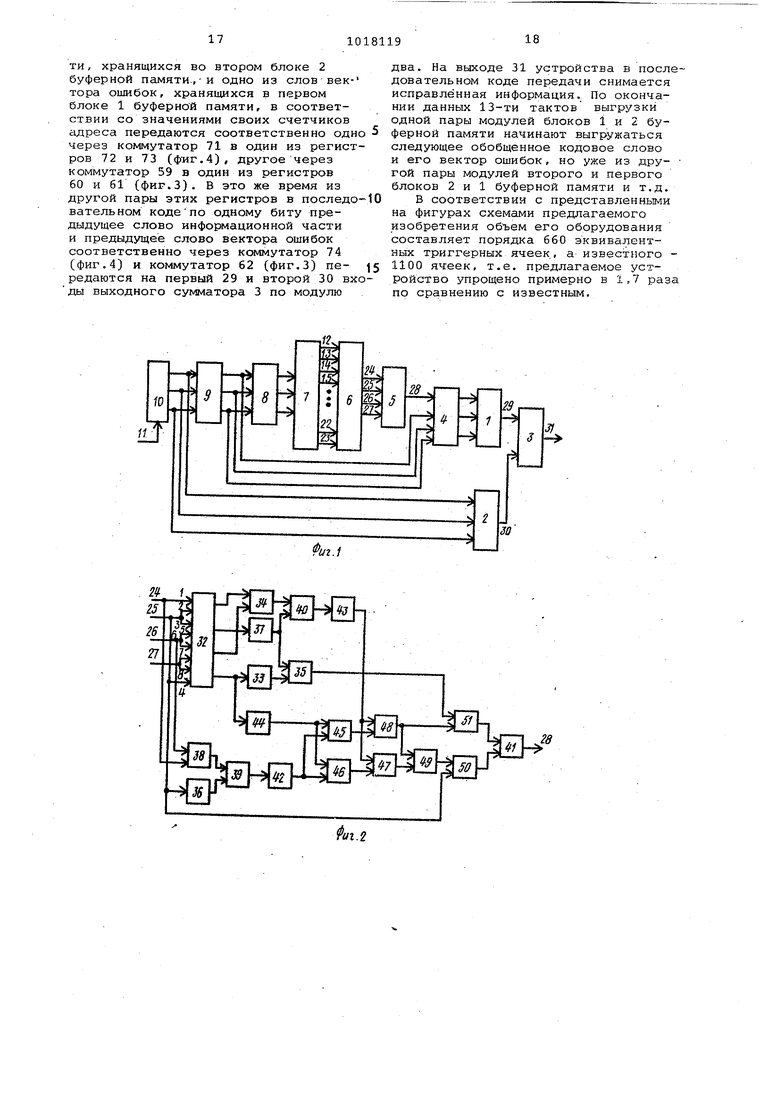

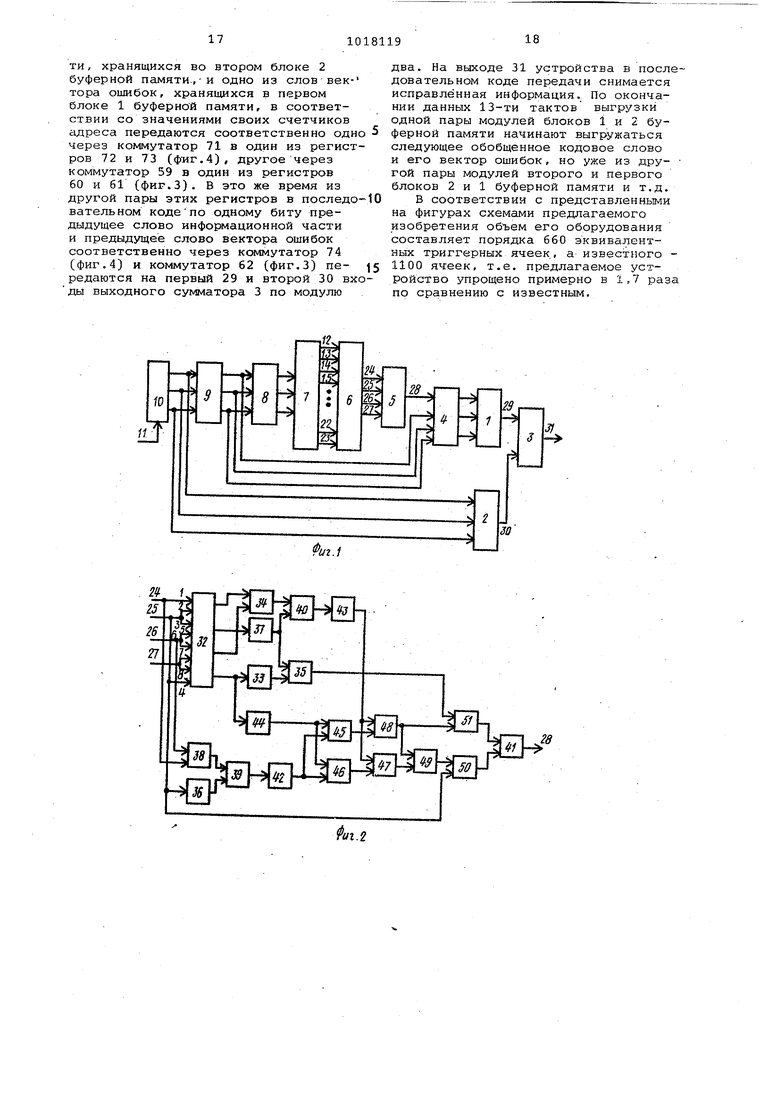

Пост.авленная цель достигается тем, что в устройство, содержащее последовательно соединенные тремя группами связей приемный сдвиговый регистр, блочтсодеров,первый блок элементов Н и блок вычисления синдромов , вычислитель ошибок, выходной сумматор по модулю два, первый и второй блоки буферной памяти, выходы которых соединены соответственно с первым и вторым входами выходного сумматора по моду-лю два, выход которого является выходом устройства, тр группы входов второго блока буферной памяти соединены с тремя группами выходов приемного сдвигового регистра, вход КОТ9РОГО является информаци онным входом устройства, вычислитель оши.бок содержит блок сумматоров, пер вый, второй и третий блоки перемножения, первый и второй блоки возведения в квадрат, блок нахождения обратного элемента, первый, второй и третий сумматоры, первый, второй, третий и четвертый элементы НЛИ-НЕ, первый,, второй и третий элементы И, элемент ИЛИ, второй и третий блоки элементов И, причем первая группа входов вычислителя ошибок соединена с первыми группами входов блока сумматоров и первого блока перемножения группа выходов которого соединена с первой группой входов первого сумматора , вторая группа входов вычислителя ошибок соединена с второй,третьей и четвертой группами входов блока сумматоров, с. группой входов первого блока возведения в квадрат и с группой входов второго блока эле ментов Иг третья группа входов вычис лителя ошибок соединена с пятой и шестой группами входов блока сумматоров и с второй группой входов первого блока перемножения, четвертая группа входов вычислителя ошибок сое динена с седьмой и восьмой группами входов блока сумматоров, группа вы;Ходов первого блока возведения в . квссцрат соединена с второй группой ; входов первого сумматора, группа выходов которого со.ёдинена с группой входов первого элемента ИЛИ-НЕ, первая и Третья rpynrtH выходов блока сумматоров соединены с соответствующими труппами входов второго блока перемножения, группа выходов которого соединена с первой группой входов второго суммматора, вторая групп выходов блока cyi taxopoB соединена с.группой входов BTojJOTo блока возведения в квадрат, группа выходов которого соединена с первой груйпой входов третьего блока перемножения и второй группой входов второго сумматора, группа выходов которого сое динена с группой входов второго элемента ИЛИ-НЕ, четвертый выход блока сумматоров соединен с группой входо третьего элемента ИЛИ-НЕ и группой входов блсйса нахождения обратного элемента, группа выходов которого со динена со второй группой входов тре тьего блока перемножения, группа вы ходов которого соединена с группой входов третьего блока элементов И, ВЫХОД первого элемента ИЛИ-НЕ соединен с вторыми входами четвертого элемента ИЛИ-НЕ и первого, элейента И, выход которого соединен с вторым входом второго элемента И, выход третьего элемента ИЛИ-НЕ соединен с первыми входами первого элемента И и четвертого элемента ИЛИ-НЕ, выход которого соединен с вторьаам входом третьего элемента И, выход когорого соединен с первым входом элемента ИЛИ и с управяякндим входом третьего блока элементов И, группа выходов которого соединена с первой группой входов третьего сумматора, вькод второго элемента ИЛИ-НЕ соединен с первыми входами третьего и второго элементов И, выход второго элемента И соединен с вторым входом элемента ИЛИ, выход которого соединен с управляющим входом второго блока элементов И, группа выходов которого соединена с второй группой входов третьего сумматора, rpS.nna выходов которого является группой выходов вычислителя ошибок. Кроме того, Б устройство введены первый и второй коммутато ял, причем группы выходов блока вычисления синдромов соединена с соответствующими группами входов первого коммутатора, четыре группы выходов которого соединены с соответствующими группами входов вычислителя ошибок, rpynnai выходов которого соединена с первой группой входов второго коммутатора, три группы выходовкоторого соединены с соответствуюпщми группами входов первого блока буферной памяти, три других группы входов второго коммутатора соедаснены с соответствующи ми группами выходов блока кодеров. На фиг.1 представлена блок-схема предложенного устройства, защиты от ошибок внешней памяти; на фиг.2 - то же, вычислителя ошибок; на фиг.3-7 примеры реализации первого .орого блоков буферной памяти, блока вычисления синдромов, блока кодеров :и приемного сдвиговогорегистра соответственно, Устройство содержит первый и второй блоки 1 и 2 буферной памяти, выходной сумматор 3 по модулю два, второй коммутатор 4,вычислитель 5 ошибок, первый коммутатор 6, блок 7 вычисления.синдромов, первый блок 8 элементов jjt, блок 9 кодеров и приемный сдвиговый регистр 10, информационн1 1й вход 11 сдвигового регистра, выходы 12-23 блока вычисления Синдромов, выходы 24-27 коммутатора, выход 28 вычислителя ошибок, выходы 29, 30 блоков буферной памяти, выход 31 сумматора по модулю два. Вычислитель 5 ошибок (фиг.2) содержит блок 32 сумматоров, первый.

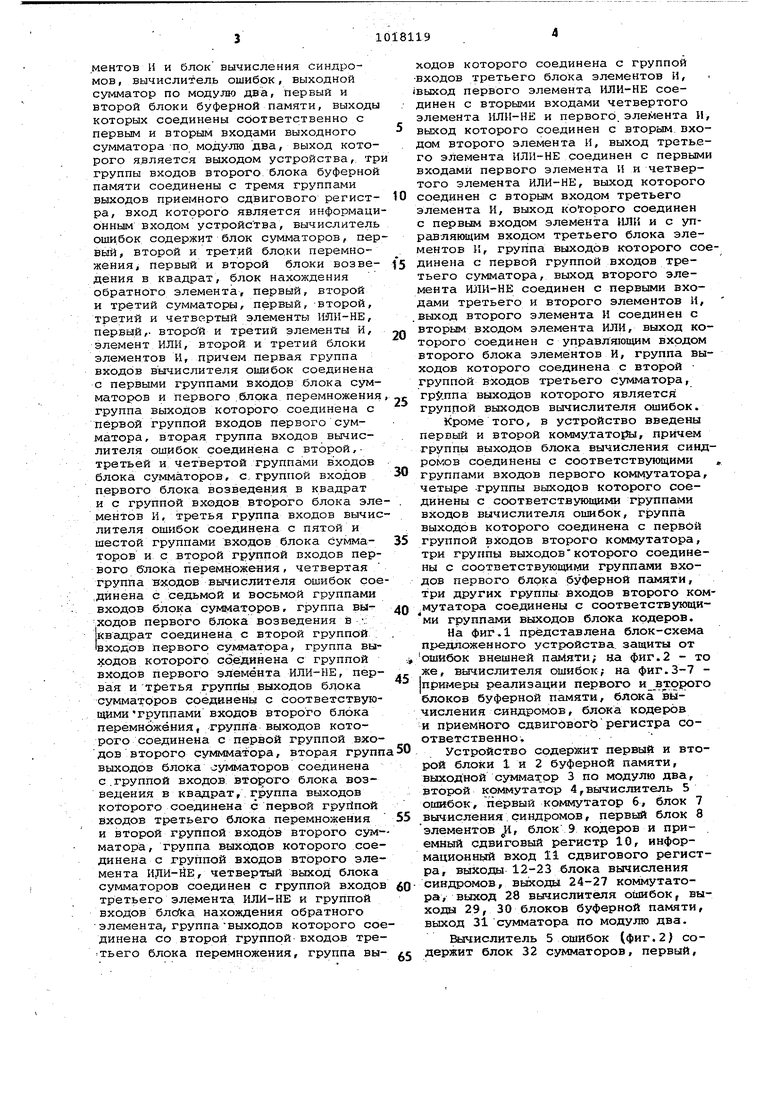

второй и третий блоки 33, 34 и 35 перемножений, первый и второй блоки 36 и 37 возведения в квадрат, блок 38 нахождения обратного элемента, первый и второй и третий сумматоры 39, 40 и 41, первый, второй, третий и четвертый элементы 42-43 ИЛИ-НЕ, первый, второй и третий элементы 46, 47 и 48 И,элемент 49 ИЛИ, первый и второй блоки 50 и 51 элементов И.

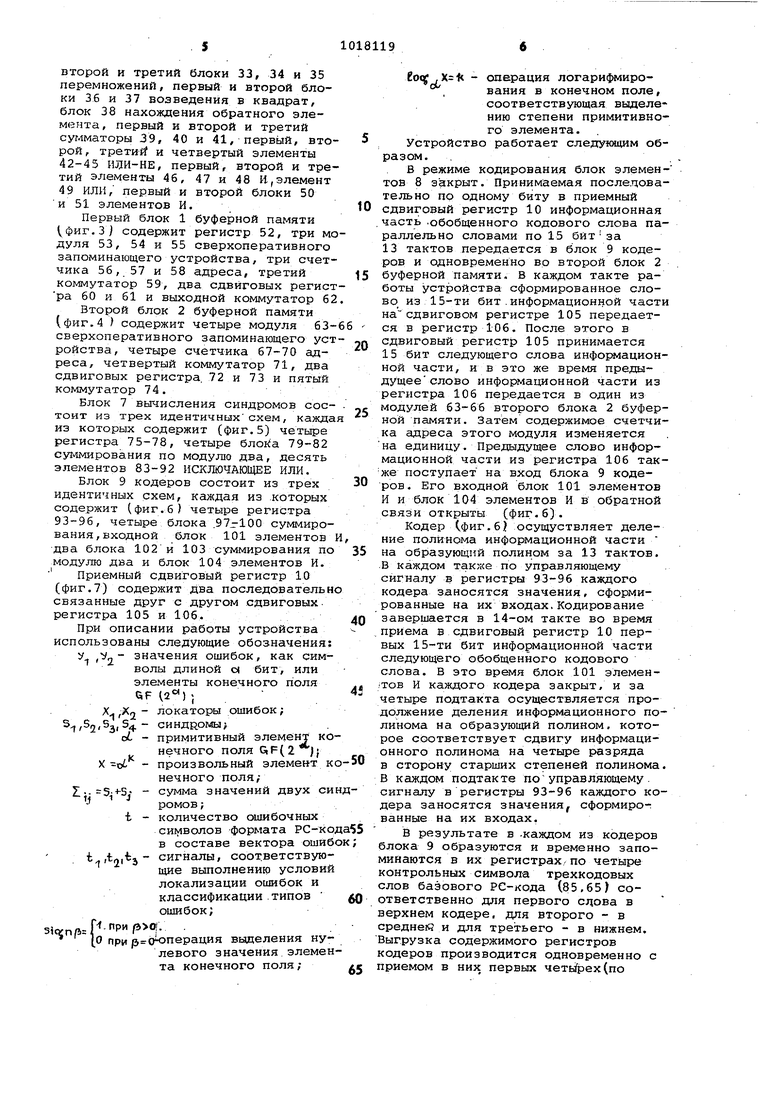

Первый блок 1 буферной памяти фиг.З) содержит регистр 52, три модуля 53, 54 и 55 сверхоперативного запоминающего устройства, три счетчика 56, 57 и 58 адреса, третий коммутатор 59, два сдвиговых регистра 60 и 61 и выходной коммутатор 62.

Второй блок 2 буферной памяти (фиг.4 ) содержит четыре модуля 63-6сверхоперативного запоминающего устройства, четыре счетчика 67-70 адраса, четвертый коммутатор 71, два сдвиговых регистра, 72 и 73 и пятый коммутатор 74.

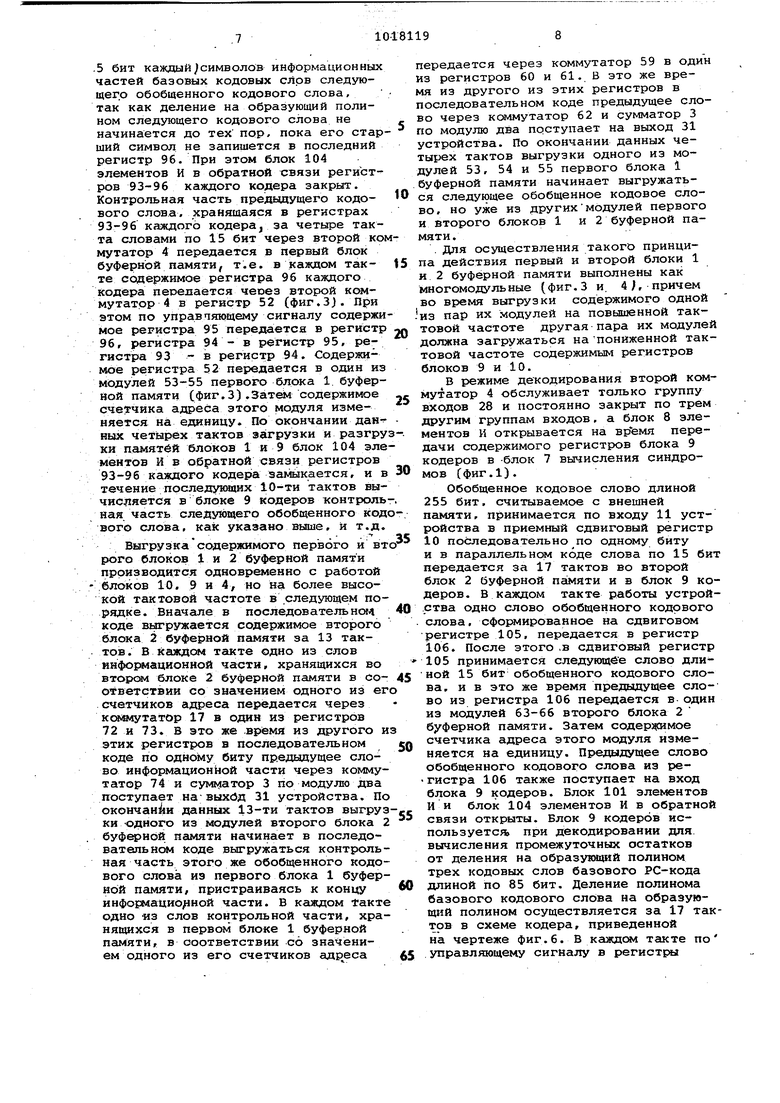

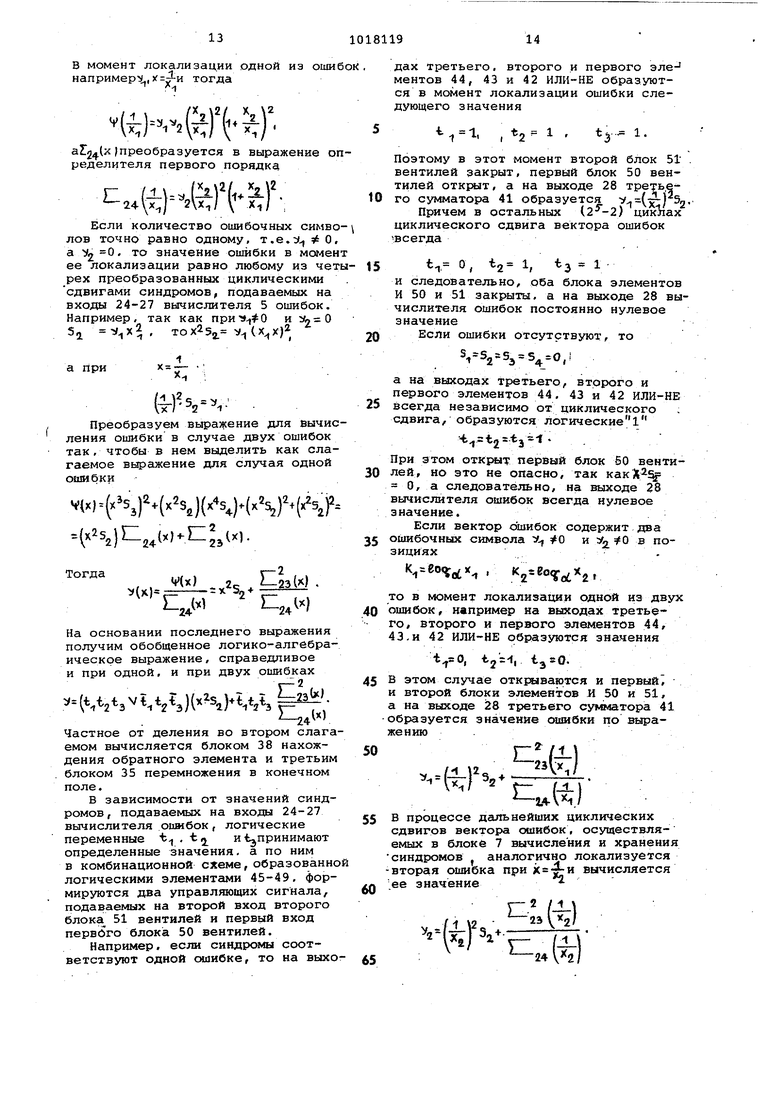

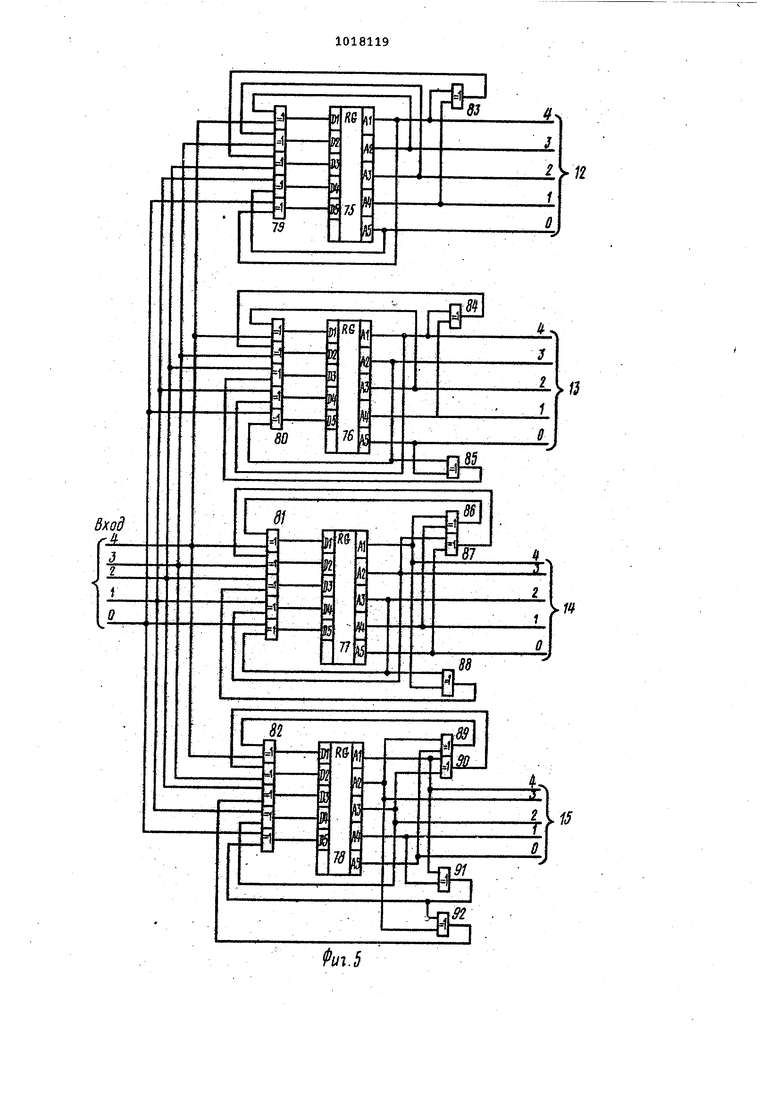

Блок 7 вычисления синдромов соетоит из трех идентичныхсхем, каждая из которых содержит (фиг.5) четыре регистра 75-78, четыре блока 79-82 суммирования по модулю два, десять элементов 83-92 ИСКЛЮЧАЮЩЕЕ ИЛИ.

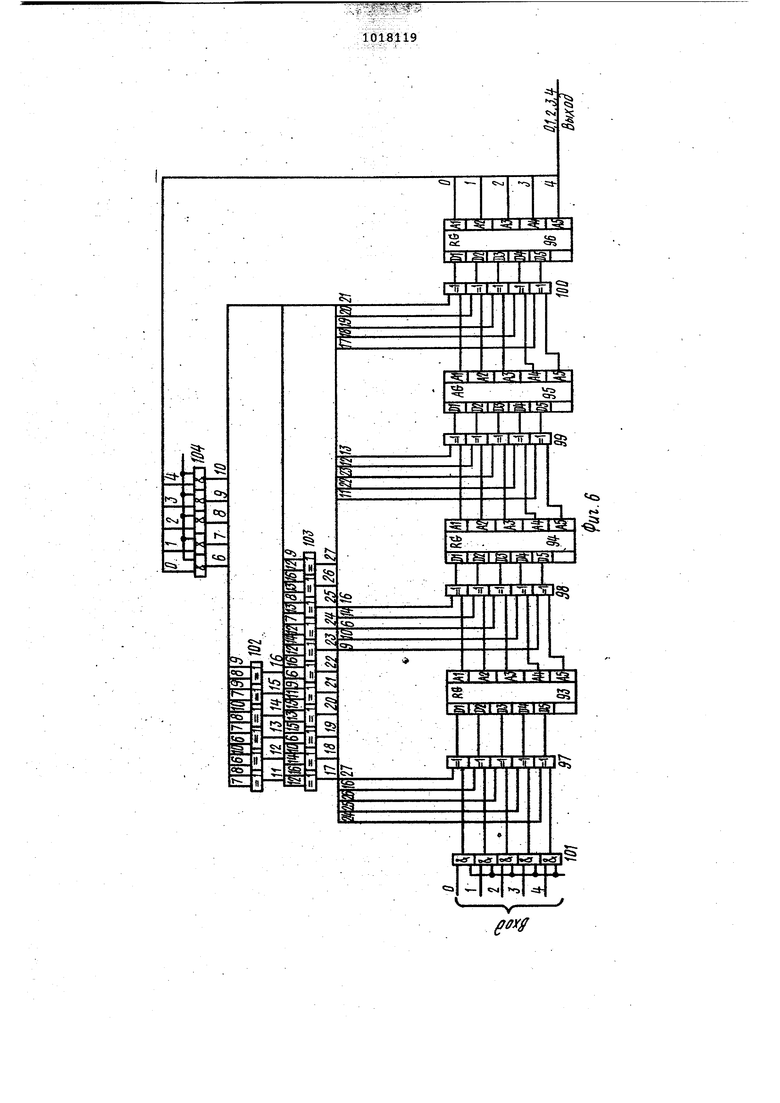

Блок 9 кодеров состоит из трек идентичных схем, каждая из .которых содержит (фиг.6) четыре регистра 93-96, четыре блока .97-100 суммирования, входной блок 101 элементов И два блока 102 и 103 суммирования по модулю два и блок 104 элементов И.

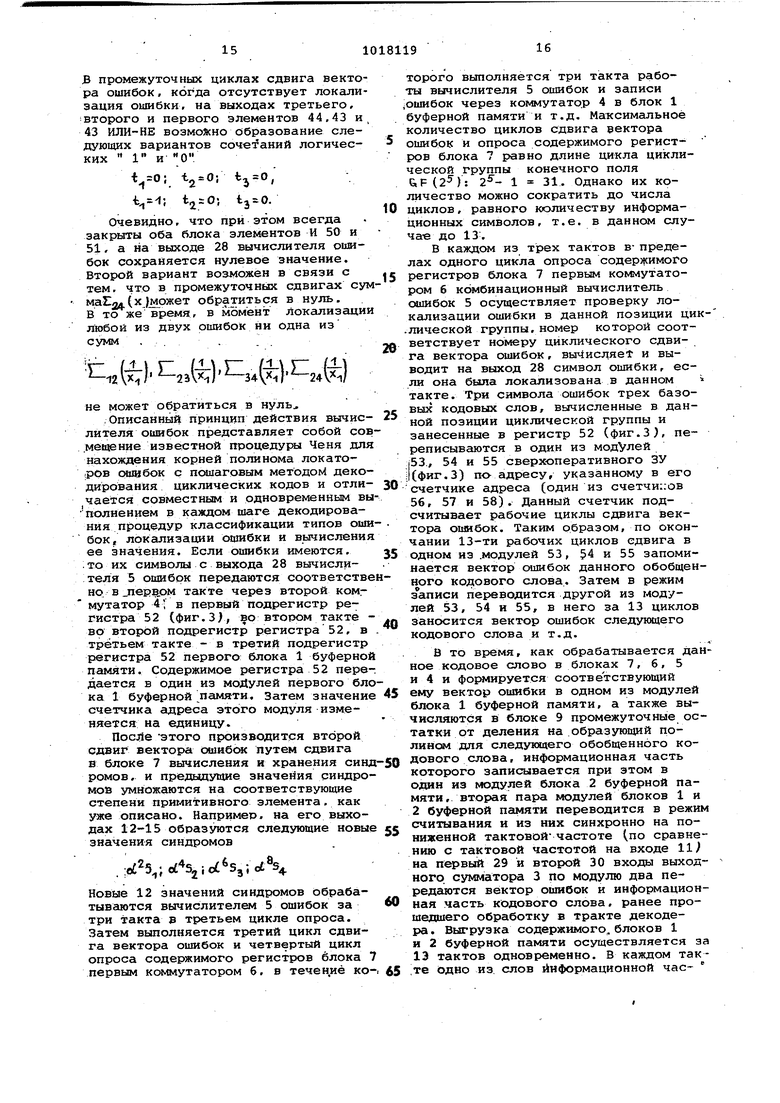

Приемный сдвиговый регистр 10 (фиг.7) содержит два последовательно связанные друг с другом сдвиговыхрегистра 105 и 106.

При описании работы устройства использованы следующие обозначения: у ,У„- значения ошибок, как символы длиной d бит, или элементы конечного поля GF (2«) ;

Х локаторы ошибок; S /Sj/S, синдромы;

cL - примитивный элемент конечного поля CiF(2 )( X -oi - произвольный элемент ко

нечного поля;

2;.. .- - сумма значений двух син ромов;

t - количество ошибочных

сиг)1волов формата РС-код в составе вектора ошибо t trtitj - сигналы, соответствующие выполнению условий локализации ошибок и классификации.типов ошибок;

з5с5пр Р

О при б СГОГ1ерация выделения нулевого значения элемента конечного поля; j

. ( - операция логарифмиро, вания в конечном поле, соответствующая выделению степени примитивного элемента.

Устройство работает следующим образом.

В режиме кодирования блок элементов 8 закрыт. Принимаемая последовательно по одному биту в приемный сдвиговый регистр 10 информационная часть .обобщенного кодового слова параллельно словами по 15 битза 13 тактов передается в блок 9 кодеров и одновременно во второй блок 2 буферной памяти. В каждом такте работы устройства сформированное слово из 15-ти бит.информационной части на сдвиговом регистре 105 передается в регистр 106. После этого в сдвиговый регистр 105 принимается 15 бит следующего слова информационной части, и в это же время предыдущее слово информационной части из регистра 106 передается в один из модулей 63-66 второго блока 2 буферной памяти. Затем содержимое счетчика адреса этого модуля изменяется на единицу. Предыдущее слово информационной части из регистра 106 также поступает на вход блока 9 кодеров. Его входной блок 101 элементов И и блок 104 элементов И в обратной связи открыты (фиг.6).

КодерЛфиг.б осущуствляет деление полинома информационной части на образующий полином за 13 тактов. .В каждом также по управляющему сигналу в регистры 93-96 каждого кодера заносятся значения« сформированные на их входах.Кодирование завершается в 14-ом такте во время .приема в сдвиговый регистр 10 первых 15-ти бит информационной части следующего обобщенного кодового слова. В это время блок 101 элемен/тов И каждого кодера закрыт, и за четыре подтакта осуществляется продолжение деления информационного полинома на образующий полином, которое соответствует сдвигу информационного полинома на четыре разряда в сторону старших степеней полинома В каждом подтакте поуправляющему. сигналу в регистры 93-96 каждого кодера заносятся значения, сформирог ванные на их входах.

В результате в .каждом из кодеров блока 9 образуются и временно запоминаются в их регистрах/по четыре контрольных символа трехкодовых слов базового PC-кода (85,65) соответственно для первого сдова в верхнем кодере, для второго - в средней и для третьего - в нижнем. Выгрузка содержимого регистров кодеров производится одновременно с приемом в них первых 4eTb3fpex(no

.5 бит каждый символов информационных частей базовых кодовых слов следующего обобщенного кодового слова, так как деление на образующий полином следующего кодового слова не начинается до тех пор, пока его старший символ не запишется в последний регистр 96. При этом блок 104 элементов И в обратной связи регистров 93-96 каждого кодера закрыт. Контрольная часть предьадущего кодового слова, хранящаяся в регистрах 93-96 каждого кодера за четыре такта словами по 15 бит через второй коммутатор 4 передается в первый блок буферной памяти, т.е. в каждом такте содержимое регистра 96 каждого кодера перелается чеоез второй коммутатор 4 в регистр 52 (фиг.3}. При этом по управпяк)1цему сигналу содержимое регистра 95 передается в регистр 96, регистра 94 - в регистр 95, регистра 93 - в регистр 94. Содержимое регистра 52 передается в один из модулей 53-55 первого блока 1. буферной памяти (фиг.3).Затем содержимое счетчика адреса этого модуля изменяется на единицу. По окончании данных четырех тактов загрузки и разгру ки памятей блоков 1 и 9 блок 104 элементов Ив обратной связи регистров 93-96 каждого кодера замыкается, и в течение последующих 10-ти тактов вычисляется в блоке 9 кодеров контроль ная часть следующего обобщенного кодвого слова, как указано выше, и т.д.

Выгрузкасодержимого первого и вт рого блоков 1 и 2 буферной памяти производится одновременно с работой блоков 10, 9 и 4, но на более высокой тактовой частоте в следующем порядке. Вначале в последователь нся4 коде вьагружается содержимое второго блока 2 буферной памяти за 13 тактов. В каждом такте одно из слов инфОЕЯлационной части, хранящихся во втором блоке 2 буферной памяти в соответствии со значением одного из ег счетчиков адреса передается через коймутатор 17 в один из регистров 72 и 73. В это же время из другого и этих регистров в последовательном коде по одному биту предыдущее слово информационной части через коммутатор 74 и cyMNiaTop 3 по модулю два поступает на; ВЫХС5Д 31 устройства. По окончании данных 13-ти тактов выгруз ки -одного из модулей второго блока 2 . памяти начинает в последовательном коде выгружаться контрольная часть этого же обобщенного кодового слова из первого блока 1 буферной памяти, пристраиваясь к концу информационной части. В каждом Такте одно -из слов контрольной части, хранящихся в первом блоке 1 буферной памяти, в соответствии со значением одного из его счетчиков адреса

передается через коммутатор 59 в один из регистров 60 и 61. В это же время из другого из этих регистров в последовательном коде предыдущее слово через коммутатор 62 и сумматор 3 по модулю дйа поступает на выход 31 устройства. По окончании данных четырех тактов выгрузки одного из модулей 53, 54 и 55 первого блока 1 .буферной памяти начинает выгружаться следующее обобщенное кодовое слово, но уже из другихмодулей первого и второго блоков 1 и 2 буферной памяти.

. Для осуществления такого принципа действия первый и второй блоки 1 и 2 буферной памяти выполнены как многомодульные (фиг.З и 4Ь причем во время выгрузки содержимого одной -из пар их модулей на повышенной тактовой частоте другая пара их модулей должна загружаться на пониженной тактовой частоте содержимым регистров блоков 9 и 10.

В режиме декодирования второй коммутатор 4 обслуживает только группу входов 28 и постоянно закрыт по трем другим группам входов, а блок 8 элементов И открывается на передачи содержимого регистров блока 9 кодеров в -блок 7 вычисления синдромов СФИГ.1).

Обобщенное кодовое слово длиной 255 бит, считываемое с внешней памяти, принимается по входу 11 устройства в приемный сдвиговый регистр 10 последовательно по одному биту и в параллельном коде слова по 15 би передается за 17 тактов во второй блок 2 буферной памяти и в блок 9 кодеров. В каждом такте работы устройства одно слово обобщенного кодового

. слова, сфо ллированное на сдвиговом регистре 105, передается в регистр i06. После этого ,в сдвиговый регистр 105 принимается следующбе слово длиной 15 бит обобщенного кодового слова, ив это же время предыдущее слово из регистра 106 передается в один из модулей 63-66 второго блока 2 буферной памяти. Затем содержимое счетчика адреса этого модуля изменяется на единицу. Предыдущее слово обобщенного кодового слова из регистра 106 также поступает на вход блока 9 кодеров. Блок 101 элементов ИИ блок 104 элементов И в обратной связи открыты. Блок 9 кодеров используется при декодировании для вычисления промежуточных остатков от деления на образующий полином трех кодовых слов базового PC-кода длиной по 85 бит. Деление полинома базового кодового слова на образующий полином осуществляется за 17 тактов в схеме кодера, приведенной на чертеже фиг.6. В кг1ждс 1 такте по управляющему сигналу в регистры 93-96 каждого кодера заносятся значения, сформированные на их входах, аналогично описанной работе кодера. Во время загрузки приемного сдвигового регистра 10 первыми 15-ю битами следующего обобщенного кодового слова промежуточные остатки от де ления на образующий полином предыдущих трех кодовых слов базового PC-кода передаются за четыре под,такта по трем шинам параллельно символами по 5 бит через первый блок 8 элементов И в блок 7 вь/числения синд ромов. На это время обратные связи регистров кодера с помощью блока 10 элементов И размыкаются, а блок 101 элементов И каждого кодера на входа блока 9 закрывается. В каждом из четырех подтактов содержимое регистра 96 каждого кодера пед едается через блок 8 элементов И в блок 7 вычисления синдромов, В соответствии с содержимым регистром 96 каждого кодера и содержимым регистров 75-78 каждой схемы вычисления синдромов (фиг. 5) на выходах блоков 79-82 суммирования формируются определенные значения, которые затем по управляющему сигналу заносятся в регистры 75-78. Содержимое регистра 95 кодера (фиг. 6) передается в регистр 9 регистра 94 - в регистр 95, регистра 93 - в регистр 94. Блок 7 вычисления синдромов осуществляет вычисления значений трех полиномов базовых кодовых слов при подстановке в них корней образующего полинома ot, oL , of , оС. По окончании - указанных четырех подтактов на выходах 12-23 блока 7 образуются 12 значений синдромов, по четыре синдрома для каждого из трех кодовых /слов базового PC-кода, блок 8 элемен тов И закЕ 1вается, обратные связи с помощью блока 104 элементов И в кодерах блока 9 замыкаются, блок 9 кодеров начинает вычисление промежуточ ных остатков от деления на образующий полином следующих трех базовых кодовых слов, а си|1дромы предыдущих кодовых слов базового PC-кода начинают обрабатываться вычислителем 5 ошибок. Вычислитель 5 ошибок с помо щью коммутатора 6 последовательно опрашивает и обрабатывает синдромы трех кодовых слов базового PC-кода, вычисляет ошибки, которые через вто рой коммутатор 4 передаются в регистр 52 первого блока 1 буферной памяти. Затем производится циклический сдвиг вектора сяиибок на одну пози-, цию циклической группы Конечного по ля GiF(2.) . Это соответствует умг ножению содвр} имого .регистров 75-78 каждой схемы (фиг.5) блока 7 хранения и вычисления синдромов соответet , ot , об-. Для ственно на I этого достаточно подать один такто-вый импульс сдвига в регистры 75-78 каждой схемы (фиг.5 блока 7 вычисления синдромов при закрытых вентилях блока 8. Умножение напостоянные коэффициенты осуществляется в обратных связях регистров 75-78 каждой схемы вычисления синдромов (фиг.5). . В обратной связи регистра 75 ос лцествляется умножение его содержимого на постоянный коэффициент oi ; в обратной связи регистра 76 - на постоянный коэффициент в обратной связи регистра 77 - на постоянный коэффициент ot, в обратной связи регистра 78 - на постоянный коэффициент ci. По окончании первого сдвига в блоке 7 на его выходах 12-23 образуются синдрОЯы, умноженные на соответствующие степени примитивного элемента конечного поля. Например, на его выходах 12-15 образуются следующие синдромы первого кодового слова базового PC-кода: «stS . ..Bo время сдвига вектора ошибок, который осуществляется на регистрах 75-78 каждой вычисления синдромов, коммутатор 6 закрыт,и на его выходах нулевые символы. Затем производится второй цикл опроса содержимого регистров 75-78 каждой из трех схем fфиг.5).блока 7 вычисления синдромов первьм коммутатором 6 и выполняется три такта обрабртки синдромов вычислителем 5 ошибок. Условием локализации ошибки является равенство нулю следующего выражения : f(,, х.х.х,х () (.(1+х,х при числе ошибочных символов в векторе ошибок, точно рависям двум. Это ус ловие соответствует выражению определителя системы линейных уравнений р .связывающих значения синдромов и симметрических функций локаторов ошибок X , если ее применить к системе, образованной путем попарного сложения уравнений систег-ол, связывающей значения синдромов, ошибок и их локаторов, так как ) принимает нулевые значения в конечном поле только в двух случаях 4 где X cL соответствует циклическому сдвигу вектора ошибок на произ вольное число к позиций циклической группы поля. в комбинационном вычислителе 5 ошиi бок значения /S(x J вычисляются с помощью блока 32 сумматоров, на , втором и третьем выходах котор го образуются значения сумм синдром n,,(.x2s2 , .,, 24( Ч-, . . а также второго блока 37 возведения в квадрат, второго блока 34 перемно женин и второго сумматора 40. Проверка условия, когда р(х) о. осуществляется вторым элементом 43 ИЛИ-НЁ; на выходе которого образует ся логическая пер«яейная . t rl+SiCgtlpix). EcJF9€ ЧИСЛО ошибочных СИМВОЛОВ в век торе опибок точно равно , то каждая из парных сумм синдромов Zj| принимает нулевое значение в момент л6кал11защ1и ошибки. 11апример, при , У, 0, выражение . - . П2(С),(Ч)() принимает нулевое значение только в одном случав Следует подчеркнуть - что. значения .условия MX.) при одной ошибке, т.е. прич,.#О а О,-всегда равно нулю не зависимо о номера inara циклическог сдвига вектора ошибок, равного . Значения )вычисляются в блоке 32 сумматоров и образуются на его четвертом выходе. Проверка условия. когда выполняется третьим элементом 44 ИЛИ-НЕ, на выходе которого, образуется логическая пераленная Jt 1+9 q}nEl24 Классификация типов ошибок, т.е. выделение ситуаций. когда в векторе ошибок число сшибок равно точно оддаой или точно двум, исполняется одновремен но с локализацией ошибок периам блоком 33 перемножения,периамблоком 36 возведения в квадрат, первым сумматорсм 39 и первым элементом 42 ИШ1-Н по илражению у1х) 3,.X% Vi4V( KatpaMieHHe jf(x являетг я выражением определителя указанной выше системы линейных уравнений, связываюсцих значения синдромов и симметрических функций локаторов х,. Х2. Выражениеу(х) не принимает нулевое значение ни при каких циклических сдвигах вектора ошибок на любые по-. зиции циклической группы конечного пег ля, так как х х,. у(х) равно нулю только в случае, если число оцшбочных символов в векторе ошибок равнй точно одному, т.е. при v О, У2 э О , или если ошибки отсутствуют. Если число оимбочных символов в векторе ошибок точно равно двум, т. е. при v #0 ,: О )никогда не равно нулю. Таким образом, на выходе первого элемента 42 или-НЕ образуется логическая 1, если число ошибок точно равно ОДНОЙ или нулю, и - логический О, если число ошибок точно равно двум, в соответствии с выражением: (x). Выделение ситуации, когда ошибки отсутствуют, является тривиальным и осуществляет.сй по выражению i Пoкaжeмt что в предлагаемой схеме вычислителя нет необходимости применять дополнительные элементы для выделения ситуации отсутствия ошибок. В к 4бинационном вычислителе 5 ошибок одновременно с выполнением описанных-операций -вычисляется значение ошибки, локализованной в данном цикле циклического сдвига вектора ошибок. Значение ошибки вычисляется по разным выражениям при разном количестве ошибочных символов в векторе (Яйибок. Если число ошибочных символов точно равно двум, то значение ошибки можно вычислить как. отношение значений определителей второго и первого порядков, вычисленных в момент локализации ошибки , {М V - 11, .«(VM где У(х) - определитель.указанйЪй Системы линейных уравнений, вычисляемый по выражению (){A)(vf(vf (V d,(xj-. сумма двух синдромов, вычисляемая по выражению )) M8))В момент локализации одной из ошибок например.,)и тогда -1

4i)v4)).

alj.l преобразуется в выражение определителя первого порядка

С W(l(

MX-,/ V Xl/ :

Вели количе.ство ошибочных символов точно равно одному, т.е.у 0. а 2 0 то значение ошибки в момент ее локализации равно любому из четырех преобразованных циклическими сдвигами синдромов, подаваемых на входы 24-27 вычислителя 5 ошибок. Например. так как npH-s-t O и

V х2

TOX25,i

(Х,Х), 1 -1

а при

Ш

52

Преобразуем выражение для вычисления ошибки в случае двух ошибок так, чтобы в нем выделить как слагаемое выражение для случая одной ошибки

V(x)(x%)4(x2sJ{x).(K2s,f.( )

П2э(х) .

X.h.-% ) Ц(

На основании последнего выражения получим обобщенное логико-алгебраическое выражение, справедливое и при одной, и при двух ошибках

)-2

Р

i-2

Частное от деления во втором слагаемом вычисляется блоком 38 нахождения обратного элемента и третьим блоком 35 перемножения в конечном поле.

В зависимости от значений синдромов, подаваемых на входы 24-27 вычислителя опжбок, логические переменные 1 иЪ принимают определенные значения. а по ним в комбинационной схеме, образованн логическими элементами 45-49, формируются два управляющих сигнала, подаваемых на второй вход второго блока 51 вентилей и первый вход первого блока 50 вентилей.

Например, если синдромы соответствуют одной ошибке, то на выходах Третьего. второго и первого элементов 44, 43 и 42 ИЛИ-НЕ образуются в мсмент локализации ошибки следующего значения

, tj. 1

.

ь-1Поэтому в этот момент второй блок 51 вентилей закрыт, первый блок 50 вентилей открыт, а на выходе 28 третье го сумматора 41 образуется v(

Причем в остальных () циклах циклического сдвига вектора ошибок всегда

Ц О, t2 1, t3 1

и следовательно, оба блока элементов И 50 и 51 закрыты, а на выходе 28 вычислителя ошибок постоянно нулевое значение

Если ошибки отсутствуют, то

а на выходах третьего, второго и первого элементов 44. 43 и 42 ИЛИ-НЕ всегда независимо от циклического сдвига, образуются логические

t t2 . .

При этом открыт первый блок 50 вентилей, но это не опасно, так О, а следовательно, на выходе 28 вычислителя ошибок всегда нулевое значение.

Если вектор ошибок содержит два ошибочных символа , #0 и У, 0 в позициях

«4o6S «2 °Tot 2.

то в момент локализации одной из двух ошибок, например на выходах третьего, второго и первого элементов 44, 43.и 42 ИЛИ-НЕ образуются значения

, tjz-f, .

В этом случае открываются и первый и второй блоки элементов И 50 и 51, а на выходе 28 третьего сумматора 41 образуется значение ошибки по выражению

Ш

п

n(J

(

32

tl {-fl

В процессе дальнейших циклических сдвигов вектора ошибок, осуществляемых в блоке 7 вычисления и хранени синдромов аналогично локализуется -вторая ошибка при х и вычисляется

вторая

ее значение

(У

п

23

У2-1- 1 В промежуточных циклах сдвига вектора ошибок, когда отсутствует локализация ошибки, на выходах третьего, второго и первого элементов 44,43 и 43 ИЛИ-ВЕ воэмоясно образование следующих вариантов сочетаний логических 1 и О tjxO; Очевидно, что при этом всегда закрыты оба блока элементов И 50 и 51, а на выходе 28 вычислителя очмбок сохраняется нулевое значение. Второй вариант возможен в связи с тем, что в промежуточных сдвигах су маЕдд.(X )может обратиться в нуль. В то же время, в момент Локализаци любой из двух ошибок ни одна из сумм ... 12(х) ()) не может обратиться в нуль .Описанный принцип действия вычислителя ошибок представляет собой сов мещение известной процедуры Ченя для нахождения корней полинома локаторов ошибок с пошаговым методом декодирования циклических кодов и отличается совместным и одновременным вы полнением в каждом шаге декодирования процедур классификации типов оши бок, локализации сявибки и вычисления ее значения. Если ошибки имеются. :то их символы с выхода 28 вычислителя 5 ошибок передаются соответстве но в перв.ом такте через второй комг мутатор 4- в первый подрегистр регистра 52 (фиг.З), во втором такте во второй подрегистр регистра 52, в третьем такте - в третий подрегистр регистра 52 первого блока 1 буферной памяти. Содержимое регистра 52 передается в один из модулей первого бло ка 1 буферной памяти. Затем значение счетчика адреса этого модуля -изменяется на единицу. После ЭТОГО производится второй сдвиг вектора ошибсж путем сдвига в блоке 7 вычисления и хранения синд ромов, и предыдущие значения синдромов умножаются на соответствующие степени примитивного элемента, как уже описано. Например, на его выходах 12-15 образуются следующие новые значения синдромов ,,,;d Новые 12 значений синдромов обрабатываются вычислителем 5 ошибок за три такта в третьем цикле опроса. Затем выполняется третий цикл сдвига вектора ошибок и четвертый цикл опроса содержимого регистров блока 7 первым коммутатором б, в течение KOторого выполняется три такта работы вычислителя 5 ошибок и записи (Ошибок через коммутатор 4 в блок 1 буферной памяти и т.д. Максимальное количество циклов сдвига вектора ошибок и опроса содержимого регистров блока 7 равно длине цикла циклической группы конечного поля G,F(2): 1 31. Однако их количество можно сократить до числа циклов, равного количеству информационных символов, т.е. в данном случае до 13. В каждом из трех тактов в- пределах одного цикла опроса содержимого регистров блока 7 первым коммутатором 6 комбинационный вычислитель сшибок 5 осуществляет проверку локализации ошибки в данной позиции циклической группы, номер которой соответствует номеру циклического сдвига вектора ошибок, вычисляет и выводит на выход 28 символ ошибки, если она была локализована в данном такте. Три символа ошибок трех базовых кодовых слов, вычисленные в данной позиции циклической группы и занесенные в регистр 52 (фиг.З), переписываются в один из модулей 53, 54 и 55 сверхоперативного ЗУ (фиг.З) по адресу, указанному в его счетчике адреса (один из счетчи::ов 56, 57 и 58). Данный счетчик подсчитывает рабочие циклы сдвига 1вектора ошибок. Таким о.бразом, по окончании 13-ти рабочих циклов сдвига в одном из .модулей 53, 54 и 55 запоминается вектор ошибок данного обобщенного кодового слова. Затем в режим записи переводится другой из модулей 53, 54 и 55, в него за 13 циклов заносится вектор ошибок следующего кодового слова и т.д. В то время, как обрабатывается Данное кодовое слово в блоках 7, 6, 5 и 4 и фоЕ юруется соответствующий ему вектор ошибки в одном из модулей блока 1 буферной памяти, а также вычисляются в блоке 9 промежуточные остатки от деления на образуюгдай полкном для следующего обобщенного кодового слова, информационная часть которого записывается при этом в один из модулей блока 2 буферной памяти,, вторая пара модулей блоков 1 и 2 буферной памяти переводится в режим считывания и из них синхронно на пониженной тактовой частоте (по сравнению с тактовой частотой на входе 11 на педвый 29 и второй 30 входы выходного сумматора 3 по модулю два передаются вектор ошибок и информационная часть кодового слова, ранее прошедшего обработку в тракте декодера. Выгрузка содержимого, блоков 1 и 2 буферной памяти осуществляется за 13 тактов одновременно. В каждом одно из слов информационной час-

ти, хранящихся во втором блоке 2 буферной памяти.,-и одно из слов вектора ошибок, хранящихся в первом блоке 1 буферной памяти, в соответствии со значениями своих счетчиков адреса передаются соответственно одно через коммутатор 71 в один из регистров 72 и 73 (фиг.4), другое через коммутатор 59 в один из регистров 60 и 61 (фир.З). В это же время из другой пары этих регистров в последовательном кодепо одному биту предыдущее слово информационной части и предыдущее слово вектора ошибок соответственно через коммутатор 74 (фиг.4) и коммутатор 62 (фиг.З) передаются на первый 29 и второй 30 входы выходного сумматора 3 по модулю

два. На выходе 31 устройства в последовательном коде передачи снимается исправленная информация.. По окончании данных 13-ти тактов выгрузки одной пары модулей блоков 1 и 2 буферной памяти начинают выгружаться следующее обобщенное кодовое слово и его вектор ошибок, но уже из другой пары модулей второго и первого блоков 2 и 1 буферной памяти и т.д. В соответствии с представленными на фигурах схемами предлагаемого изобретения объем его оборудования составляет порядка 660 эквива.лентных триггерных ячеек., а известного 1100 ячеек, т.е. предлагаемое устройство упрощено примерно в 1,7 раза по сравнению с известным.

1018119

.r.T/T

I JN I Ш.

w

Авторы

Даты

1983-05-15—Публикация

1981-06-10—Подача