Изобретение относится к импульсной технике и может быть использовано в FiporpaMмных системах автоматического управления.

Известен генератор импульсов, содер кащий интегрирующие усилители, амплитудные дискриминаторы, Й5-триггеры и переключатели .

Недостатком данного генератора является нестабильность кр5(тизны фронтов выходного напряжения.

Более совершен}1ым является устройство формирозания ступенчато-трапецеидального напряжения, содержащее дешифратор, устройство временных задержек, триггер реверса, счетчик, импульсов, преобразователь код-напряжеиие, элемент совпадения, генераторы пикообразных напряжений 2.

Недостаток устройства - невысокая стабильность фронтов выходного ступенчатотрапецеидального напряжения.

Цель предлагаемого изобретения - повышение стабильности крутизны фронтов импульсов выходного напряжения.

Для этого в устройство формирования ступенчато-трапецеидального напряжения, содержащее элементы задержки, дешифратор, счетчики импульсов и триггер реверса.

введены фазовый демодулятор, блок амплитудно-импульсных компараторов, триггер интервалов, делители частоты и генератор стабильной частоты, прямой вход которого через первый делитель частоты соединен с

первым входом дешифратора, через второй делитель частоты - со вторым входом дешифратора, инверсный выход - непосредственно с первыми входами счетчиков, импульсов, ко вторым и третьим входам которых подключены выходы дешифратора, а выходы счетчиков импульсов через фазовый демодулятор подключены ко входу блока амплитудно-импульсных компараторов, первый и второй выходы которого непосредственно, а третий - через первый элемент задержки

подключены к S - входам триггера интервалов, третий и четвертый выходы непосредственно, а первый - через второй элемент задержки к R-входам триггера интервалов, причем четвертый и второй йыходы блока амплитудно-импульсных компараторов через третий и четвертый элементы задержки подключены соответственно к S и R-входам триггера реверса, а выходы триггера реверса и триггера интервалов подключены ко входам дешифратора.

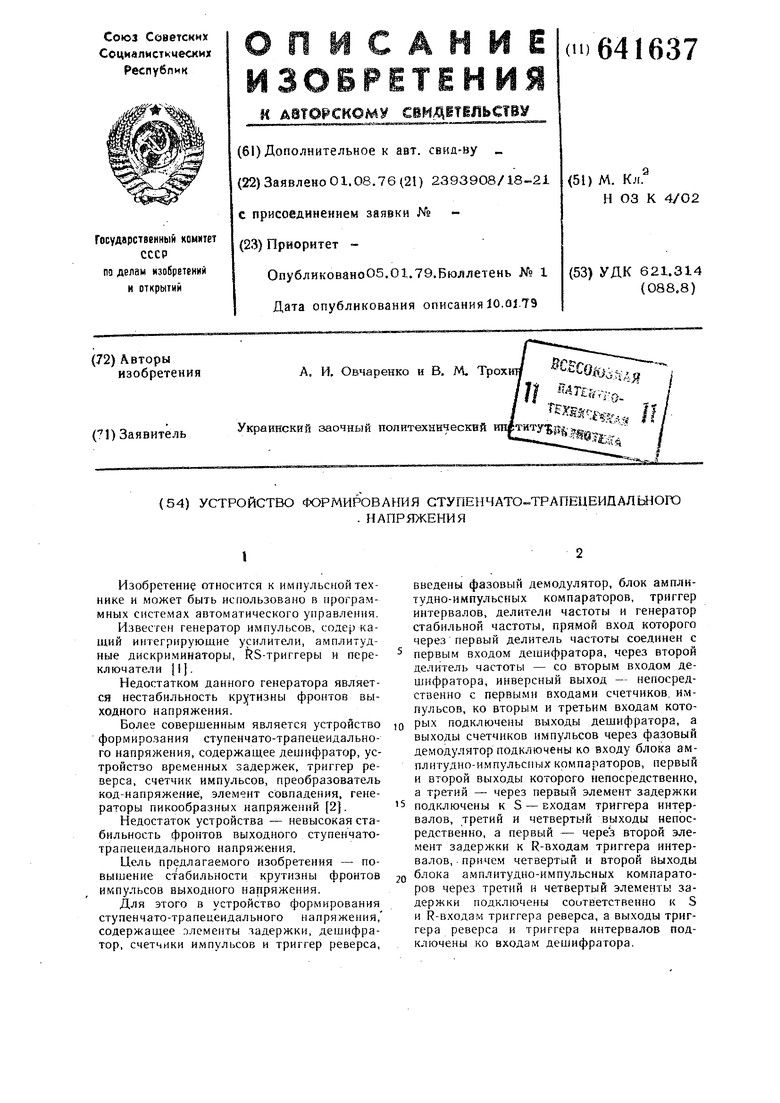

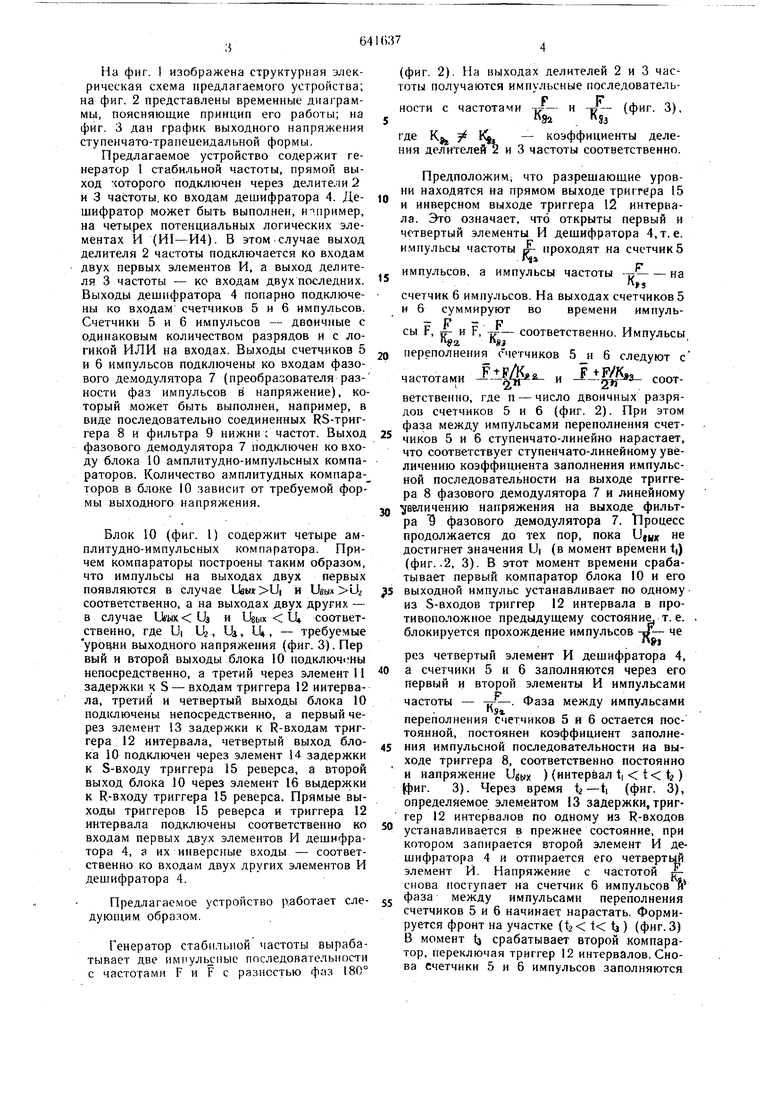

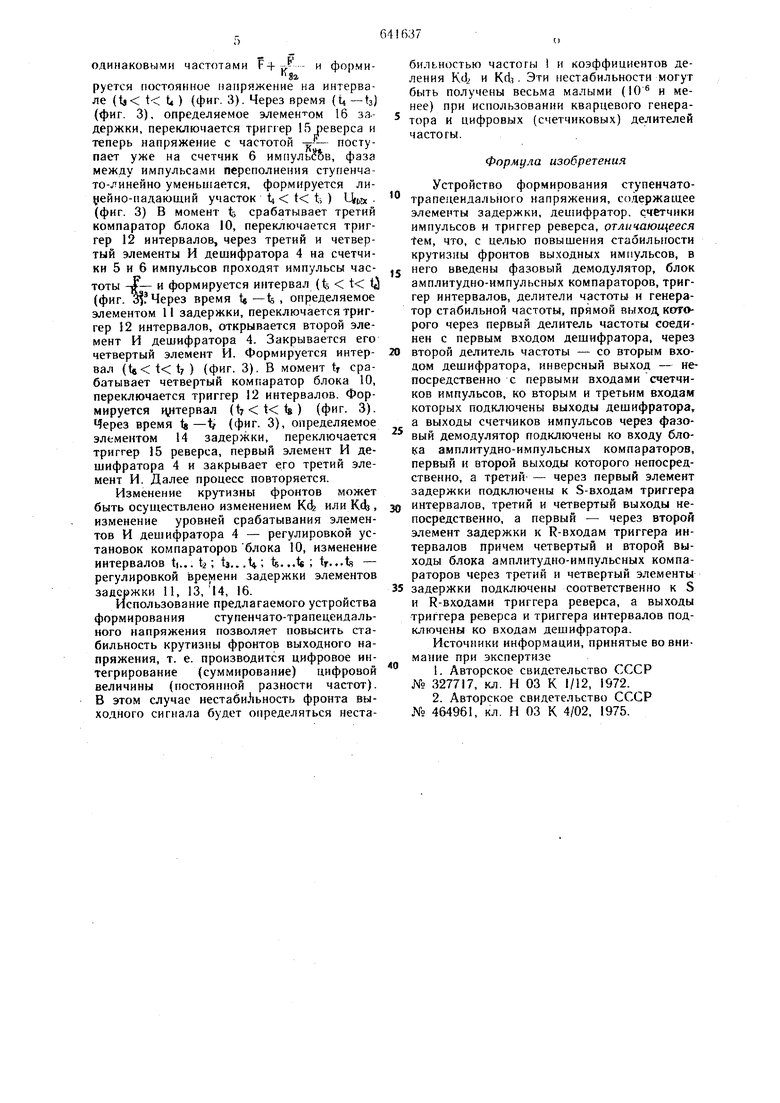

На фиг. 1 изображена структурная элекрическая схема предлагаемого устройства; на фиг. 2 представлены временные диаграммы, поясняющие принцип его работы; на фиг. 3 дан график выходного напряжения ступенчато-трапецеидальной формы.

Предлагаемое устройство содержит генератор 1 стабильной частоты, прямой выход чоторого подключен через делители 2 и 3 частоты, ко входам дешифратора 4. Дешифратор может быть выполнен, например, на четырех потенциальных логических элементах И {И1-И4). В этом случае выход делителя 2 частоты подключается ко входам двух первых элементов И, а выход делителя 3 частоты - ко входам двух последних. Выходы дешифратора 4 попарно подключены ко входам счетчиков 5 и 6 импульсов. Счетчики 5 и 6 импульсов - двоичные с одинаковым количеством разрядов и с логикой ИЛИ на входах. Выходы счетчиков 5 и 6 импульсов подключены ко входам фазового де.модулятора 7 (преобразователя разности фаз импульсов в напряжение), который может быть выполнен, например, в виде последовательно соединенных RS-триггера 8 и фильтра 9 нижни с частот. Выход фазового демодулятора 7 подключен ко входу блока 10 амплитудно-импульсных компараторов. Количество амплитудных компара- торов в блоке 10 зависит от требуемой формы выходного напряжения.

Блок 10 (фиг. I) содержит четыре амплитудно-импульсных компаратора. Причем компараторы построены таким образом, что импульсы на выходах двух первых появляются в случае lJfaKjf U| и Usbw Ц соответственно, а на выходах двух других - в случае Ua и Цьгх U соответ ствеино, где Ц Ц, Ua, iX, - требуемые уровди выходного напряжения (фиг. 3). Пер вый и второй выходы блока 10 подключоны непосредственно, а третий через элемент 11 задержки к S - входам триггера 12 интервала, третий и четвертый выходы блока 10 подключены непосредственно, а первый через элемент 13 задержки к R-входам триггера 12 интервала, четвертый выход блока 10 подключен через элемент 14 задержки к S-входу триггера 15 реверса, а второй выход блока 10 через элемент 16 выдержки к R-входу триггера 15 реверса. Прямые выходы триггеров 15 реверса и триггера 12 интервала подключены соответственно ко входам первых двух элементов И дешифратора 4, а их инверсные входы - соответственно ко входам двух других элементов И дешифратора 4.

Предлагаемое устройство работает следующим образом.

Генератор стабильной частоты вырабатывает две им11уль с-пые ппследователыюсти с частотами F и F с разностью фг13 180°

(фиг. 2). Иа выходах делителей 2 и 3 частоты получаются импульсные последовательF

--/- (фиг. 3),

НОСТИ с частотами и

Ъ7

Но «За

где К 1 - коэфф

ициенты деления делителей 2 и 3 частоты i соответственно.

Предположим; что разрешающие уровни находятся на прямом выходе триггера 15 и инверсном выходе триггера 12 интервала. Это означает, что открыты первый и четвертый элементы И дешифратора 4,т.е.

импульсы частоты S- проходят на счетчик 5 Л

импульсов, а импульсы частоты --Q-на

счетчик 6 импульсов. На выходах счетчиков 5 и 6 суммируют во времени импуль F - F

сы F, 5т- и F, - соответственно. Импульсы i

переполнения счетчиков 5 и 6 следуют с

частотами -F--|4r и соответственно, где п - число двоичных разрядов счетчиков 5 и 6 (фиг. 2). При этом фаза между импульсами переполнения счетчиков 5 и 6 ступенчато-линейно нарастает, что соответствует ступенчато-линейному увеличению коэффициента заполнения импульсной последовательности на выходе триггера 8 фазового демодулятора 7 и линейному

увеличению напряжения на выходе фильтра фазового демодулятора 7. Т роцесс продолжается до тех пор, пока не достигнет значения Ц (в момент времени t|) (фиг. .2, 3). В этот момент времени срабатывает первый компаратор блока 10 и его

выходной импульс устанавливает по одному из S-входов триггер 12 интервала в противоположное предыдуш,ему состояние, т. е. блокируется прохождение импульсов че

рез четвертый элемент И дешифратора 4,

а счетчики 5 и 6 заполняются через его

первый и второй элементы И импульсами

частоты - тг Фаза между импульсами

се

переполнения счетчиков 5 и 6 остается постоянной, постоянен коэффициент заполнения импульсной последовательности на выходе триггера 8, соответственно постоянно и напряжение ) (интервал t| t t) w. 3). Через время iz - ti (фнг. 3), определяемое элементом 3 задержки, триггер 12 интервалов по одному из R-входов

устанавливается в прежнее состояние, при котором запирается второй элемент И дешифратора 4 и отпирается его четверть|й элемент И. Напряжение с частотой J снова поступает на счетчик 6 импульсов ft

фаза между импульсами переполнения счетчиков 5 и 6 начинает нарастать. Формируется фронт на участке (t2 К tj) (фиг. 3) В момент 1з срабатывает второй компаратор, переключая триггер 12 интервалов. Снова счетчики 5 и 6 импульсов заполняются

одинаковыми частотами F+T/ - и фопми Яа

руется постоянное aI pяжeниe на интервале (t) t ti ) (фиг. 3). Через время (t - ts) (фиг. 3), определяемое элементом 16 задержки, переключается триггер 5реверса и теперь напряжение с частотой поступает уже на счетчик 6 импульЙв, фаза между импульсами переполнения ступенчато-линейно уменьшается, формируется лиуейно-падающий участок t, t t ) Цю (фиг. 3) В момент io срабатывает третий компаратор блока 10, переключается триггер 12 интервалов, через третий и четвертый элементы И дешифратора 4 на счетчики 5 и 6 импульсов проходят импульсы частоты -f- и формируется интервал (fe t t (фиг. Через время 1« -ts , определяемое элементом 11 задержки, переключается триггер 12 интервалов, открывается второй элемент И дешифратора 4. Закрывается его четвертый элемент И. Формируется интервал (1 t t ) (фиг. 3). В момент tr срабатывает четвертый компаратор блока 10, переключается триггер 12 интервалов. Формируется у1тервал (t t tg ) (фиг. 3). Через время Ig -t (фиг. 3), определяемое элементом 14 задержки, переключается триггер 15 реверса, первый элемент И дешифратора 4 и закрывает его третий элемент И. Далее процесс повторяется.

Изменение крутизны фронтов может быть осуществлено изменением К,А/. или Kcfe , изменение уровней срабатывания элементов И дешифратора 4 - регулировкой установок компараторов блока 10, изменение интервалов ti...t2; 1з..Л; t.-.tsi .-ts - регулировкой времени задержки элементов задержки 11, 13, 14, 16.

Использование предлагаемого устройства формирования ступенчато-трапецеидального напряжения позволяет повысить стабильность крутизны фронтов выходного напряжения, т. е. производится цифровое интегрирование (суммирование) цифровой величины (постоянной разности частот). В этом случае нестабильность фронта выходного сигнала будет определяться нестабильностью частоты I и коэффициентов деления и Kd:. Эти нестабильности могут быть получены весьма малыми (10 н менее) при использовании кварцевого генератора и цифровых (счетчиковых) делителей частогы.

Формула изобретения

Устройство формирования ступенчатотрапецеидального напряжения, со.аержащее элементы задержки, дешифратор, счетчики импульсов и триггер реверса, отличающееся teM, что, с целью повышения стабильности крутизны фронтов выходных импульсов, в него введены фазовый демодулятор, блок амплитудно-импульсных компараторов, триггер интервалов, делители частоты и генератор стабильной частоты, прямой выход которого через первый делитель частоты соединен с первым входом дешифратора, через второй делитель частоты - со вторым входом дешифратора, инверсный выход - непосредственно с первыми входами счетчиков импульсов, ко вторым и третьим входам которых подключены выходы дешифратора, а выходы счетчиков импульсов через фазовый демодулятор подключены ко входу блока амплитудно-импульсных компараторов, первый и второй выходы которого непосредственно, а третий - через первый элемент задержки подключены к S-входам триггера интервалов, третий и четвертый выходы непосредственно, а первый - через второй элемент задержки к R-входам триггера интервалов причем четвертый и второй выходы блока амплитудно-импульсных компараторов через третий и четвертый элементы задержки подключены соответственно к S и R-входами триггера реверса, а выходы триггера реверса и триггера интервалов подключены ко входам дешифратора.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 327717, кл. Н 03 К 1/12, 1972.

2.Авторское свидетельство СССР № 464961, кл. Н 03 К 4/02, 1975.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации многоканального воспроизведения с носителя магнитной записи | 1984 |

|

SU1150660A1 |

| Многоканальная система передачи и приема информации | 1986 |

|

SU1332550A1 |

| Устройство для измерения нелинейности пилообразного напряжения | 1986 |

|

SU1406528A1 |

| Цифровой демодулятор частотно-манипулированных сигналов | 1982 |

|

SU1058083A1 |

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В НАПРЯЖЕНИЕ | 1987 |

|

RU2056700C1 |

| Устройство для автоматической подстройки частоты | 1980 |

|

SU886250A2 |

| Устройство для измерения нелинейности пилообразного напряжения | 1990 |

|

SU1777101A1 |

| Цифровой демодулятор сигналов | 1989 |

|

SU1589420A1 |

| Устройство для считывания графической информации | 1981 |

|

SU1013989A1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 1995 |

|

RU2076458C1 |

Авторы

Даты

1979-01-05—Публикация

1976-08-01—Подача