1

Изобретение относится к автоматике и вычислительной технике и может быть использовано в постоянных запоминающих устройствах.

Одно из известных запоминающих устройств трансформаторного типа содержит запоминающие трансформаторы, выходные обмотки которых подключены к входам усилителей воспроизведеиия, а выходы усилителей считывания соединены с регистром числа. Устройство содержит также элементы совпадения и токозадающие элементы по числу разрядов, токозадающие элементы соединены с входами усилителей воспроизведения. Такое включение токозадающих элементов повышает быстродействие устройства, однако это сопровождается усложнением схемы и увеличением количества оборудования. Наиболее близким к изобретению является устройство, содержащее прошитые числовыми проводами запоминающие трансформаторы, обмотки считывания которых подключены к коллекторам первых и к базам вторых транзисторов усилителей считывания, коллекторы котгрых соединены совхОдами триггеров регистра числа. Первые транзисторы выполняют роль ключей: при открывании этих транзисторов входы вторых каскадов усилителей шунтируются.

ри этом блокируется воздействие выходного сигнала в обмотке считывания на вход второго каскада {2.

Недостатком устройства является сравнительно малое быстродействие устройства.

Целью изобретения является повыщение быстродействия устройства. Поставленная цель достигается тем, что в устройстве

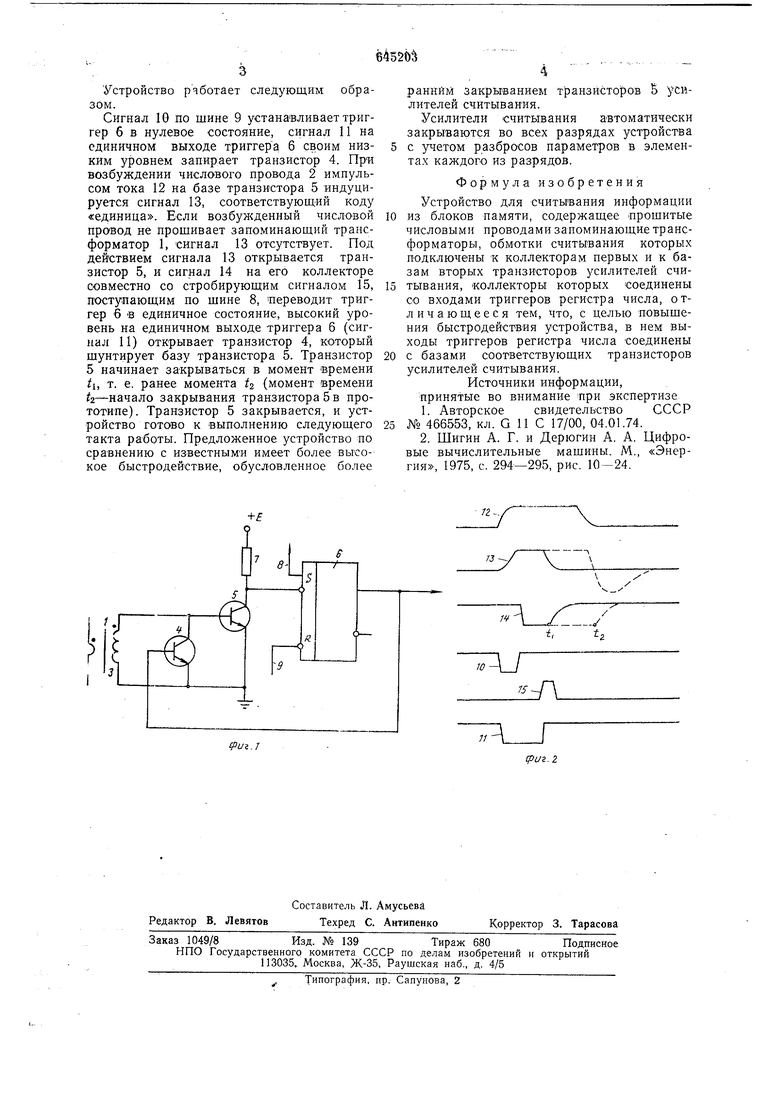

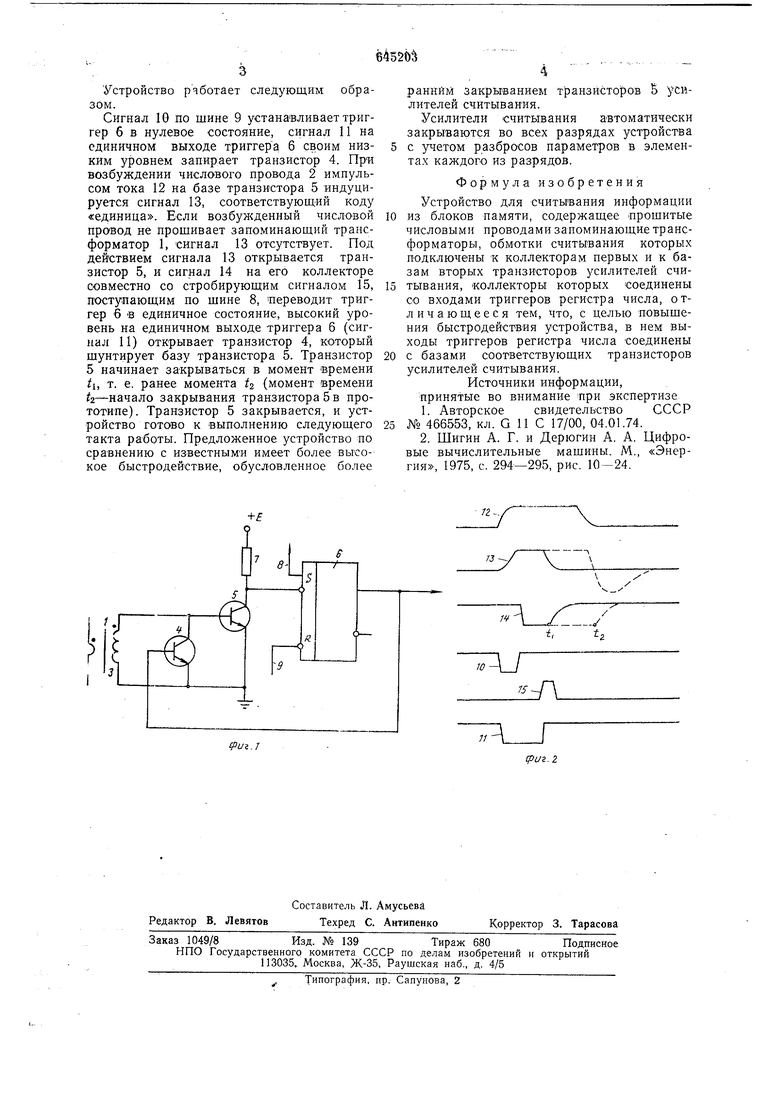

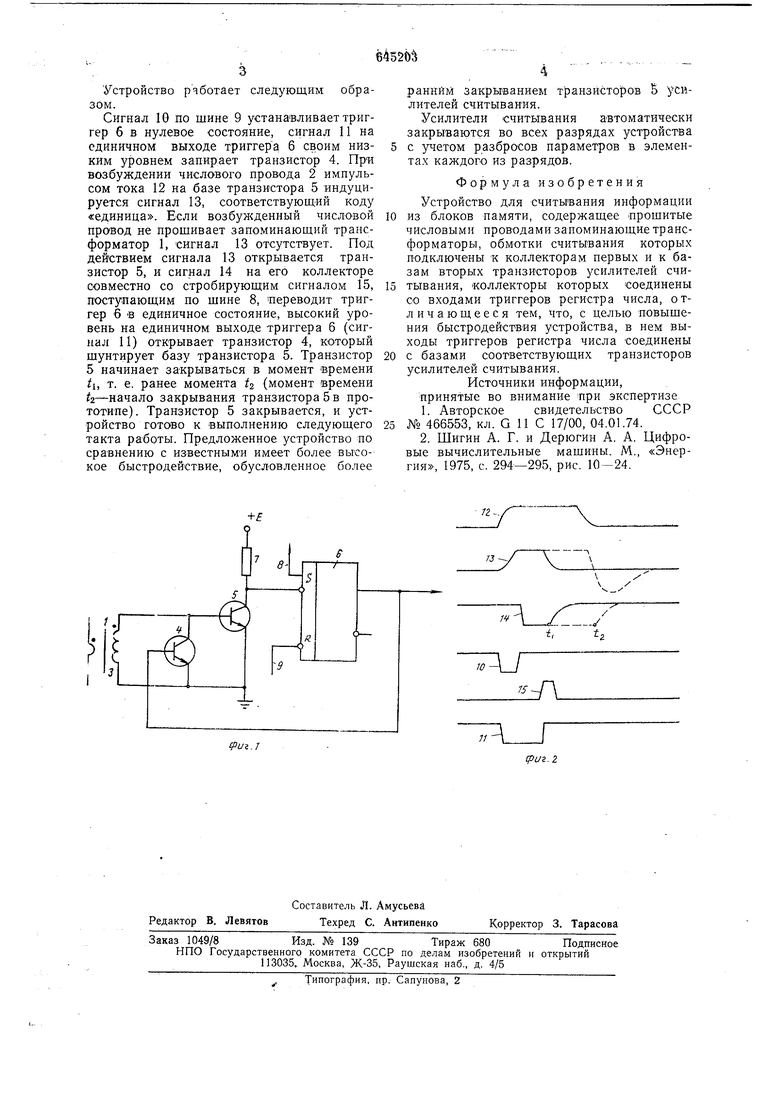

для считывания информации из блоков памяти выходы триггеров регистра числа соединены с базами соответствующих транзисторов усилителей считывания. На фиг. 1 представлена схема устройства; на фиг. 2 - временная диаграмма основных сигналов (пунктиром показана форма сигналов в прототипе).

Устройство содержит запоминающие трансформаторы 1, прошитые числовыми проводами 2. Обмотка считывания 3 трансформатора 1 подключена к коллектору первого транзистора 4 и к базе второго тран.зистора 5. Коллектор транзистора 5 соединен с информационным входом триггера 6 и через резистор 7 - с источником питания + Е. Шины 8 и 9 - шины стробирования и установки триггера в нуль соответственно. Выход триггера соединен с баЗОЙ транзистора 4.

Устройство работает следующим образом.

Сигнал 19 по шине 9 устанавливает триггер б в нулевое состояние, сигнал 11 на единичном выходе триггера 6 своим низким уровнем занирает транзистор 4. Пртг возбуждении числового провода 2 импульсом тока 12 на базе транзистора 5 индуцируется сигнал 13, соответствующей коду «единица. Если возбужденный числовой провод не прощивает запоминающий трансформатор 1, сигнал 13 отсутствует. Под действием сигнала 13 открывается транзистор 5, и сигнал 14 на его коллекторе совместно со стробирующим сигналом 15, поступающим по шине 8, переводит триггер 6 В единичное состояние, высокий уровень на единичном выходе триггера 6 (сигнал 11) открывает транзистор 4, который шунтирует базу транзистора 5. Транзистор 5 начинает закрываться в момент времени ti, т. е. ранее момента t (момент времени 2-начало закрывания транзистора 5 в прототипе). Транзистор 5 закрывается, и устройство готово к выполнению следующего такта работы. Предложенное устройство по сравнению с известным-и имеет более высокое быстродействие, обусловленное более

раннйМ закрыванием транзисторов В усилителей считывания.

Усилители считывания автоматически закрываются во всех разрядах устройства с учетом разбросов параметров в элементах каждого из разрядов.

Формула изобретения

Устройство для считывания информации из блоков памяти, содержащее прошитые числовыми проводами запоминающие трансформаторы, обмотки считывания которых подключены к коллекторам первых и к базам вторых транзисторов усилителей считывания, Коллекторы которых соединены со входами триггеров регистра числа, отличающееся тем, что, с целью повышения быстродействия устройства, в нем выходы триггеров регистра числа соединены с базами соответствующих транзисторов усилителей считывания.

Источники информации, принятые во виимание при экспертизе

1.Авторское свидетельство СССР № 466553, кл. G И С 17/00, 04.01.74.

2.Шигин А. Г. и Дерюгин А. А. Цифровые вычислительные машины. М., «Энергия, 1975, с. 294-295, рис. 10-24.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для считывания информации из блоков памяти | 1978 |

|

SU746719A1 |

| Трансформаторное постоянное запоминающее устройство | 1985 |

|

SU1352534A1 |

| Трансформаторное постоянное запоминающее устройство | 1977 |

|

SU651417A2 |

| СПОСОБ ЗАПИСИ ИНФОРМАЦИИ В ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА МАГНИТНЫХ СЕРДЕЧНИКАХ И ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА СЕРДЕЧНИКАХ | 1992 |

|

RU2101784C1 |

| Постоянное запоминающее устройство | 1978 |

|

SU734808A1 |

| Запоминающее устройство | 1976 |

|

SU597006A1 |

| Трансформаторное постоянное запоминающее устройство | 1982 |

|

SU1072097A1 |

| Трансформаторное постоянное запо-МиНАющЕЕ уСТРОйСТВО | 1979 |

|

SU841048A1 |

| Устройство для выборки информации | 1978 |

|

SU809344A1 |

| ИНВЕРТОР | 1994 |

|

RU2066513C1 |

Авторы

Даты

1979-01-30—Публикация

1977-11-21—Подача