(54) ИМИТАТОР ОШИБОК В ГРУППОВОМ ТРЛКТЕ ЦИФРОВЫХ СИСТЕМ ПЕРЕДАЧИ

WS последовательно соединенных генерйтора модулируюдего сигнала и делителя напряжения, выход которого подключен к N цепям, каждая которых состоит из последовательно соединенных порогового блока и триггера, выход которого соединен с соответствующим входом переключателя положение, а блок ввода ошибок в цифровой поток состоит из последовательно соединенных первого блока стробирования, первый и второй входы которого являются первым и вторым входами имитатора, сумматора по модулю два, к второму входу которого через первый инвертор подключен второй выход первого блока стробирования, и второго блока стробирования, к второму входу которого через элемент задержки подключен второй вход имитатора, соединенный также с первым входом третьего блока стробирования, второй вход которого соединен с выходом переключателя на N +1 положение, а первый и второй выходы третьего блока стробирования соединены с соответствующими входами с;а; оенного переключателя на два положения, первый и второй выходы которого соединены соответственно с третьим и четвёртым входами сумматора по модулю два, введен формирователь длительностей ошибок, состоящий из кольцевого счетчика-распределител на К + .позицию, выход первой из которых подключен к первым входам N двухвходовых элементов совпадения, выход каждого из которых через триггер, второй, вход которого соединен с соответствующим выходом кольцевого счетчика-распределителя, подключен к одному из входов элемента ИЛИ, выход которого подключен к входу второго инвертора, при этом второй вход каж дого из двухвходовых элементов совпадения через введенный соответствующий ключ соединен с выходом соответствующего триггера формирователя длительностей интервалов между ошибками второй вход которого через введенный соответствующий ключ соединен с соответствующим выходом кольцевого счетчика-распределителя, вход которого подключен к второму входу имитатора, а выход элемента ИЛИ и выход второго инвертора соединены с соответствующими входами сдвоенного переключателя на два пйложени.я.

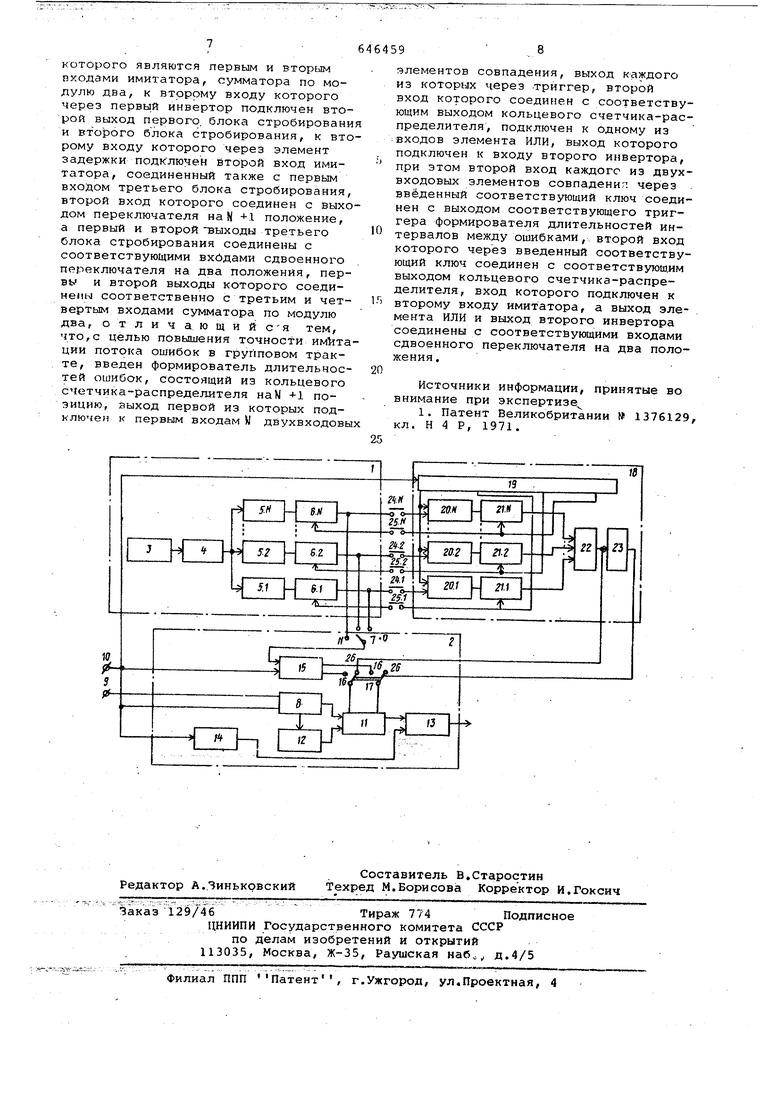

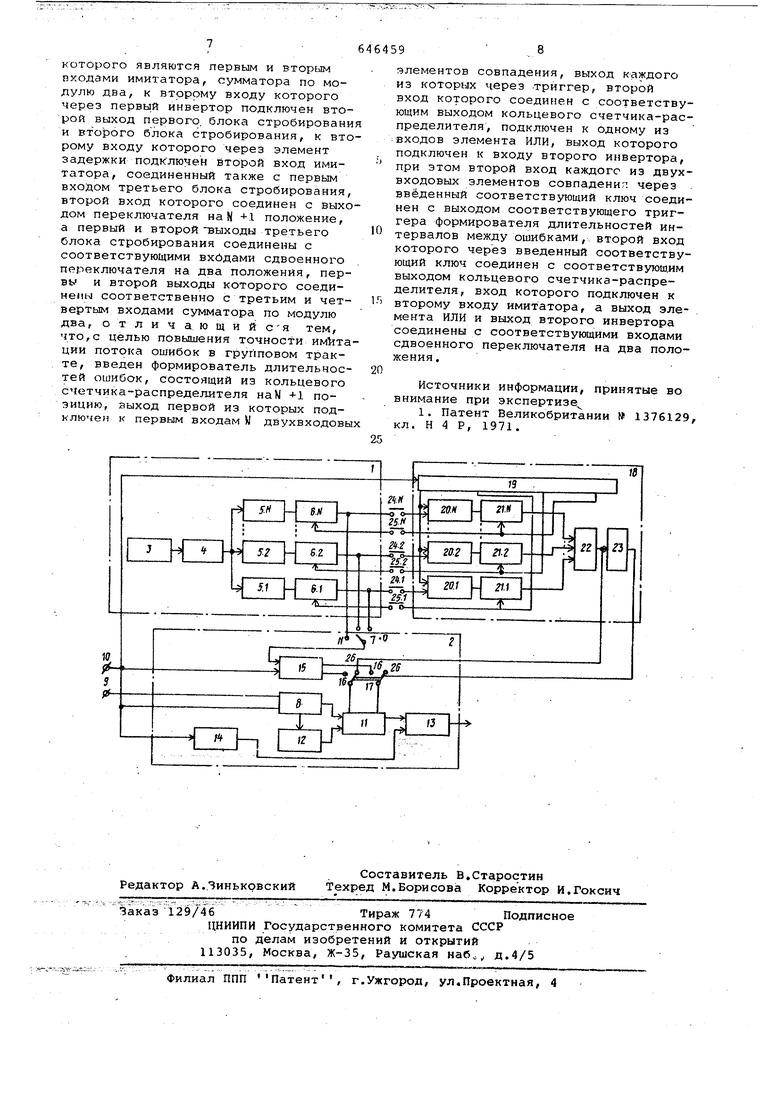

На чертеже пг ведена структурная электрическая схема имитатора.

Имитатор ошибок в групповом тракте цифровых систем передачи содержит формирователь 1 длительностей интервалов между ошибками и блок 2 для ввода ошибок в цифровой поток, причем формирователь 1 длительностей интервалов между ошибками состоит из последовательно соединенных генератора 3 модулиру1ощего сигнала

и делителя 4 напрям ения, вход которого подключен к W цепям,, причем { -я цепь состоит из последовательно соединенных порогового блока 5.t и триггера 6.jr, где i, - 1,2,..W , Выход триггера 6, J, соединен с соответствующим входом переключателя 7

HaN + l положение. Блок 2 для ввода ошибок в цифровой поток состоит из последовательно соединенных первого блока стробирования 8, первый и второй входы которого являются первым

и вторым входами 9 и 10 имитатора, сумматора по модулю два 11, к второму входу которого через первый инвертор 12 подключен второй выход первого .блока стробирования 8, и второго бло. ка стробирования 13, к второму входу которого через элемент задержки 14 подключен второй вход 10 имитатора. Второй вход 10 имитатора соединен также с первым входом третьего блока

0 стробирования 15, второй вход которого соединен с выходом переключателя 7 на W 4-1 положение, а первый и второй выходы третьего блока стробирования 15 соединены с соответствующими входами 16 сдвоенного переключателя 17 на два положения, первый и второй выходы которого соединены соответственно с третьим и четвертым входами сумматора по модулю два 11. Кроме

0 того, имитатор ошибок в групповом тракте цифровых систем передачи содержит формирователь длительностей ошибок 18, состоящий из кольцевого г-четчика-распределителя 19 наМ +1

с, позицию, выход первой из которых

подключен к первым входам Н двухвходовых элементов совпадения 20.1 20.М, а выход |;вухвходового элемента совпадения 20„, где -1,2 ,..,N, через триггер 2l,i, второй вход которого соединен с соответствующим выходом, кольцевого счетчика-райпределителя 19, подключен к одному из входов элемента ИЛИ 22, выход которого подключен к входу второго инвертора 23, при этом второй вход двух5входового элемента совпадения 20.i через введенный соответствующий ключ 24,« соединен с выходом соответствующего триггера 6,i формирователя 1 - длительностей интервалов между ошиб,. ками,второй вход которого через введенный соответствующий ключ 25.i соединен с соответствующим выходом кольцевого счетчика-распределителя 19, вход которого подключен к второму входу 10 имитатора, а выход эле мента ИЛИ 22 и выход второго инвертора 23 соединены с соответствующими входами 26 сдвоенного переключателя 17 на два положения.

Имитатор ошибок работает следующим образом.

При формировании потока ошибок, 5 содержащего импульсы, длительность

которых равна одному периоду тактовой частоты искажаемого цифрового потока, ключи 24.1 и 25.1 замкнуты, а ключи 24.2 - 24.W и 25.2 - 25.N разомкнуты. Сдвоенный переключатель 17 на два положения замкнут на входы 26, а переключатель 7 на N +1 положение находится в положении 0. Сигнал с выхода генератора 3 модулирующего сигнала через делитель 4 напряжения поступает на вход порогового блока 5,1, на выходе которого формируется импульсная последовательность, определяемая пересечением уровней входного модулирующего напряжения и порогом срабатывания порогового блока 5,1 о Через ключ 24.1 сигнал с выхода триггера 6,1 поступает на второ вход двухвходового элемента совпадения 20.1, на выходе которого в момен совпадения сигнала с выхода триггера 6.1 и импульса первой позиции кольцевого счетчика-распределителя 19 формируется сигнал, запускающий триггер 21.1. Установка в О триггеров 6,1 и 21.1 производится импульсом второй позиции кольцевого счетчика-распределителя 19.

Таким образом, длительность импульса, сформированного на выходе триггера 21.1, равна одному периоду тактовой частоты искажаемого цифрового потока. Этот сигнал поступает н один из входов элемента ИЛИ 22.

Аналогичным образом формируются потоки ошибок, содержащие импульсы длительностью в 2, 3,.,N,-периодов тактовой частоты искажаемого цифрового потока,

При замыкании ключей 24,1 - 24,N и 25.1- 25.yj на выходе элемента ИЛИ 22 формируется поток ошибок, содержащий импульсы длительностью в -1, 2,..,М периодов тактовой частоты Частота появления импульсов в потоке ошибок и их длительности определяются как уровнем модулирующего сигнала так и значениями порогов срабатывания пороговых элементов 5.1 - 5,N которые управляют формированием импульсов определенной длительности в потоке ошибок.

В блоке ввода ошибок в цифровой поток 2 сумматор по модулю два 11 осуществляет поразрядное суммирование по модулю два цифрового потока системы передачи и потока ошибок. На третий и четвертый входы сумматора по модулю два через сдвоенный переключатель 17 подается поток ошибок в прямом и инверсном видах, вырабатываемый третьим блоком стробирования 15 или элементом ИЛИ 22. Hai первый и второй входы сумматора по модулю два 11 подается прямой и инверсный потоки системы п - редачи с выходов первого блока стробирования 8 и первого инвертора 12. На первый

и второй входы первого блока стробп рования 8 с первого и второго входом 9 и 10 имитатора поступают соответственно цифровой сигнал и сигнал тактовой частоты. Сигнал с выхода сумматора по модулю два 11 поступает на первый.вход второго блока стробирования 13, на второй вход которого через элемент задержки 14 подается сигнал тактовой частоты с второго входа 10 имитатора, Элемент задержки 14 служит для компенсации временных

0 задержек, вносимых элементами имитатора.

В частном случае имитатор может формировать потоки ошибок, в которых длительности импульсов и интервалы

Г, между ними распределены по нормальному закону. При работе в этом режиме ключи 24,1 - 24,и и 25,1 - 25,W разомкнуты, переключатель 7 находится в одном из и положений, а сдвоенный переключатель 17 находится в положении,

0 когда замкнуты его входы 16. Сигнал с выхода генератора 3 модулирующего сигнала через делитель 4 напряжения поступает на входы пороговых блоков 5,1 - 5.N, имеющих различные пороги

5 срабатывания, С выходов пороговых , блоков 5,1 - 5,1 сигналы поступают на счетные входы триггеров 6,1 - 6.М, с выхода одного из которых через переключатель 7 сигнал по0дается на второй вход третьего блока стробирования 15, первый вход которого является вторым входом 10 имитатора .

Предложенный имитатор ошибок в групповом тракте цифровых систем передачи отличается повышенной точностью имитации потока ошибок и позволяет формировать этот поток по любому заданному закону с любым распределением длительностей пачек ошибок.

Формула изобретения

Имитатор ошибок в групповом тракте цифровых систем передачи, содержащий формирователь длительностей интервалов между ошибками и блок ввода ошибок в цифровой поток, причем формирователь длительностей интервалов между ошибками состоит из последовательно соединенных генератора модулирующего сигнала и делителя напряжения, выход которого подключен к N цепям, каждая из которых состоит из последовательно соединенных порогового блока и триггера, выход котброго соединен с соответствуккцим входом переключателя на H-t-l положение, а блок ввода ошибок в цифровой поток состоит из последовательно соединенных первого- блока стробирования, первый и второй входь

которого являются первым и вторым пходами имитатора, сумматора по модулю два, к второму входу которого через первый инвертор подключен второй выход первого, блока стробировани и втЪрого блока стробирования, к второму входу которого через элемент задержки подключем второй вход имитатора, соединенный также с первым входом третьего блока стробирования, второй вход которого соединен с выходом переключателя на N +1 положение, а первый и второй выходы третьего блока стробирования соединены с соответствующими вхйдами сдвоенного переключателя на два положения, первы и второй выходы которого соединены соответственно с третьим и четвертым входами сумматора по модулю два, отлич ающййся тем, что,с целью повышения точности им тации потока ошибок в групповом тракте, введен формирователь длительностей ошибок, состоящий из кольцевого счетчика-распределителя наИ +1 позицию, аыход первой из которых подключен к первым входам W двухвходовы

элементов совпадения, выход каждого из которых через триггер, второй вход которого соединен с соответствующим выходом кольцевого счетчика-распределителя, подключен к одному из :входов злемента ИЛИ, выход которого подключен к входу второго инвертора, при этом второй вход каждого из двухвходовых элементов совпадение через введенный соответствующий ключ соединен с выходом соответствующего триггера формирователя длительностей интервалов между ошибками,, второй вход которого через введенный соответствующий ключ соединен с соответствующим выходом кольцевого счетчика-распределителя, вход которого подключен к второму входу имитатора, а выход элемента ИЛИ и выход второго инвертора соединены с соответствующими входами сдвоенного переключателя на два положения.

Источники информации, принятые во внимание при экспертизе

1. Патент Великобритании 1376129 кл. Н 4 Р, 1971.

| название | год | авторы | номер документа |

|---|---|---|---|

| Имитатор ошибок в групповом тракте цифровых систем передачи | 1986 |

|

SU1319291A2 |

| Устройство формирования испытательных сигналов для многоканальной системы связи с импульсно-кодовой модуляцией и временным разделением каналов | 1980 |

|

SU930713A2 |

| Цифровой демодулятор сигналов с относительной фазовой модуляцией | 1981 |

|

SU985970A1 |

| Устройство магнитной записи сигналов цифровой информации | 1983 |

|

SU1157566A1 |

| Имитатор цифрового телевизионногоСигНАлА | 1978 |

|

SU815966A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ РАДИОТЕЛЕМЕТРИЧЕСКИХ СИГНАЛОВ | 1994 |

|

RU2126139C1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2014 |

|

RU2549360C1 |

| Устройство контроля ошибок многоканальной аппаратуры магнитной записи | 1987 |

|

SU1529285A1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2011 |

|

RU2460225C1 |

| РАДИОПРИЕМНОЕ УСТРОЙСТВО МНОГОЧАСТОТНЫХ СИГНАЛОВ | 2005 |

|

RU2310992C2 |

Авторы

Даты

1979-02-05—Публикация

1976-06-04—Подача