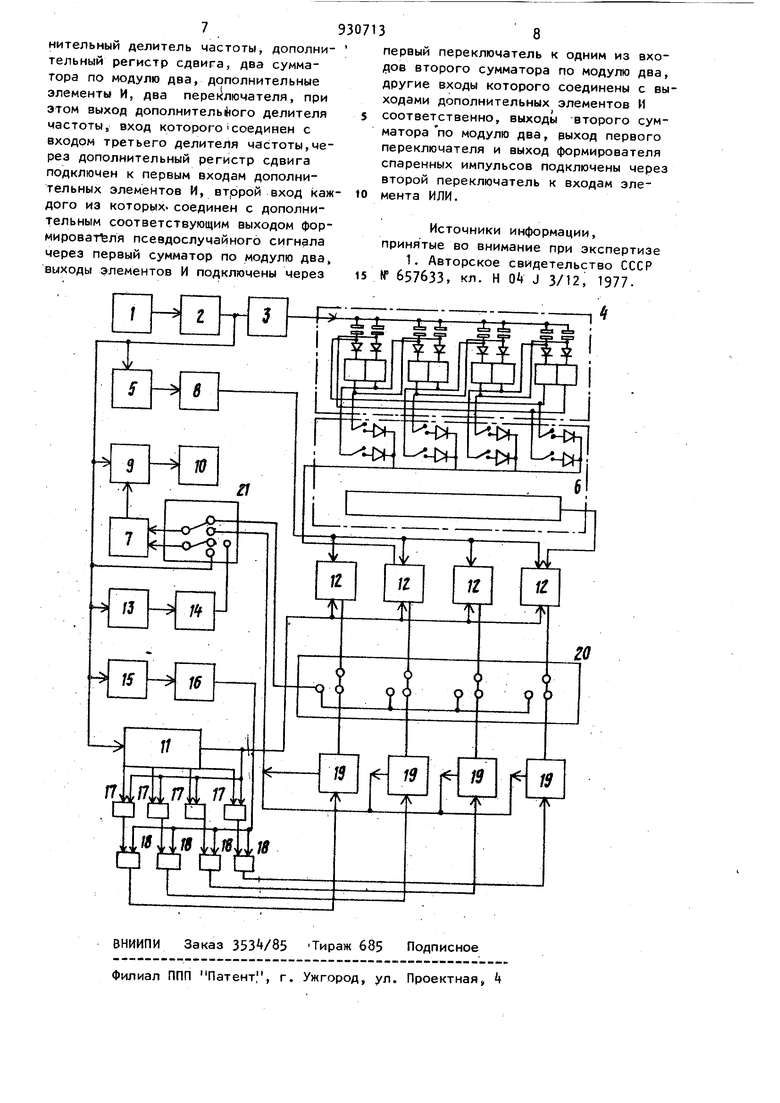

3 ,93 тельный делитель частоты, дополнительныи регистр сдвига, два сумматора по модулю два, дополнительные элементы И, два переклю4ателя, при этом выход дополнительного{делителя частоты, вход которого соединен с входом третьего делителя частоты, через дополнительный регистр сдвига подключен к первым входам допрлнительных элементов И, второй вход каж дого из которых соединен с дополнительным соответствующим выходом формирователя псевдослучайного си)- нала через первый сумматор по модулю два, выходы элементов И подключены через первый переключатель к одни из входов второго сумматора по модуг лю два, другие входы которого соединены с выходами дополнительных элементов И соответственно, выходы второго сумматора по модулю два, .выход первого переключателя и выход формирователя спаренных импульсов подключены через второй переключатель к входам элемента ИЛИ, На чертеже дана структурная элект рическая схема предлагаемого устройства . . Устройство формирования испытательных сигналов для многоканальной системы связи с импульсно-кодовой модуляцией и временным разделением каналов содержит задающий генератор 1, формирователь 2 тактовых импульсов, первый делитель 3 частоты, коль цевой делитель k частоты, второй делитель 5 частоты, блок 6 коммутации элемент ИЛИ 7, регистр 8 сдвига согласую1чий триггер 9, выходной формирователь 10 импульсов, формирователь 11 псевдослучайного сигнала, элементы И 12, третий делитель 13 частоты :|зормйрователь Т спаренных -импульсов , дополнительный делитель 15 частоты, дополнительный реги|стр 16 сдвига, первый сумматор 17 по модулю два, дополнительные элементы И 18, второй сумматор 19 по модулю два первый 20 и второй 21 переключатели Устройство работает следующим сэб разом. Импульсы тактовой частоты с задаю щего генератора 1 поступают з форми рователь 2 и первый делитель частот 3, который осуществляет дe ieниe так товой частоты с целью получения импульсов, кратных числу импульсов в предполагаемых служебных каналах 34 (например, установка импульсов стаффинга). Полученный в первом делителе 3 сигнал поступает в кольцевой делитеЛь частоты А, причеМ обеспечивается срабатывание лишь одного триггера, кольцевого делителя при поступлении с формирователя 2 импульсов в общую цепь запуска кольцевого делителя k. Число блоков 6 определяется ЧИСЛОМ служебных каналов. С формирователя 2 сигнал поступает в формирователь псевдослучайного сигнала 11, который имитирует информационный сигнал и в общем случае представляет собой регистр с сумматором по модулю два. Служебные сигналы с блока 6 коммутации и псевдослучайный сигнал с формирователя 11 поступают на один из входов элементов И 12, причем последовательность соединения указанных блоков .с элементами И 12 определяется структурой имитируемого сигнала, т.е. наличием одного канала служебной информации, затем информационного сигнала, т.е. псевдослучайного сигнала, далееопять служебного канала с импульсами стаффинга и т.д. На второй вход 31лементоЕ И 12 поступает сигнал с регистра 8 сдвига, управляемого сигналами с второго делителя 5 частоты. Регистр В сдвига осуществляет распределение указанных информационных и временных каналов, очередность их расположения относительно друг друга. Поэтому второй делитель 5 частоты и регистра сдвига 8 делят тактовую частоту с коэффициентами, зависящими от числа каналов и их расположением относительно друг друга. 8 элементе ИЛИ 7 осуществляется сборка всех канальных групп и далее сигнал поступает на согласующий триггер 9- На второй вход согласующего триггера 9 подаются импульсы тактовой частоты с формирователя 2, чем осуществляется синхронизация выходных импульсов с задающим генератором 1. Выходной формирователь .10 осуществляет формирование импульсной последовательности цифрового потока в соответствии с требуемой амплитудой и длительностью импульсов. Одновременно сигнал с задающего генератора 1 делится третьим.делителем 13 до величины сотен Гц, характерных для частоты ввода импульсов стаффинга и поступает в формирователь I, который формирует сигнал, имеющий +-,+-,.., Причем в зависимости от коэффициента деления третьего делителя 13 частота появления парных импульсов и пробелов изменяется (+- импульс --- пробел).

Указанные парные импульсы и пробелы определяют моменты изменения временного интервала между моментами записи и считывания. Указанная последовательность поступает на элемент ИЛИ 7, образуя испытательный сигнал, который позволяет определить помехозащищенность и а;1горитм работы устрЬйств синхронизации и объединения оконечного оборудования. С помощью ключей блока 6 можно имитировать ошибки (статические) и в служебных каналах.

При установке соответствующих клемм переключателя 20 и 21 в соответствующие положения в указанный ранее испытательный сигнал может быть введена дополнительная ошибка, формируемая по случайному закону. Сигнал через дополнительный делитель 15 частоты поступает в дополнительный регистр 16 сдвига, который осуществляет распределение импульсов ошибки по длительности. При этом могут быть сформированы потоки ошибок, содержащие импульсы длительностью в 1,2,3,---N периодов тактовой частоты. Для формирования этих потоков сигнал с дополнительного регистра 16 сдвига-подается на,дополнительные элементы И 18, навторой вход которых поступают сигналы с первых сумматоров 17 по модулю два, включенных в цепь формирователя псевдослучайного сигнала 11. При этом один вход первых сумматоров 17 по модулю два связан с выходом формирователя псевдослучайного сигнала 11, а вторые входы связдны с выходом разных ячеек дополнительного регистра 16 сдвига. Это позволяет сформироват N некогерёнтных потоков импульсов, подчиняющихся закону, определяемому формирователем псевдослучайного си1 нала 11, т,.е. получается N псевдослучайных сигналов.

Импульсы с выхода дополнительных элементов И 18, являющиеся элементами сигнала ошибок, длительность которых определяется дополнительным регистром сдвига 1б, поступают на один из входов второго сумматора по модулю два .19, на второй вход которого поступает сигнал с элементов И 12. Зторой сумматор 19 по модулю два осуществляет поразрядное суммирование по модулю дёа цифрового потока

ошибок и цифрового потока испытательного сигнала, распределенного по своим каналам элементами И 12. Указанные потоки поступают на вход элемента ИЛИ 7 и далее на выходной формирователь 10. При этом в каждый канал испытательного сигнала и служебных сигналов вводятся ошибки,распределенные по.случайному закону. Технико-экономическая эффективность изобретения заключается в том, что предлагаемое устройство обладает универсальностью по сравнению с известным, сравнительной простотой построения, гибкостью позволяя формировать испытательный сигнал без ошибок и с динамическими и статическими ошибками в каждом канале.

Причем в процессе контроля повышается точность контроля узлов синхронизации и оконечной аппататуры в

целом, так как появляется возможность вводить случайную ошибку в информационные и служебные каналы сложного испытательного сигнала. При этом

устройство работает либо как генератор испытательных сигналов, либо как генератор испытательного сигнала с введенной нормированной ошибкой.Получение случайной последовательности

ошибок осуществляется от имеющегося формирователя псевдослучайной последовательностью с помощью сумматоров .по модулю два. При этом потоки ошибок некогерентны с сигналом ПСП.

Одновременно вводя ошибки в различные каналы испытательного сигнала, можно более точно оценить помехозащищенность отдельных узлов оконечно- . го оборудования, приближая условия

работы аппаратуры к реальным условиям.

Формула изобретения

Устройство формирования испытательных сигналов для многоканальной системы связи с импульсно-кодовой модуляцией и временным разделением каналов по авт. св. СССР № б57бЗЗ, отличающееся тем, что, с целью обеспечения возможности формирования ошибок и введения их в испытательные сигналы, введены допол

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство формирования испытательных сигналов для многоканальной системы связи с импульно-кодовой модуляцией и временным разделением каналов | 1977 |

|

SU657633A1 |

| Устройство для передачи и приема информации с временным уплотнением каналов | 1978 |

|

SU746951A2 |

| Устройство фазирования псевдослучайных последовательностей | 1986 |

|

SU1381726A1 |

| Устройство для контроля аппарата магнитной записи | 1985 |

|

SU1283848A1 |

| Устройство для контроля ошибок многоканального аппарата магнитной записи | 1987 |

|

SU1432604A1 |

| Устройство для цикловой синхронизации | 1976 |

|

SU640439A1 |

| Устройство для передачи и приема дискретной информации | 1980 |

|

SU886295A1 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

| Устройство для контроля синхронизма воспроизведенных сигналов | 1988 |

|

SU1585833A1 |

| Устройство для контроля сбоев псевдослучайного испытательного сигнала | 1983 |

|

SU1172056A1 |

Авторы

Даты

1982-05-23—Публикация

1980-07-07—Подача