1

Изобретение относится к радиосвязи и может использоваться в устройствах, исправляющих ошибки.

Известно декодирующее устройство, содержащее входной декодер, выходы которого подключены соответственно к входам накопителя информационных слов и накопителя избыточных слов, а также два блока ключей и блок мажоритарной обработки 1}.

Однако данное устройство не обладает достаточной помехозащищенностью

Цель изобретения - пов1лаение помехозащищенности при декодировании.

Для этого в декодирующее устройство, содержащее входной декодер, выходы которого подключены соответственно к входам накопителя информационных слов и накопителя избыточных слов, а также дЬа блока ключей и бло мажоритарной обработки, введены анализатор искаженных слов и сумматор, при этом выход входного декодера через анализатор исксикенных слов подключен к входам первого и второго блоков ключей и к одному из входов блока мажоритарной обработки,к другому входу которого подключены выходы первого и второго блоков ключей через сумматор, а выходы блока мажоритарной обработки яодключены соответственно к управляккцему входу вхо ного декодера и к соответствующему входу анализатора искаженных слов, другие выходы которого подключены соответственно к входам накопителя информационных слов и накопителя избыточных слов, причем накопитель информационных слов, накопитель избыточных слов объединены по одному из входов, а их выходы подключены к соответствующим входам первого и второго блоков ключей.

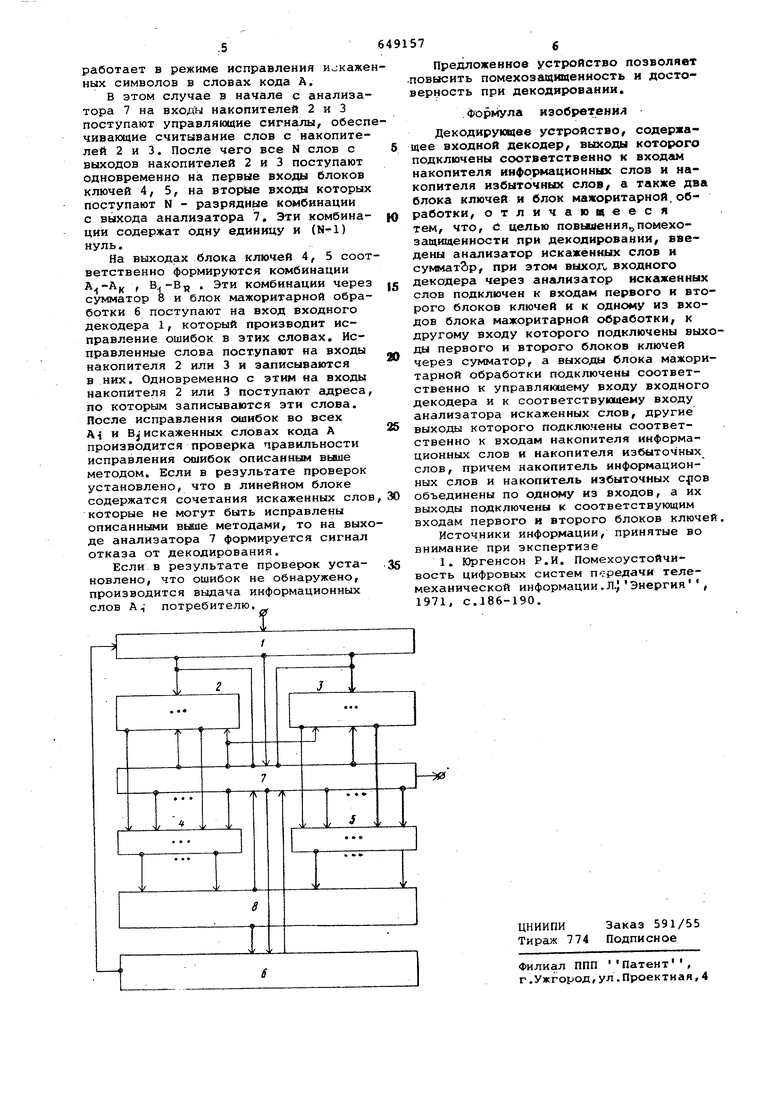

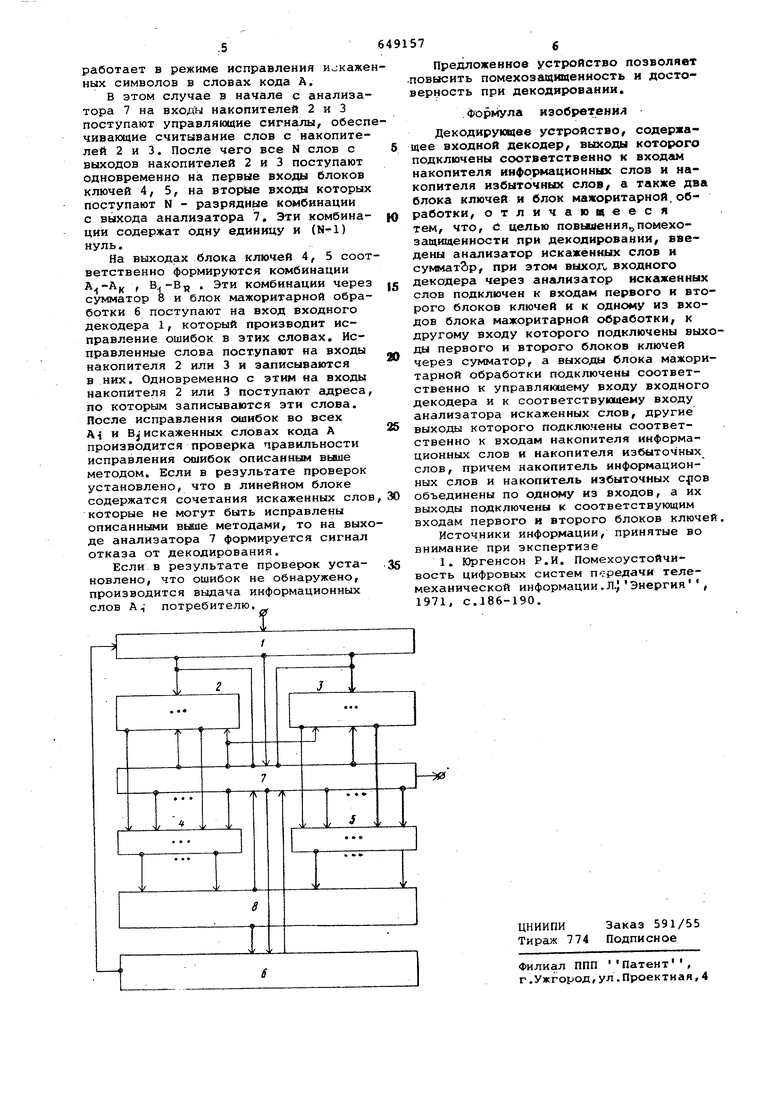

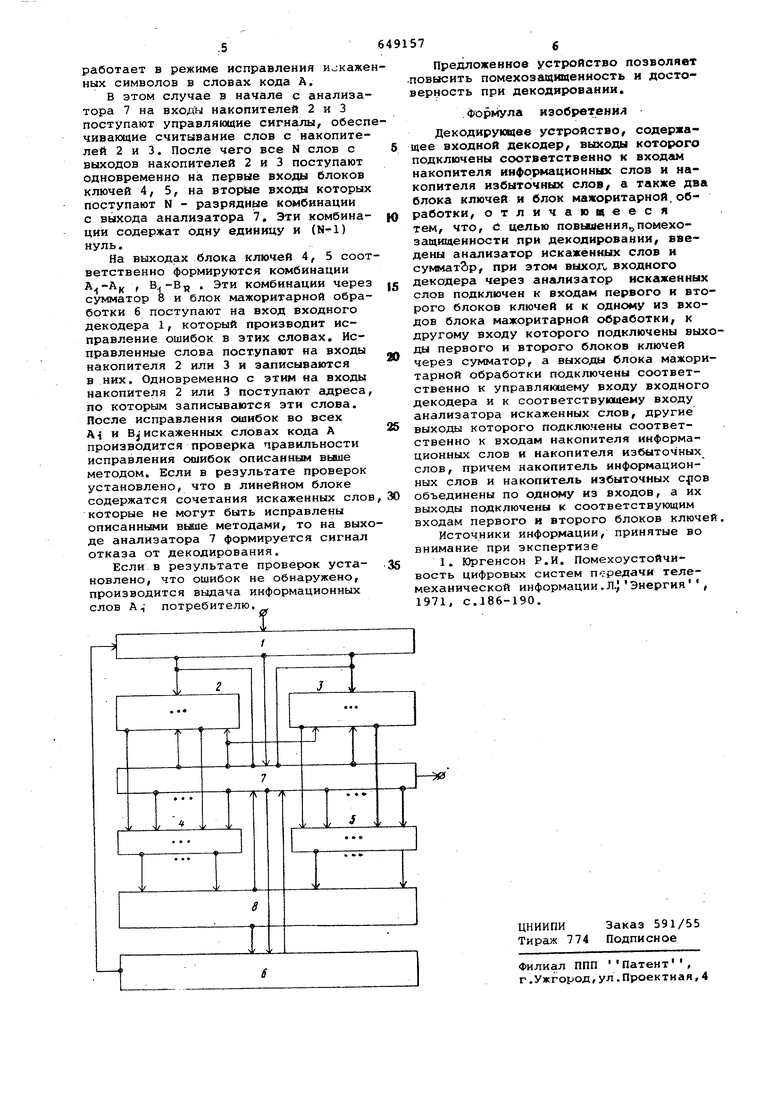

На чертеже изображена структурная электрическая схема предложенного устройства.

Декодирующее устройство- содержит входной декодер 1, выходы которого подключены соответственно к входам накопителя 2 информационных слов и накопителя 3 избыточных, слов, а также два блока ключей 4,5 и блок мажоритарной обработки 6, кроме того анализатор 7 искаженных слов и сумматор при этом выход входного декодера 1 через анализатор 7 искаже:{ных слов подключен к входам первого и второго блоков к.шочей 4,5 и к одному из входов блока мажоритарной обработки 6, к другому входу которого подключены выход

первого и второго блоков ключей 4, 5 через сумматор 8, а выходы блока мажоритарной обработки б подключены соответственно к управлякндему входу входно го дбкодера 1 и к соответствующему входу анализатора 7 искаженных слов, другие выходы которого подключены соответственно к входам наколителя 2 информационных слов и накопителя 3 избыточных слЬв причем накопитель 2 информационных слов и накопитель 3 избыточных сло объединены по одному из входов, а их выходы подключены к соответствуквдим входам первого и второго блоков ключей 4, 5,

Декодирукядее устройство работает следующим образом.

Информация с выхода дискретного канала связи поступает на входной декодер1, Инофрмационные слова А и и3 5ыточные слова Bj с выходов входного декодера 1 поступают соответственно на входы накопителей 2 и 3 и запоминаются в них. Сигналы отметок ошибок, формируемые входным декодером 1 при приеме .слов и В с ошибками, обнаруживаемыми входным декодером 1, поступают на анализатор 7 и запоминаются в нем,

После приема К - информационных А и R избыточных Bj слов, образующих линейный блок кода АВ, производится анализ правильности приема слов принятых входным декодером 1 кода А без обнаруженных ошибок, В этом случа на выходе анализатора 7 формируется управляющий сигнал, который поступает на входы накопителей 2 и 3, После чего все слов линейного блока с выходов накопителей 2 и 3 поступают на входы блоков ключей 4, 5. Одновременно с этим на другие входы блоков , ключей 4, 5 поступают с анализатора 7 управляющие сигналы в виде N -разрядных комбинаций ,

В результате на выходах блоков ключей 4, 5 формируются слова А и В, которые поступают на входы сумматора 8, Результируняций сигнал с выхода сумматора 8 поступает на вход анализатора 7, который определяет наличие единиц в Пд - разрядных результирующих комбинациях. Если в результате проверок все результируквдие Ид -раз-. рядные комбинации не содержат единиц, то это указывает на то, что в словах, принятых входным декодером 1, не содержится ошибок, которые не были обнаружены этим входным декодером 1, В случаях, если в результирующих комбинациях содержатся единицы, это указывает на наличие необнаруженных входным декодером 1 ошибок в словак кода Ai В этом случае, если возможно, производится попытка локализовать искаженное слово или слова для их дальнейшего исправления. Если это невозможно, то исправление ошибок в искаженном слове или словах производится на дальнейших этапах декодирования.

Если число искаженных слов в линейном блоке меньше или равно К + 1, то производится исправление этих слов методами решения линейных уравнений, В этом случае возможно полное или частичное исправление искаженных слов,

В этом случае в начале с анализатора 7 на входы накопителей 2 и 3 поступают управлякйцие сигналы. После чего Bce.N слов считываются с этих накопителей 2, 3 и поступают на входы блоков ключей 4, 5, на другие вход которых поступают N - разрядные комбинации, каждая из которых содержит по {Д-1) единиц, В результате на выходе сумматора 8 формируется исправленное Пд - разрядное слово кода А, Одновременно с этим с анализатора 7 на входы накопителей 2 или 3 поступают сигналы, указывающие адрес, по которому записывается исправленное слово. Исправленное слово с выхода сумматора 8 через анализатор 7 поступает на входы накопителя 2 или 3,

В случаях частичного исправления искаженных слов или, когда число искаженных слов в линейном блоке больше или равно К + 2, исправление производится методами мажоритарного декодирования с выборкой по большинству,

В начале с выхода анализатора 7 на входы накопителей 2 и 3 поступает управляивдий сигнал, по которому все слова с этих накопителей 2, 3 поступают на входы блоков ключей 4,5, На другие входы этих блоков ключей 4, 5 поступают N - разрядные комбинаций, каждая из которых содержит (Д-1) единиц. Позиции единиц в этих комбинациях соответствуют словам А и BJ, В результате на выходах блоков ключей 4, 5 формируется (Д-1) слов, поступающих на входы сумматора 8,

В результате на выходе сумматора 8 формируются слова, которые поступают на вход блока мажоритарной обработки и запоминаются в нем. Одновременно с записью 3-го и последующих слов в мажритарной обработке блок 6 формирует слово, полученное методом мажоритарного декодирования с выборкой по большинству. Это слово поступает на входной декодер 1 и проверяет,я на наличи обнаруженных ошибок, сигналы о которы поступают в анализатор 7, В случае отсутствия ошибок в этом слове формируется адрес, по которому записывается данное слово в накопитель 2 или 3,

В случае, если при мажоритарном декодировании не происходит исправление слов, на выходе блока мажоритарной обработки 6 формируется сигнал, который поступает на вход анализатора 7, После чего анализатор 7 работает в режиме исправления искаж ных символов в словах кода А. В этом случае в начале с анализа тора 7 на входы накопителей 2 и 3 поступают управляющие сигналы, обес чивающие считывание слов с накопите лей 2 и 3. После чего все N слов с выходов накопителей 2 и 3 поступают одновременно на первые входы блоков ключей 4, 5, на вторые входы которы поступают N - разрядные комбинации с выхода анализатора 7, Эти комбина ций содержат одну единицу и () нуль. На выходах блока ключей 4, 5 соо ветственно формируются комбинации , . Эти комбинации чере сумматор 8 и блок мажоритарной обра ботки 6 поступают на вход входного декодера 1, который производит исправление ошибок в этих словах. Исправленные слова поступают на входы накопителя 2 или 3 и записываются в них. Одновременно с этим на входы накопителя 2 или 3 поступают адреса по которым записываются эти слова. После исправления ошибок во всех At и Неискаженных словах кода А производится проверка правильности исправления ошибок описаннЕЛМ вьаие методом. Если в результате проверок установлено, что в линейном блоке содержатся сочетания искаженных слов которые не могут быть исправлены описаннь 1и выие методами, то на выхо де анализатора 7 формируется сигнал отказа от декодирования. Если.в результате проверок установлено, что ошибок не обнаружено, производится выдача информационных слов потребителю, I Предложенное устройство позволяет .повысить помехозащищенность и достоверность при декодировании. Формула изобретени/1 Декодирующее устройство, содержащее входной декодер, выходы которого подключены соответственно к входам накопителя информационных слов и накопителя избыточных слов/ а также два блока ключей и блок мажоритарной, обработки, отличающееся тем, что, о целью повышення помехозсодгааенностн при декодировании, введены анализатор искаженных слов и сумматор, при этом выход, входного декодера через анализатор искаженных слов подключен к входам первого и второго блоков ключей и к одному из входов блока мажоритарной обработки, к другому входу которого подключены выходы первого и второго блоков ключей через сумматор, а выходы блока мажоритарной обработки подключены соответственно к управлякадему входу входного декодера и к соответствующему входу анализатора искаженных слов, другие выходы которого подключены соответственно к входам накопителя информационных слов и накопителя избыточных слов, причем накопитель информационных слов и накопитель избыточных С{1ов объединены по одному из входов, а их выходы подключены к соответствующим входам первого и второго блоков ключей. Источники информации, принятые во внимание при экспертизе 1. Юргенсон Р.И. Помехоустойчивость цифровых систем п ;редачи телемеханической информации.Л. Энергия , 1971, с.186-190.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исправления ошибок дискретной информации | 1977 |

|

SU690640A1 |

| Устройство для исправления ошибок | 1989 |

|

SU1750061A1 |

| Мажоритарный декодер | 1980 |

|

SU890397A1 |

| Устройство для обнаружения и исправления ошибок в блоках памяти | 1988 |

|

SU1525746A1 |

| АДАПТИВНЫЙ ДЕКОДЕР | 2008 |

|

RU2379833C1 |

| Устройство для приема дискретной информации,закодированной корректирующим кодом | 1984 |

|

SU1172022A2 |

| Устройство для мажоритарного декодирования | 1974 |

|

SU636800A1 |

| Устройство для обнаружения и исправления ошибок | 1990 |

|

SU1785041A1 |

| Устройство для приема и адаптивного мажоритарного декодирования дублированных сигналов | 1982 |

|

SU1073789A1 |

| Мажоритарный декодер | 1980 |

|

SU903887A1 |

Авторы

Даты

1979-02-25—Публикация

1976-02-16—Подача