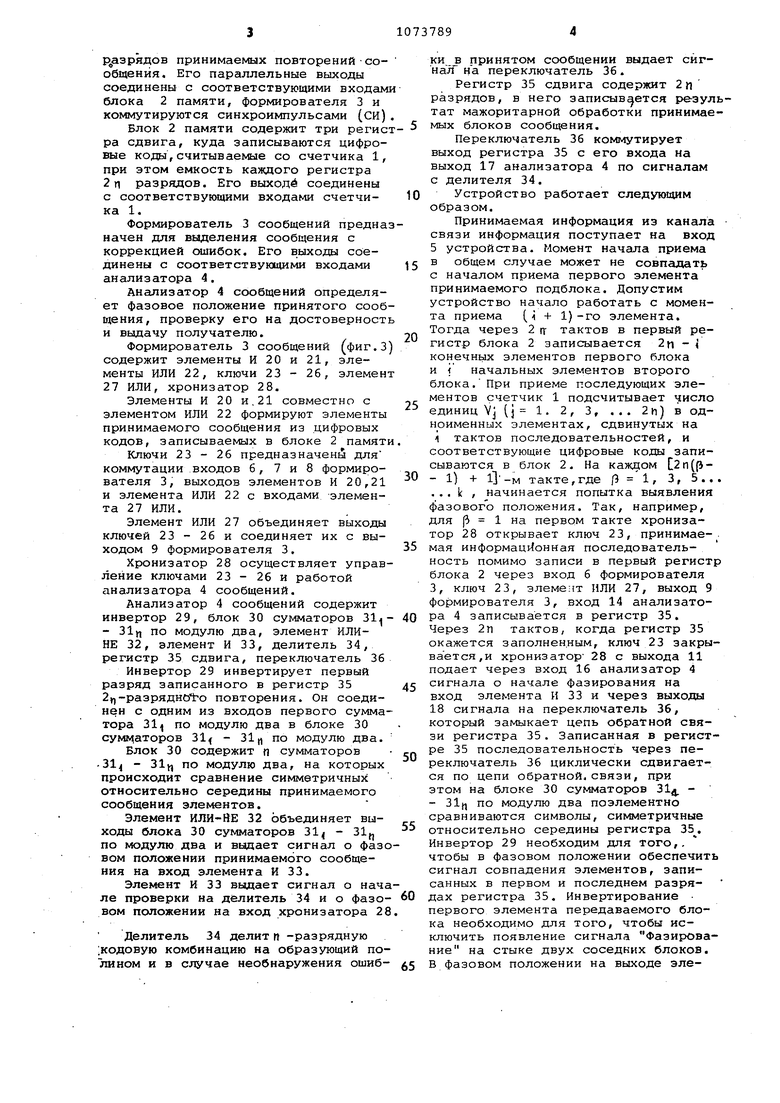

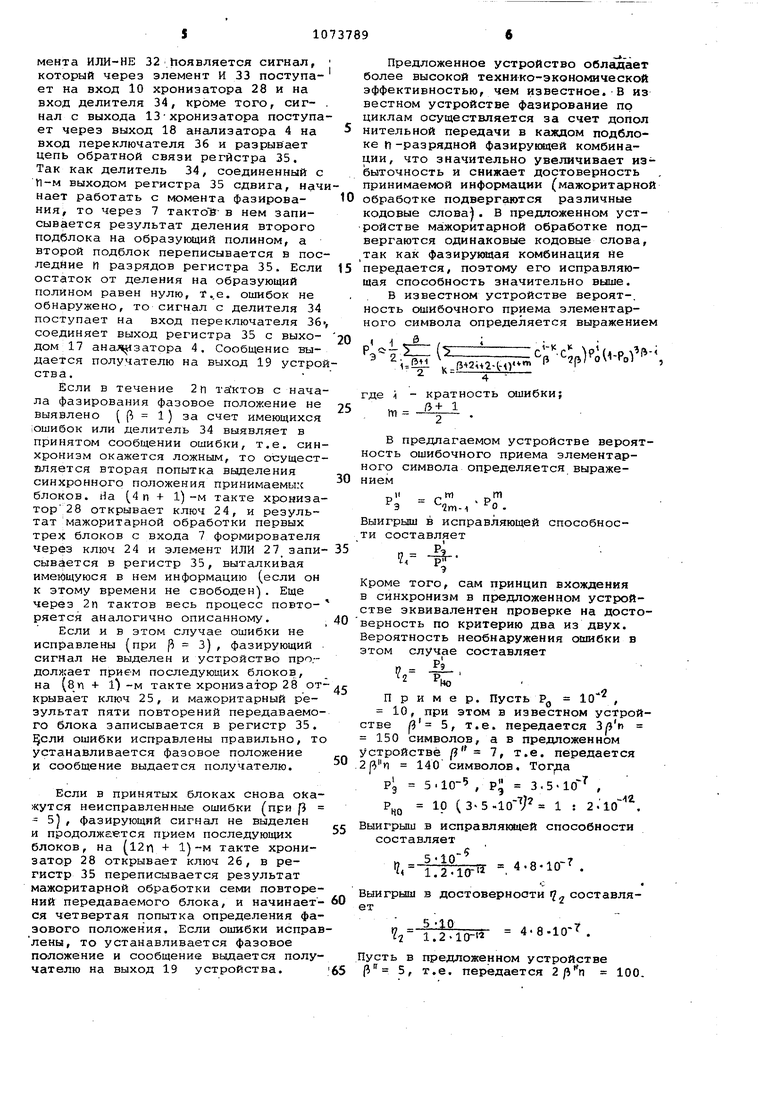

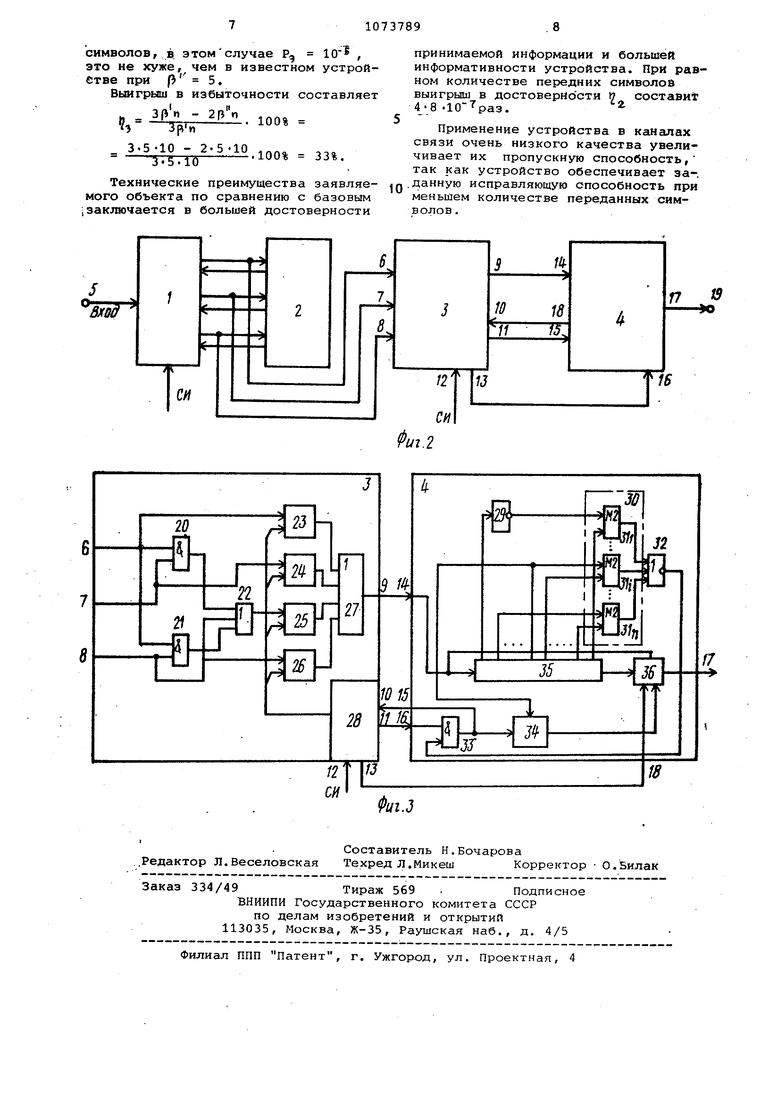

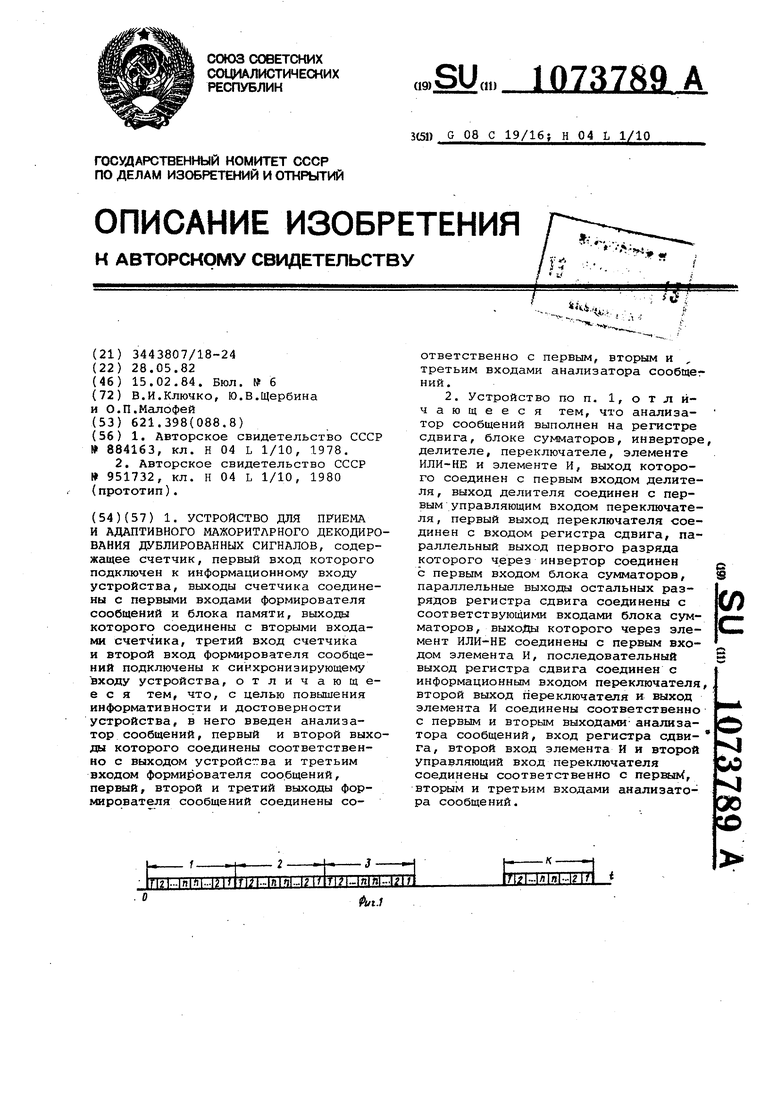

Изобретение относится к телемеха нике и вычислительной технике и может быть использовано в адаптивных системах передачи дискретной информ ции по каналам связи низкого качест ва для коррекции ошибок при многократном дублировании сообщений. Известно устройство для адаптивного мажоритарного декодирования, содержащее ключ, счетчик, накопител и решающий блок, обеспечивающее высокую исправляющую способность l , Однако такое устройство не позволяет осуществлять цикловое фазирова ние, что ограничивает его функциональные возможности, Наиболее близким к предложенному по технической сущности является уст ройство для адаптивного мажоритарного декодирования телемеханических Дублированных сигналов, содержащее последовательно соединенные ключ, счетчик, накопитель (блок памятиj, решающий блок (формирователь сообще ния) , анализатор фазирующего сигнал и селектор начальной фазы, при этом выход селектора начальной фазы соединен с одним из входов решающего блока, один из выходов которого сое динен с входом ключа, а входы соединены с соответствующими входами счет чика и накопителя. В данном устройстве последовател но Лринимаемые блоки, состоящие из одного фазирующего и двух информацио ных сигналов равной длины, накапливаются и мажоритарно складываются, а затем по выделенному фазирующему сигналу отыскивается фазовое положение 2J . . Недостатком данного устройства является большая избыточность и низ кая достоверность принимаемой инфор мации . Цель изобретения - повышение информативности и достоверности устрой ства. Поставленная цель достигается тем, что в устройство дпя приема и а даптивного мажоритарного декодирования дублированных сигналов, содержащем счетчик, первый вход которого подключен к информационному входу устройства, выходы счетчика соединены с первыми входами формирователя сообщения и блока памяти, выходы которого соединены с вторыми входами счетчика, третий вход счетчи ка и второй вход формирователя сообщения подключены к синхронизирующему входу устройства, введен анализатор сообщений, первый и второй выходы которого соединены соответствен но с выходом устройства и третьим входом формирователя сообщений, перг вый, второй и третий выходы формирователя сообщений соединены соответственно с первым, вторым и третьим входами анализатора сообщений. Кроме того, анализатор сообщений выполнен на регистре сдвига, блоке сумматоров, инверторе, делителе, переключателе, элементе И-НЕ и элементе И, выход которого соединен с первым входом делителя, выход делителя соединен с первым управляющим входом переключателя, первый вход переключателя соединен с входом регистра сдвига, параллельный выход первого разряда которого через инвертор соединен с первым входом блока сумматоров, параллельные выходы остальных разрядов регистра сдвига соединены с соответствующими входами блока сумматоров, выходы которого через элемент ИЛИНЕ соединены с первым входом элемента И, последовательный выход регистра сдвига соединен с информационным входом переключателя, второй Выход переключателя и выход элемента И соединены соответственно с первым и вторым выходами анализатора сообщений, вход регистра сдвига, второй вход элемента. И и второй управляющий вход переключателя соединены соответственно с первым, вторым и третьим входами анализатора сообщений. На фиг. 1 представлена временная диаграмма, поясняющая порядок повторения сообщения; на фиг. 2 - структурная схема устройства; на фиг. 3функциональная схема формирователя сообщений и анализатора сообщений. Один сеанс передачи включает k одинаковых блоков, каждый из которых состоит из двух подблоков: исходного сообщения, закодированного избыточны - ( п , k ) кодом , и его зеркального относительно середины отображения , при этом младший разряд первого подблока инвертируется. Величина k определяется качеством используемого канала связи и заданной помехоустойчивостью. Для каналов очень низкого качества, на которые рассчитано предлагаемое устройство, величина k выбирается достаточно большой. В рассматриваемом примере k 7. Устройство (фиг. 2) содержит счетчик 1, блок 2 памяти, формиро-. ватель 3 сообщений и анализатор 4 сообщений, вход 5 счетчика, первые входы б, 7 и 8,первый выход 9, третий вход 10, второй выход 11, второй вход 12, третий выход 13 формирователя, первый 14, второй 15 и третий 16 вхо,ды, первый 17 и второй 18 выходы анализатора, выход 19 устройства. Счетчик 1 в рассматриваемом варианте содержит три двоичных разряда и предназначен для подсчета числа V принятых единиц для одноименных , р азрядов принимаемых повторений-сообщения. Его параллельные выходы соединены с соответствующими входам блока 2 памяти, формирователя 3 и коммутируются синхроимпульсами (си) Блок 2 памяти содержит три регис ра сдвига, куда записываются цифровые коды, считываег Фле со счетчика 1, при этом емкость каждого регистра 2п разрядов. Его выходи соединены с соответствующими входами счетчика 1. Формирователь 3 сообщений предна начен для выделения сообщения с коррекцией сяиибок. Его выхохи соединены с соответствующими входами анализатора 4. Анализатор 4 сообщений определяет фазовое положение принятого сооб щения, проверку его на достоверност и выдачу получателю. Формирователь 3 сообщений (фиг.З содержит элементы И 20 и 21, элементы ИЛИ 22, ключи 23 - 26, элемен 27 ИЛИ, хронизатор 28. Элементы И 20 и,21 совместно с элементом ИЛИ 22 формируют элементы принимаемого сообщения из цифровых кодов, записываемых в блоке 2 памят Ключи 23-26 предназначены для коммутации входов 6, 7 и 8 формирователя 3, выходов элементов И 20,21 и элемента ИЛИ 22 с входами элемента 27 ИЛИ. Элемент ИЛИ 27 объединяет выходы ключей 23 - 26 и соединяет их с выходом 9 формирователя 3. Хронизатор 28 осуществляет управ ление ключами 23 - 26 и работой анализатора 4 сообщений. Анализатор 4 сообщений содержит инвертор 29, блок 30 сумматоров 31 - 31ц по модулю два, элемент ИЛИНЕ 32, элемент И 33, делитель 34, регистр 35 сдвига, переключатель 36 Инвертор 29 инвертирует первый разряд записанного в регистр 35 2,-разряднсЛ-о повторения. Он соединен с одним из входов первого сумма тора 31 по модулю два в блоке 30 сумматоров 31( - 31 по модулю два. Блок 30 содержит п сумматоров -31 - 31, по модулю два, на которых происходит сравнение симметричных относительно середины принимаемого сообщения элементов. Элемент ИЛИ-ЙЕ 32 объединяет выходы блока 30 сумматоров 314 по модулю два и выдает сигнал о фаз вом положении принимаемого сообщения на вход элемента И 33. Элемент И 33 выдает сигнал о нач ле проверки на делитель 34 и о фазо вом положении на вход хронизатора 2 Делитель 34 делит rt -разрядную кодовую комбинацию на образующий полином и в случае необнаружения ошибки в принятом сообщении выдает сигнал на переключатель 36. Регистр 35 сдвига содержит 2 п разрядов, в него записывается результат мажоритарной обработки принимаемых блоков сообщения. Переключатель 36 коммутирует выход регистра 35 с его входа на выход 17 анализатора 4 по сигналам с делителя 34. Устройство работает следующим образом. Принимаемая информация из канала связи информация поступает на вход 5 устройства. Момент начала приема в общем случае может не совпадать с началом приема первого элемента принимаемого подблока. Допустим устройство начало работать с момента приема (i + 1)-го элемента. Тогда через 2 гг тактов в первый регистр блока 2 записывается 2п - конечных элементов первого блока и 1 начальных элементов второго блока. При приеме последующих элементов счетчик 1 подсчитывает число единиц Vj (j 1, 2, 3, ... 2n) в одноименных элементах, сдвинутых на 1 тактов последовательностей, и соответствующие цифровые коды записываются в блок 2. На каждом 2п(р-1) + такте, где /3 1, 3, 5... ... k , начинается попытка выявления фазового положения. Так, например, для fi 1 на первом такте хронизатор 28 открывает ключ 23, принимаемая информац1 онная последовательность помимо записи в первый регистр блока 2 через вход 6 Формирователя 3, ключ 23, элемент ИЛИ 27, выход 9 формирователя 3, вход 14 анализатора 4 записывается в регистр 35, Через 2п тактов, когда регистр 35 окажется заполненным, ключ 23 закрывается, и хронизатор- 28 с выхода 11 подает через вход 16 анализатор 4 сигнала о начале фазирования на вход элемента И 33 и через выходсы 18 сигнала на переключатель 36, который замыкает цепь обратной связи регистра 35. Записанная в регистре 35 последовательность через переключатель 36 циклически сдвигается по цепи обратной.связи, при этом на блоке 30 сумматоров 314. -31f, по модулю два поэлементно сравниваются символы, симметричные относительно середины регистра 35. Инвертор 29 необходим для того,. чтобы в фазовом положении обеспечить сигнал совпадения элементов, записанных в первом и последнем разрядах регистра 35. Инвертирование первого элемента передаваемого блока необходимо для того, чтобы исключить появление сигнала Фазирование на стыке двух соседних блоков. В фазовом положении на выходе элемента ИЛИ-НЕ 32 появляется сигнал, который через элемент И 33 поступает на вход 10 хрониэатора 28 и на вход делителя 34, кроме того, сигнал с выхода 13-хронизатора поступает через выход 18 анализатора 4 на вход переключателя 36 и разрывает цепь обратной связи регистра 35. Так как делитель 34, соединенный с П-м выходом регистра 35 сдвига, начинает работать с момента фазироваНИН, то через 7 тактой- в нем записывается результат деления второго подблока на образующий полином, а второй подблок переписывается в последние ц разрядов регистра 35. Если остаток от деления на образующий полином равен нулю, т..е. ошибок не обнаружено, то сигнал с делителя 34 поступает на вход переключателя 36соединяет выход регистра 35 с выходом 17 aHaJ kjfsaTopa 4. Сообщение выдается получателю на выход 19 устройства.

Если в течение 2п тактов с начала фазирования фазовое положение не выявлено ( ( 1 ) за счет имеющихся Ошибок или делитель 34 выявляет в принятом сообщении ошибки, т.е. синхронизм окажется ложным, то осуществляется вторая попытка выделения синхронного положения принимаемых блоков. На (4п + 1)-м такте хронизатор28 открывает ключ 24, и результат мажоритарной обработки первых трех блоков с входа 7 формирователя через ключ 24 и элемент ИЛИ 27 записывается в регистр 35, выталкивая имейщуюся в нем информацию (если он к этому времени не свободен). Еще через 2п тактов весь процесс повторяется аналогично описанному.

Если и в этом случае ошибки не исправлены {при р З), фазирующий сигнал не выделен и устройство про,дол)сает прием последующих блоков, на (BVI + 1 -м такте хронизатор 28 открывает ключ 25, и мажоритарный результат пяти повторений передаваемого блока записывается в регистр 35. сли ошибки исправлены правильно, то

устанавливается фазовое положение и сообщение выдается получателю.

Если в принятых блоках снова окажутся неисправленные ошибки (при f - 5j, фазирующий сигнал не выделен и продолжается прием последующих блоков, на (l2n + 1)-м такте хронизатор 28 открывает ключ 26, в регистр 35 переписывается результат мажоритарной обработки семи повторений передаваемого блока, и начинается четвертая попытка определения фазового положения. Если ошибки исправлены, то устанавливается фазовое положение и сообщение выдается получателю на выход 19 устройства.

Предложенное устройство обладает более высокой технико-экономической эффективностью, чем известное. В из вестном устройстве фазирование по циклам осуществляется за счет допол нительной передачи в каждом подблоке п -разрядной фазирукяцей комбинации, что значительно увеличивает избыточность и снижает достоверность принимаемой информации (мажоритарной обработке подвергаются различные кодовые слова). В предложенном устройстве мажоритарной обработке подвергаются одинаковые кодовые слова, так как фазиру т«ая комбинация не переедается, поэтому его исправляющая способность значительно выше.

В известном устройстве вероят-. ность ошибочного приема элементарного символа определяется выражением

3

(- -с;«с- 1,;,.р„,.где - кратность ошибки;

В предлагаемом устройстве вероятность ошибочного приема элементарного символа определяется выражением

к м т

э - Sm-1 РО.

Выигрыш в исправляющей способности составляет

«. 4Кроме того, сам принцип вхождения в синхронизм в предложенном устройстве эквивалентен проверке на достоверность по критерию два из двух. Вероятность необнаружения ошибки в этом случае составляет

„ Р9 2- Г

,-2

Пример. Пусть Рд 10 , 10, при этом в известном устройстве 5, т.е. передается 150 символов, а в предложенном устройстве р 1, т.е. передается 140 символов.

РЭ 5.10-5 р« 3. ,

Р..- 10 (3-5-10 / 1 2.10.

пО

Выигрыш в исправлякяцей способности

составляет

„ 510

4.8-10 . « 1.2-10-2

Выигрыш в достоверности составляет

5 -10

-

4-8-10

1.2-10-«

Пусть в предложенном устройстве Р В, т.е. передается 2/in 100.

символов, в этомслучае Р 10 , это не хуже, чем в известном устройстве при р 5.

Выигрыш в избыточности составляет

, ..- 100%

Зрп

З5-IO - 2-510

.100% 33%. 3-5.10

Технические преимущества заявляемого объекта по сравнению с базовым iзаключается в большей достоверности

принимаемой информации и большей информативности устройства. При равном количестве передних символов выигрыш в достоверности 1 состава 48.10-7раз.

Применение устройства в каналах связи очень низкого качества увеличивает их пропускную способность, так как устройство обеспечивает за.данную исправляющую способность при меньшем количестве переданных символов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для адаптивного мажоритарного декодирования телемеханических дублированных сигналов | 1980 |

|

SU951732A2 |

| Устройство для адаптивного мажоритарного декодирования фазирующих сигналов | 1984 |

|

SU1213492A1 |

| Устройство для передачи и приема самосинхронизирующихся кодограмм | 1986 |

|

SU1403379A1 |

| Устройство для декодирования сверточного кода | 1984 |

|

SU1213491A1 |

| Устройство для приема трехкратноповторенных команд телеуправления | 1977 |

|

SU720775A1 |

| Устройство для кодирования и декодирования циклических кодов | 1985 |

|

SU1302440A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ ТОЧНОГО ВРЕМЕНИ | 1990 |

|

RU2033640C1 |

| Декодирующее устройство | 1979 |

|

SU809550A1 |

| Анализатор кодовых комбинаций для устройств передачи информации с решающей обратной связью | 1978 |

|

SU781872A2 |

| Устройство для приема и обработки избыточных сигналов | 1982 |

|

SU1078455A1 |

5 ВхвГ

13

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для адаптивного мажоритарного декодирования телемеханических дублированных сигналов | 1978 |

|

SU884163A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для адаптивного мажоритарного декодирования телемеханических дублированных сигналов | 1980 |

|

SU951732A2 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-02-15—Публикация

1982-05-28—Подача