Изобретение относится к тезшике связи и может использоваться дай построении систем передачи данных для симплексных кангшов связи.

Известно устройство для исправления ошибок дискретной информации, содержащее регистр декодируемой комбинации (ДК) и декодер, выход которого подключен к одному из входов блока сравнения и ко входу первого анализатора, выход которого через первый ключ подключен к входам выходного накопителя, выходы которого через второй ключ подключены к другому входу блока сравнения, выхода которого подключены соответственно к управляющему входу первого ключа и к одному из входов блока управления 11 . .

Однако данное устройство имеет недостаточную точность исправления.

Цель изобретения - повышение точности исправления ошибок дискретной информации.

Для ЭТОГЧ5 в устройство для исправления ошибок дискретной информации, содержащее регистр декодируемой комбинации (ДК) и декодер, выход которого подключен к одному из входов

блока сравнения и к входу первого анёшизатора, выход которого через первый ключ подключен к входам выходного накопителя, .выходы которого через второй ключ подключены к другому входу блока сравнения, выходы . которого подключены соответственно к управляюцему входу первого ключа

0 и к одному из входов блока управления, введены входной накопитель-преобразователь, блок мажоритарной обработки, второй анализатор, регистр второго подблока ДК, коммутатор

г режимов исправления ошибок и дополнктельный ключ, при этом выходы входного накопителя - преобразователя подключены соответственно через регист ДК к входам выходного накопителя, регистра второго подблока

0 ДК и к входам коммутатора режимов исправления йшибок, а через блок мажоритарной обработки - к входам второго анализатора, выходы которого подключены к соответствующим входам

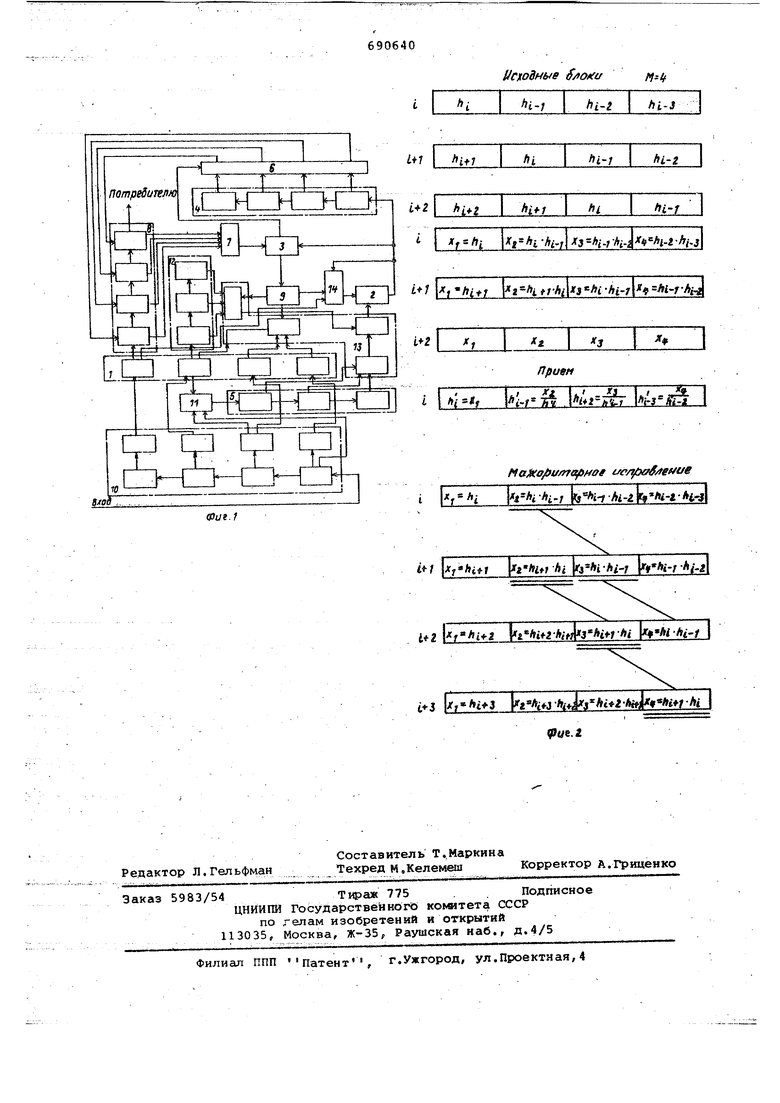

5 комм татора режимов исправления ошибок, к другим входам которого подключены соответственно выходы регистра второго подблока ДК и блока управления, а выход коммутатора режимов исправления ошибок подключен к первому входу декодера, между выходом вторым входом которого включен дополнительный ключ, к управляющим входам которого подключены срртветствующйе выхода блока управления и регистра ДК., На фиг.1 изображена структурная электрическая схема предпожениого устройства на фиг.2 - вид блоков информации. Устройствб для исправления ошибок дискретной информации содержит регистр 1 декодируемой комбинации ДК, декодер 2, блок сравнения 3, анализаторы 4,5, ключи 6,7, выходно накопитель 8, блок управления 9, входной накопитель - преобразовател 10, блок мажбритарной обработки 11, регистр 12 второго подблока ДК, ком мутатор 13 режимов исправления ошибок и дополнительный ключ 14. Предложенное устройство работает следующим образом. Сообщение hj (фиг. 2) передается в канал без изменения. Сообщение h. подвергается стохастическому преобразованию с участием h, . Напри мер, если в качестве стохастическог преобразования используется умножение, то в канал передшотся подблоки X,Hi aCi-hi -hi. и так далее. На приеме подблоки ,/ декодир ются .с размножением ошибки: Ь, «X,; Hc-f-J./fjl -i i/i-Г H,-i . 3rjh.. То есть все подблоки после декодирования, начиная с того, который искажен в и кончая последни подблоком блока, искажаются. Такой подход к кодированию имее ряд достоинств при исправлении оши бок. Вогпервых, искажаются не все подблоки, а только с :едующие за ис каженным в канале, значит, если Х не йскажек,то сообщение данного бл принимается верно, независимо от п ема . Во-вторых, требуемой дл декодирования подблок Xj блока 1 передается, как подблок Х в блоке i-1, поэтому искаженное значение X можно заменить Неискаженным Xt из блока 1-1. В третьих, в соседних передаваемых блоках при такой мето дике кодирования значения подблоко будут повторяться. Например, подбл Хд в блоке 1 равен и равен подблоку Хд блока 1+1, а также подблоку Xj, блока 1+2,Псслёдйеё об стоятельство позволяет воспользова ся операцией мажоритарной выбо{: Ки путем сравнения указанных подблоко Х, Хд, Xj, блоков 1,1+1,1+2 соответственно. Исправление выполняется в три этапа. Принятое сообщение hi блока 1 запоминается. На первом зтапе производится обратное преобразование, в результате из Х|. получаем h. , значение которого сравнивается с h.j, принятым в предыдущем блоке. Если имеет место совпадение этих комбинаций, т6 считается, что оба сообщения h и h приняты верно, им присвгшвается признак того, что они верны. Если совпадение не происходит, определяется h.j из Х, и выполняется сравнение h. и . из блока 1-2, Если Совпадение имеет место, то считается, что h , hf,-| и ht-t приняты в блоке 1 верно, а блок (1-1) GoJi искажен в канале, и в качестве сообщения с номером (1-1) берется h.j из блока 1 и так далее. Если при описанном первом этапе исправления после декодирования блока 1 все время фиксируется несовпадение, то выполняется второй этап. На втором этапе вместо подблоков XjrX используются результаты мажоритарного исправления этих подблоков. Для этой цели при поступлении блоков из канала прокзводйтся мажоритарное исправление и формируются значения результатов мажорирования. Причек( мажорированное значейие Xj, получается в последнем цикле приема блока 1, мажорированное значение Х было получено уже ранее при приеме блока 1-1 и так далее. Итак, на втором этапе для блока 1 выполняется: м Х. а)преобразование h,, - и сравнение h. с предыдущим сообщением hi.i }, б)преобразование Ь.; -« и сравнение с и так далее. Выполнение второго этапа позволяет компенсировать искажения вторых подблоков принятых блоков в случае, когда не или искажены в разных позициях априорно равные им подблоки соседних блоков. В результате снижается вероятность ситуации, когда исправление не происходи±. Если второй этап не обеспечивает исправления, то выполняется третий этап, соответствующий подстановке. На этом этапе используются при декодировании подблоки ранее принятых блоков. Цель третьего эта- па - исправить ошибки, вызванные искаженйем в каждом блоке первых подблоков, не исправляемых мажорированием. Действительно, если Х и Xj блока 1+2 приняты верно, а Х блоков 1 и 1+1 - искажены при неискаженных

Xj этих же блоков, то ошибка исправится следующим образом.

Делим Xjt на Х блока i+2, полученное значение подставляем в качестве Xj, блока 1+1, результат подставляем в Х блока 1 и так далее. Операции этапа повторяются до исчерпания накопителя 8, если, например, в блоке i-1 Х было принято верно, то после деления в блоке на Х| результат сов падает с X, блока i-1, и исправление выполняется.

Принимаемая информация из канала поступает во входной накопитель преобразбватель 10, откуда &гвший та блок переписывается через ключ 14

в декодер 2. Подблоки блоков, занесенных во входной накопитель-преобразователь 10, участвуют в мажоритарно исправлении, после следуххцего блока результат мажорирования переписывается в анализатор 5.

Исправление ошибок выполняется следующим образом. Номер этапа декодирования задается блоком управления 9, открывая один из входов коьмутатЬ ра 13. На первом этапе в декодер 2 поступают по очереди подблоки из регистра 1, очередность выдачи подблоков определяется коммутатором 13, на втором этапе поочередно вьщаются

ангшогично комбинации из ангшизатора 5, порядок выдачи определяет коммутатор 1Э, на третьем этапе используются подблоки из регистра 12, поступающие через коммутатор 13.

Во всех случаях вторая комбингщия участвующая в декодировании, поступает из регистра 1. Это ко й5инация Х|. Рассмотрим первый этап. После деления Х на X, результат декоднровгшия поступает в гшализатор 4, в

блок сравнения .3 и в декодер 2 через ключ 14, Затем делится Xj, поступающая из регистра 1 через коммутатор 13, на результат деления Х. на Х и так далее. Для выполнения сравнения используются ранее принятые сооб111ения из выходного накопителя 8, вызываемое по очереди ё блок сравнения 3 через ключ 7.

Если блок сравнения 3 фиксирует совпадение, то производится исправление сообщений, записанных в выходной накопитель, с комбинациями результата декодирования из анализато через ключ 6.

Второй и третий этапы выполняютс аналогично.

Предложенное устройство обеспечивает более высокую точность исправлния ошибок дискретной информации.

Формула изобретения

Устройство для исправления ошибок дискретной информации, содержащее регистр декодируемой комбинации (ДК и декодер, выход которого подключен к одному из входов блока сравнения и к входу первого анализатора, выход которого через первый ключ подключен к входам выходного накопителя, которого через; второй ключ подключены к другому вхду блока сравнения, выходы которого подк вочены соответственно к управляющему входу первого ключа и к одном из входов блока управления, о т л ич ающее ся тем, что, с целью повышения точности исправления сшибок дискретнсА информации, введены входной накопитель-преобразователь, блок мажоритарн обработки, второй анализатор, регистр второго подблока ДК, коммутатор режимов исправления сшибок и дополнительный ключ, при этом шлхояы входного накопителяпреобразователя подключены.соответственно через pewccTp ДК к входам выходного наколмтеЛя, регистра второго подблока ДК и к входам коммутатора режимов исправления ошибок, а через блок мажоритарной обработки к взсодам второго анализатора, выходы которого подключены к соответствующим входам коммутатора режимов исправления ошибок, к другим входам которого подключены соответственно выходы регистра второго подблока ДК и блока уйравл1внгия, а выход коммутатора режимов исщ авления ошибок подключен г пер11оК у входу декодера, между выходом и вторым входом которого включен дополнительный ключ, к управляквцим входам которого подключены соответствующие выходы блока управления и регистра ДК.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР 551144, кл. И 04 Ь 1/10, 1974.

UcnodHt e (ufifiif

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исправления пакетовОшибОК | 1978 |

|

SU794756A1 |

| Устройство для адаптивного мажоритарного декодирования телемеханических дублированных сигналов | 1980 |

|

SU951732A2 |

| Декодирующее устройство | 1976 |

|

SU649157A1 |

| Устройство для исправления ошибок | 1974 |

|

SU544151A1 |

| АДАПТИВНЫЙ ДЕКОДЕР | 2008 |

|

RU2379833C1 |

| Устройство для исправления ошибок | 1981 |

|

SU997254A2 |

| "Устройство для исправления ошибок в системах передачи дискретной информации | 1977 |

|

SU663120A1 |

| Декодирующее устройство | 1985 |

|

SU1349009A1 |

| Аналоговый декодер кода с ортогональными проверками | 1986 |

|

SU1401614A1 |

| ДЕКОДЕР С ИСПРАВЛЕНИЕМ СТИРАНИЙ | 2008 |

|

RU2379841C1 |

J 1 hji-j i gy i hr ° i

Jry«; t ir ijft f rAt Ifjftt-At-y |у А -гЛ/-г|

I I fj fj-r I z 4tffii X3 f4-fii. k-y Ьнз°ДГ1 I MalKojOu/nafiMoi cfe/(xff/fef ife Д

I

ЧЭме.а

Авторы

Даты

1979-10-05—Публикация

1977-09-17—Подача