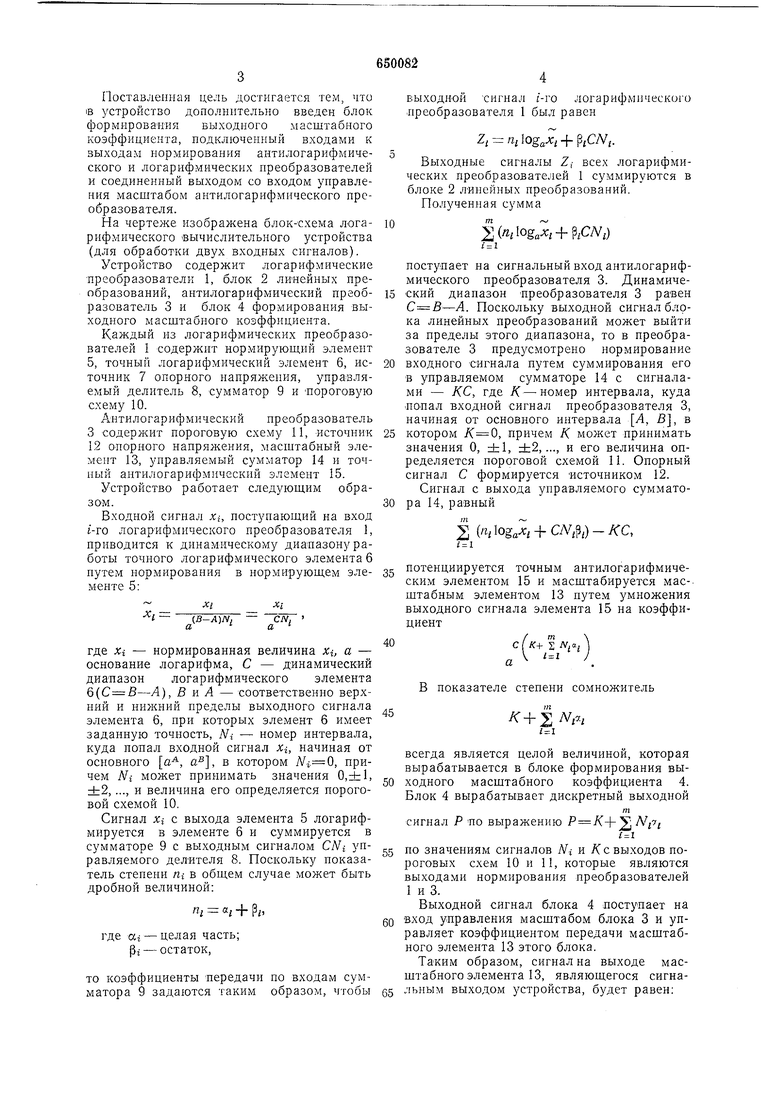

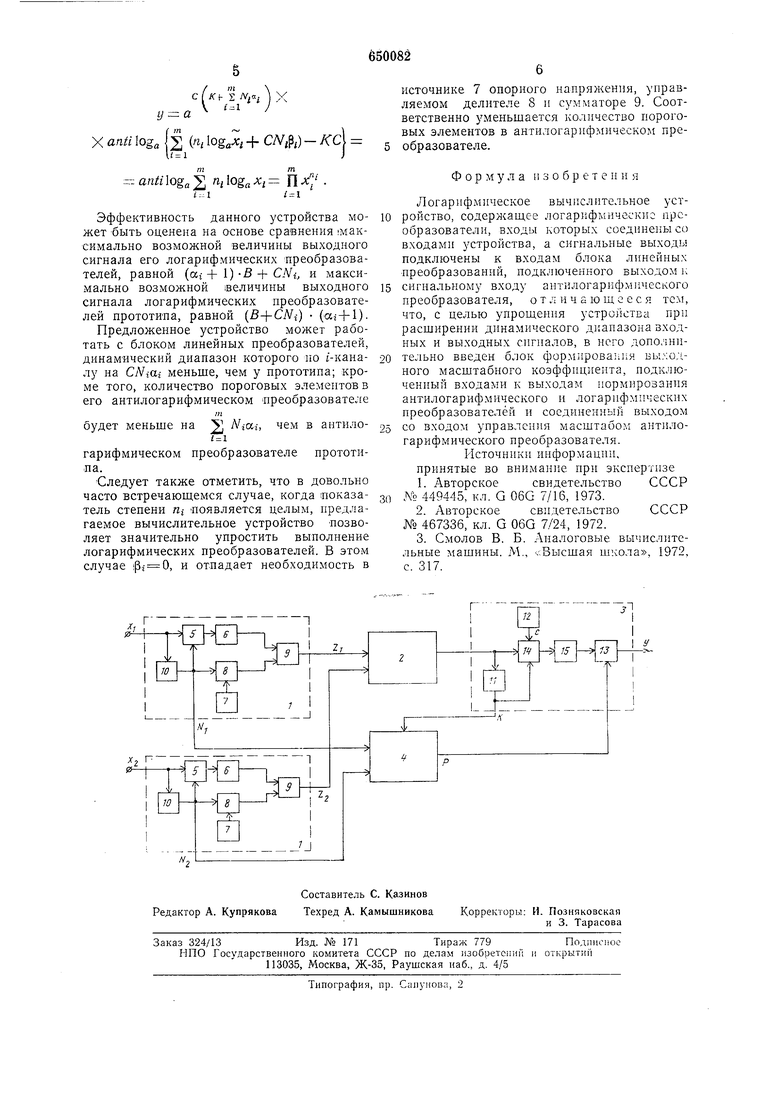

Поставленная цель достигается тем, что iB устройство дополнительно введен блок формирования выходного масштабного коэффициента, подключенный входами к выходам нормирования антилогарифмического и логарифмических нреобразователей и соединенный выходом со входом управления масштабом антилогарифмического преобразователя. На чертеже изображена блок-схема логарифмического -вычислительного устройства (для обработки двух входных сигналов). Устройство содержит логарифмические преобразователи 1, блок 2 линейных преобразований, антилогарнфмический преобразователь 3 и блок 4 формирования выходного масштабного коэффициента. Каждый из логарифмических преобразователей 1 содержит нормируюший элемент 5, точный логарифмический элемент 6, источник 7 опорного напряжения, управляемый делитель 8, сумматор 9 и пороговую схему 10. Антилогарнфмический нреобразователь 3 содержит пороговую схему И, источник 1.2 опорного напряжения, масштабный элемент 13, управляемый сумматор 14 и точный антилогарифмический элемент 15. Устройство работает следуюшим образом. Входной сигнал Xi, поступающий на вход i-ro логарифмического преобразователя 1, приводится к динамическому диапазону работы точного логарифмического элемента 6 путем нормирования в нормирующем элементе 5:

где Хг - нормированная величина Хг, а - основание логарифма, С - динамический диапазон логарифмического элемента 6(), В и А - соответственно верхний и нижний пределы выходного сигнала элемента 6, нри которых элемент 6 имеет заданную точность, Ni - номер интервала, куда попал входной сигнал Хг, начиная от основного а, а, в котором , причем Ni может принимать значения 0,+ , ±2,..., и величина его определяется пороговой схемой 10.

Сигнал Хг с выхода элемента 5 логарифмируется в элементе 6 и суммируется в сумматоре 9 с выходным сигналом CNi управляемого делителя 8. Поскольку показатель степени Лг в общем случае может быть дробной величиной:

«г «/ + Рг.

где «г - целая часть; Рг - остаток,

то коэффициенты передачи но входам сумматора 9 задаются таким образом, чтобы

/

С(ЛГ+ S

. V

В показателе степени сомножитель

всегда является целой величиной, которая

вырабатывается в блоке формирования выходного масштабного коэффициента 4.

Блок 4 вырабатывает дискретный выходной

m

сигнал Р ПО выражению P K- - Ali: i

по значениям сигналов Ni и /С с выходов пороговых схем 10 и И, которые являются выходами нормирования преобразователей 1 и 3.

Выходной сигнал блока 4 поступает на вход управления масштабом блока 3 и управляет коэффициентом передачи масштабного элемента 13 этого блока.

Таким образом, сигнал на выходе масштабного элемента 13, являюшегося сигна. ьныл1 выходом устройства, будет равен: 82 Е;ыходной сигнал г-го логарифмическо1о преобразователя 1 был равен Z,3 « IogJi + p,C/V,. Выходные сигналы Z,- всех логарифмических преобразователей 1 суммируются в блоке 2 линейных преобразований. Полученная сумма m/:(nilOgaXt + iCNi) i l поступает на сигнальный вход антилогарифмического преобразователя 3. Динамический диапазон преобразователя 3 равен . Поскольку выходной сигнал блока линейных преобразований может выйти за пределы этого диапазона, то в преобразователе 3 предусмотрено нормирование входного сигнала путем суммирования его в управляемом сумматоре 14 с сигналами - КС, где К-номер интервала, куда попал входной сигнал преобразователя 3, начиная от основного интервала А, В, в котором , причем К может принимать значения О, ±1, ±2,..., и его величина определяется пороговой схемой 11. Опорный сигнал С формируется источником 12. Сигнал с выхода управляемого сумматора 14, ра;вный I (nilog,x, + CN,,)-KC, потенциируется точным антилогарифмическим элементом 15 и масщтабируется мас-штабным элементом 13 путем умножения выходного сигнала элемента 15 на коэффициент

| название | год | авторы | номер документа |

|---|---|---|---|

| Антилогарифмический преобразователь (его варианты) | 1982 |

|

SU1053116A1 |

| Логарифмический преобразователь | 1979 |

|

SU790003A1 |

| Аналоговое множительное устройство | 1979 |

|

SU830413A1 |

| Логарифмический преобразователь (его варианты) | 1982 |

|

SU1078442A1 |

| Логарифмический функциональный преобразователь | 1973 |

|

SU488224A1 |

| Четырехквадрантное аналоговое множительное устройство | 1990 |

|

SU1718240A1 |

| Антилогарифмический преобразователь | 1979 |

|

SU822211A1 |

| УСТРОЙСТВО ДЛЯ ВОЗВЕДЕНИЯ В СТЕПЕНЬ | 1999 |

|

RU2175147C2 |

| Аналоговое логарифмическое вычислительное устройство | 1982 |

|

SU1095198A1 |

| Устройство для измерения функции передачи модуляции фотоматериалов | 1986 |

|

SU1381415A1 |

Авторы

Даты

1979-02-28—Публикация

1977-02-03—Подача