тора управляющих импульсов подключены к управляющим входам соответственно седьмого и восьмого ключей, первый, второй и третий выходы генератора управляющих импульсов соединены соответственно с входом инвертора, с BTOpbff входом первого переключателя и с вторым входом второго переключателя, выходы первого и второго переключателей подключены соответственно к управляющим входам четвертого и шестого ключей,,

2. Логарифмический преобразователь, содержащий блок логарифмирования, к входу которого подключены первые выводы первого, второго и третьего ключей, выход блока логари-1)мирования соединен с первым выводом четвертого ключа, первый операционный усилитель, выход которого через пятый ключ подключен к входу первого блока памяти, второй блок памяти и второй операционный усилитель, к неинвертирующему входу которого подключен второй вывод четвертого ключа, шестой ключ, элемент с управляемым сопротивлением, масштабирующий блок, вход которого соединен с вторым выводом второго ключа, выход масштабирующего блока подключен к второму выводу первого ключа, генератор управляющих импульсов, первый выход которого соединен с ;управляющими входами первого и пятого ключей, управляющий вход второго ключа подключен к второму выходу генератора управлягацих импульсов, третий выход которого соединен с управляющим входом третьего ключа, второй вывод которого является информационным входом-выходом логарифмического преобразователя, lepBbivi дополнительным информацион3bw входом которого являемся второй вывод второго ключа, отличающийся тем, что, с целью повышения его точности и расширения функциональных возможностей за C4ST обеспечения антилог.арифмиче.ссого преобразования, в него седьмой,восьмой и девятый ключиf пэрвый второй и третий масглтабные резисторы, блок управления, содержащий инвертор, первый

и второй переключатели, источник сигнала логического нуля, -выход инвертора соединен с первым входом первого переключателя, выход источника сигнала логического нуля соединен с первым входом второго переключателя, блок логарифмирования выполнен обратитьи, выход блока логарифмирования через первый масштабный резистор подключен к инвертирующему входу первого операционного усилителя, выход первого блока памяти через второй масштабный резистор соединен с инвертирующим входом первого операционного усилителя и с первым выводом элемента с управляемым сопротивлением второй вывод которого через шестой ключ подключен к выходу первого операционного усилителя, выход второго операционного усилителя через седьмой ключ подключён к входу второго блока памяти, выход которого соединен с управляющим входом элемента с управляемым сопротивлением инвертирующий вход второго операционного усилителя является вторым дополнительным информационным входо логарифмического преобразователя, информационным входом-ввходом которого является первый вывод восьмого ключа, второй вывод которого соединен с вторым выводом элемента с управляемым сопротивлением, второ и третий выходы генеоаторл управлярщих импульсов подключены к управляющим входам соответственно седьмого и восьмого ключей, инвертирующий вход первого операционного усилителя через последовательно соединенные третий масштабный резистор и девятый ключ подключен к шине нулевого потенциала, первый выход генератора управляющих импульсов соединен с управляющим входом девятого ключа, первый, второй и третий выходы генератора управлякидих импульсов соединены соответственно с входом инвертора, с вторым входом первого переключателя и с вторым входом второго переключателя, выходы второго и первого переключателей подключены соответственно к управляющим входам четвертого и шестого ключей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1981 |

|

SU978159A1 |

| Вычислительное устройство и запоминающий масштабно-суммирующий блок | 1980 |

|

SU1043670A1 |

| Логарифмический аналого-цифровой преобразователь | 1982 |

|

SU1042036A1 |

| Множительное устройств | 1979 |

|

SU824223A1 |

| Логарифмический преобразователь | 1982 |

|

SU1064283A1 |

| Устройство для логарифмирования отношения сигналов | 1982 |

|

SU1112375A1 |

| Устройство для логарифмирования отношения сигналов | 1982 |

|

SU1112374A1 |

| Логарифмический аналого-цифровой преобразователь | 1985 |

|

SU1277146A1 |

| Аналого-цифровой логарифмический преобразователь | 1976 |

|

SU612261A1 |

| Устройство для логарифмирования отношения сигналов | 1982 |

|

SU1112373A1 |

Изобретение относится к устройствам преобразовапЕЯ электрических сигналов по логариф -шчаскому закону и может быть использовано в аналоговых машинах.

Один из известных логарифмических преобразователей содержит логэрифматор, ключевые элементы, блоки памяти, операционные усилители, генератор управляющих импульсов 1j.

5 Известное устройство характеризуется низкой точностью работы.

Наиболее близким к предлагаемому является логарифмический преобразователь, содержащий блок логарифмировния, к входу которого подключены первые выводы первого, второго и третьего ключей вывод первого ключа является первым входом устройства и через масштабирующий блок соединен с вторым выводом второго ключа, второй вывод третьего ключа является вторым входом устройства, выход блока логарифмирования через четвертый ключ соединен с первым входом первого дифференциального усилителя, второй вход которого соединен с выходом первого блока памяти, вход которого через пятый ключ соединен с выходом блока логарифмирования, выход первого дифференциального усилителя подключен к входу элемента с управляемым сопротивлением, выход которого является выходом устройства и подключен к первому входу второго дифференциального усилителя, выход которого через соединенные последовательно шестой ключ и второй блок памяти подключен к управляющему входу элемента с управляемым сопротивлением, к второму входу второго дифференциального усилителя подключен вцход источника опорного напряжения, первый выход генератора управ ляющих импульсов соединен с управляющими входами первого и пятого ключей, управляющие входы второго и шестого ключей подключены к второму выходу генератора управляющих импульсов, третий выход которого соединен с управляющими входами третьего и четвертого ключей 2 .

Недостатками устройства являются невысокая точность за счет большого количества последовательно включенных элементов по цепи преобразования входного сигнала и невозможность обратного преобразования сигналов .

Цель изобретения - повышение точности и расширение функциональных возможностей за счет обеспечения антилогарифмического преобразования.

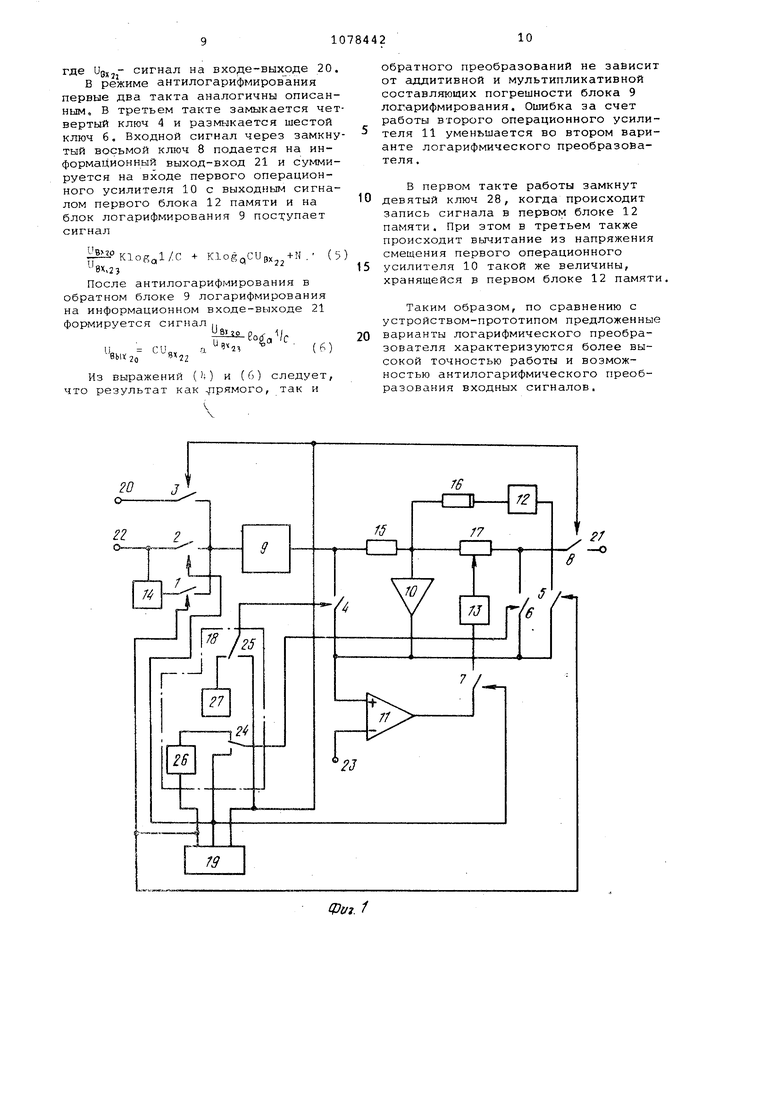

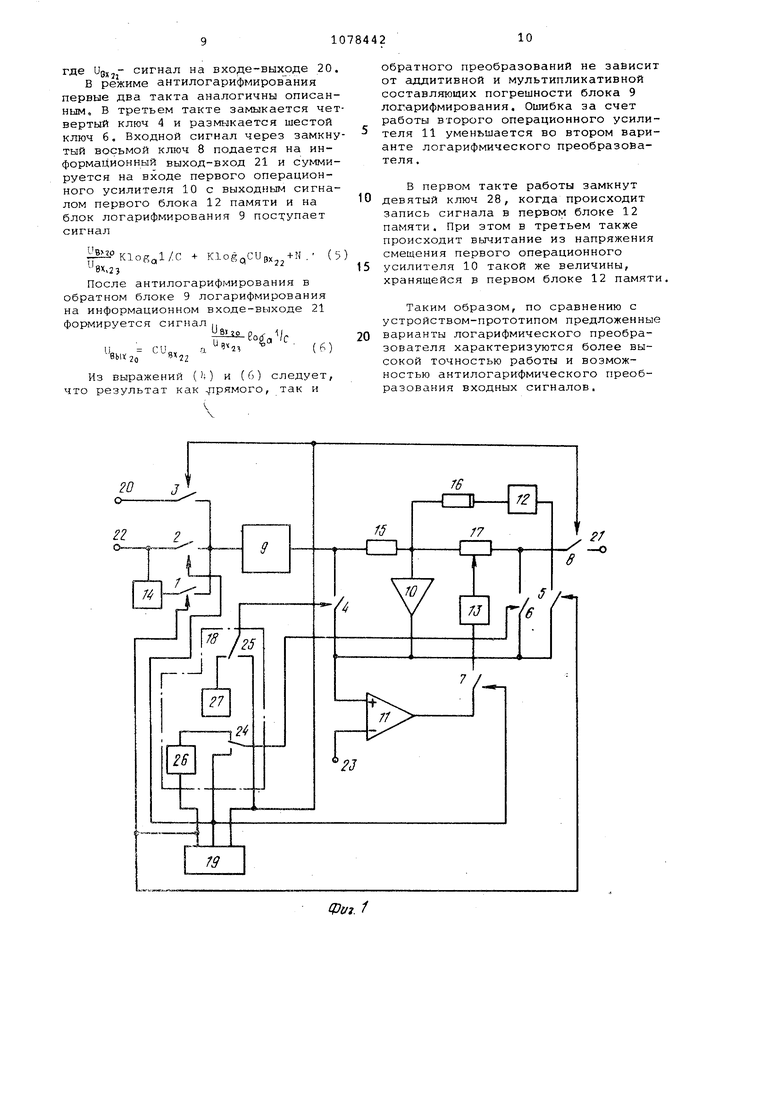

Поставленная цель достигается тем что в логарифмический преобразователь, содержащий блок логарифмирования, к входу которого подключены первые выводы первого, второго и третьего ключей, выход блока логарифмирования соединен с первьлм выводом четвертого ключа, первый операционный усилитель, выход которого через пятый ключ подключен к входу первого блока памяти, второй блок памяти и второй операционный усилитель, к неинвертирующему входу которого подключен второй вывод четве{5того ключа, шестой ключ, элемент с управляемым сопротивлением, масштабирующий блок, вход которого соединен с вторым выводом Второго ключа, выход масштабирующего блока, подключен к .второму выводу первого ключа ,генератор управляющих импульсов, первый выход которого соединен с управляющими входами первого и пятого ключе управляющий вход второго ключа подключен к второму выходу генератора управлякиих импульсов, третий выход которого соединен с управляющим входом третьего ключа, второй выход которого является информационным входом-выходом логарифмического преобразователя, первым дополнительным информационным входом которого является второй вьшод второго ключа введены седьмой и восьмой ключи,первый и второй масштабные резисторы, блок управления, содержащий инвертор, первый и второй переключатели, источник сигнала логического нуля, выход инвертора соединен с первым входом первого переключателя, выход источника сигнала логического нуля соединен с первым входом второго переключателя, блок логарифмирования выполнен обрати 1 JM, выход блока логарифмирования через первый масштабный резистор подключен к инвертирующему входу первого операционного усилителя, выход первого блока памяти через второй масштабный резистор соединен с инвертирующим входом первого операционного усилителя и с первым выводом элемента с управляемым сопротивлением, второй вывод которого через шестой ключ подключен к выходу первого операционного усилителя, выход второго операционного усилителя через седьмой ключ подключен к входу второго блока памяти, выход которого соединен с управляющим входом элемента с управляемым сопротивлением, инвертирующий вход второго операционного усилителя является вторым дополнительным информационным входом логарифмического преобразователя, информационным выходом-входом которого является первый вывод восьмого ключа, второй вывод которого соединен с вторым выводом элемента с управляемым сопротивлением, второй и третий выходы генератора управляющих импульсов подключены к управляющим входам соответственно седьмого и восьмого ключей, первый, второй и третий выходы генератора управляющих импульсов соединены соответственно с входом инвертора, с вторым входом первого переключатели и с вторьм входом второго переключателя, выхо/ ы первого и второго переключателей подключены соответственно к управляющим входам четвертого и шестого ключей. По второму варианту в известный логарифмический преобразователь, со держащий блок логарифмирования, к входу которого подключены первые выводы первого, второго и третьего ключей, выход блока логарифмирования соединен с первым выводом четве того ключа, первый операционный уси литель, выход которого через пятый ключ подключен к входу первого блока памяти, второй блок памяти и второй операционный усилитель, к неинвертирующему входу которого подключен второй вывод четвертого ключа, шестой ключ, элемент с упра ляемым сопротивлением, масштабирующий блок, вход которого соединен с вторым выводом второго ключа, выход масштабирующего блока подключен к второму выводу первого ключа, гене ратор управляющих импульсов, первый выход которого соединен с управ ляющими входами первого и пятого ключей, управляющий вход второго ключа подключен к второму выходу Генератора управляющих импульсов, третий выход которого соединен с управляющим входом третьего ключа, второй вывод которого является информационным входом-выходом логариф мического преобразователя. первЕ тм дополнительным информационныг л входом которого является второй вывод второго ключа, введены седьмой, вос мой и девятый ключи, первый, второй и третий масштабные резисторы, блок управления, содержащий инвертор, первый и второй переключатели,источ ник сигнала логического нуля, выход инвертора соединен с первым входом первого переключателя, выход источн ка сигнала логического нуля соедине с первым входом второго переключате ля, блок логарифмирования выполнен обратимым, выход блока логарифмирования через первый масштабный резяст-эр ,цключен к инвертирующему входу первого операционного усилителя, выход первого блока памяти через второй масштабный резистор соединен с инвертирующим входом первого операционного усилителя и с первым выводом элемента с управляемым сопротивлением, второй ЗЫЕОД которого через шестой ключ подключен к выходу первого операционного усилителя, выход второго операцион ного 5 рилителя через седьмой ключ подключен к входу второго блока па мяти, выход которого соединен с управляющим входом элемента с управ ляемым сопротивлением, инвертирующий вход второго аперацяонного усилителя является вторым дополнительным информ&цконнь входом логарифмического преобразователя, информационньдм : выходом-входом, которого является первый вывод восьмого ключа, второй вывод которого соединен с вторым выводом элемента с управляемым сопротивлением, второй и третий выходы генератора управляющих импульсов подключен к управляющим входам соответственно.седьмого и восьмого ключей, инвертирующий вход первого операционного усилителя через последовательно соединенные третий масштабный резистор и девятый ключ подключен к шине нулевого потенциала, первыйвыход генератора управляющих импульсов соединен с управляющим входом девятого ключа, первый, второй и третий выходы генератора управ ляющих импульсов соединены соответственно с входом инвертора, с вторым входом первого переключателя и с вторым входом второго переключателя, выходы второго и первого переключателей подключены соответственно к управляющим входам четвертого и шестого ключей. На фиг. 1 изображена функциональная схема первого варианта логарифмического преобразователя; на фиг,2 функциональная схема второго варианта логарифмического преобразователя; на фиг. 3 - таблица состояний ключей логарифмического преобразователя . Логарифмический преобразователь (фиг. 1) содержит первый, второй, третий, четверТЕЛй, пятый, шестой, , седьмой и восьмой ключи 1-8, блок 9 логарифмирования, первый 10 и второй 11 операционные усилители, первый 12 и второй 13 блоки памяти, масштабирующий блок 14, первый 15 и второй 16 масштабные резисторы, элемент с управляемым сопротивлением 17, блок 18 управления, гене- ратор 19 управляющих импульсов, информационный вход-выход 20, информационный выход-вход 21, первый 22 и второй 23 дополнительные информационные входы, первый 24 и второй 25 переключатели, инвертор 26, источник 27 сигнала логического нуля. Логарифмический преобразователь (фиг. 2) содержит первый, второй, третий, четвертый, пятый, шестой,, седьмой и восьмой ключи 1-8, блок 9 логарифмирования, первый 10 и второй 11 операционные усилители, первый 12 и второй и блоки памяти, масштабирующий блок 14, первый 15 и второй 16 масштабные резисторы, элемент с управляемым сопротивлением 17, блок 18 управления, генератор 19 управляющих импульсов,информационный вход-выход 20, информационный выход-вход 21, первый 22 и второй 23 дополнительные информационные входы, первый 25 и второй 25 переключатели, инвертор 26, источник 27 сигнала логического нуля, девятый ключ 28, третий масштабн лй резистор 29, шину 30 нулевого потенциала.

Принцип действия логарифмического преобразователя (фиг. 1) заключается в следующем.

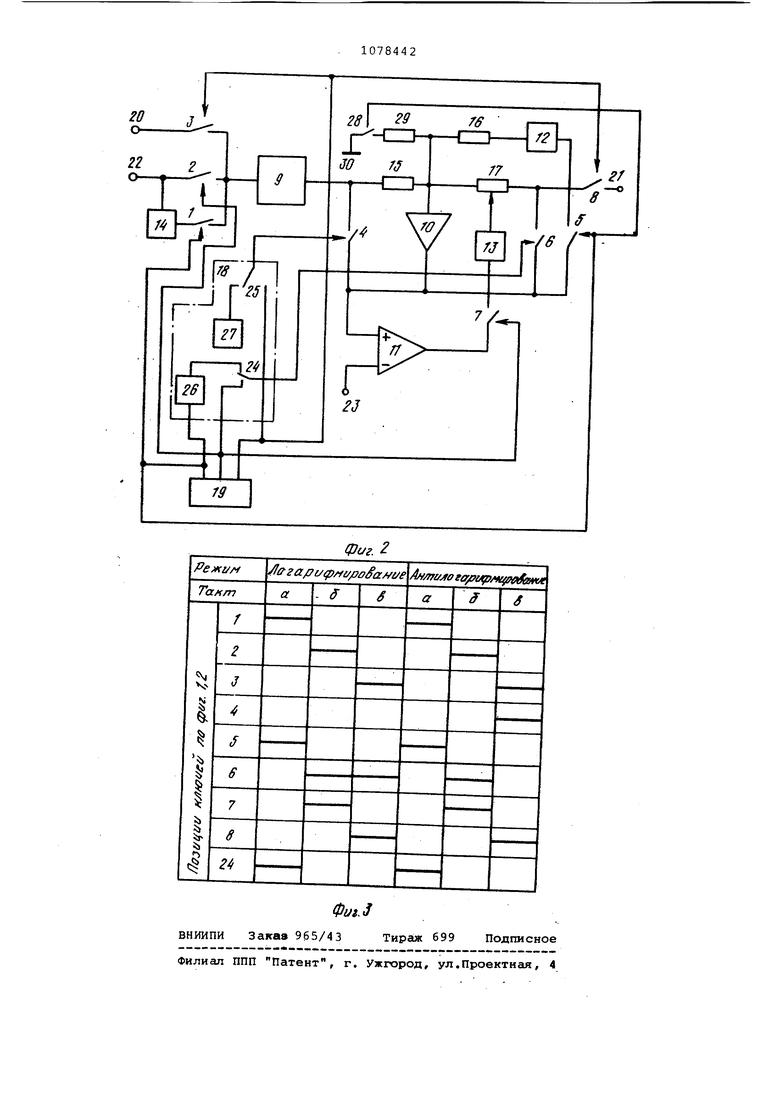

Генератор 19 управляющих импульjCOB формирует управляющие сигналы поочередно на первом, втором и третьем выходах. Положение подвижных контактов первого 24 и второго 25 переключателей соответствуют режиму логарифмирования и обеспечивает разомкнутое состояние четвертого ключа 4 во все такты а,Б , & (фиг. 3) и замкнутое состояние шестого ключа б во второй и третий такты S и Ь . в положении подвижных контактов первого 24 и второго 25 переключателей, противоположном изображенному обеспечивается режим антилогарифмирования, четвертый клю 4 замкнут в третьем такте Ь , а шеетой ключ - во втором такте S (фиг.З

При логарифмическом преобразовании в первый такт а работы генератора 19 управляющих импульсов замкнуты первый и пятый ключи 1 и 5. Сходной сигнал поступает на первый дополнительный информационный вход 22,масштабируется в масштабирующамблоке 14 и через заг пснутый первый ключ 1 поступает на вход блока 9 логарифмирования.

Результат логарифмирования сигнала через первый масштабный резистор 15 поступает на вход первого операционного усилителя 10, цепь обрат ной связи которого в первом такте образуют замкнутый пятый ключ 5,

b(,eo.u,,.(,,,eu,.N.u,.o, где R| - сопротивление элемента с управляемым сопротивление 17; иgj( - сигнал на втором дополнительном информационном вх де 23. По окончании процесса регулирования величины сопротивления элемента с управляемым сопротивлением 17 коэффициент передачи от первого масштабного резистора 15 к выходу второго операционного усилителя 11 равен ,JJg.:3 .. Klopql/C Это значение коэффициента передачи фиксируется во втором блоке 1

первый блок 12 памяти и второй масштабный резистор 16. В первом блоке 12 памяти к концу первого такта фиксируется сигнал

lL6

Kloga ex,

(I) R(

где R, и R|, - сопротивления первого и второго масштабных резисторов 15 и 16;

с - коэффициент подечи маштабного блока 14; Ug - сигнал 1га первом дополнительном информационном входе 22; К, N - мультипликативная и

аддитивная погрешност блока 9 логарифмирования .

Во второй такт S работы генератора 19 управляющих импульсов замкнуты второй, шестой и седьмой ключи 2, б и 7. Входной сигнал через второй ключ 2 поступает на вход блока логарифмирования, сигнал с которого через первый масштабирующий резистор 15 поступает на вход первого операционного усилителя 10. При этом цепь обратной связи образована замкнутым шестым ключом б и элементом с управляемым сопротивлением 17, В течение второго такта работает контур автоматического регулирования коэффициента передачи первого операционного усилителя 10, цепь отрицательной обратной связи которого образуют первый масштабный резистор 15 и элемент с управляемым сопротивлением 17. Условием работы контура является равенство нулю алгебраической суммы входных сигналов второго операционного усилителя 11

(2) памяти и хранится в течение третьего Ь и первого а тактов. В третий такт i работы генератора 19 управляющих импульсов замкнуты третий, шестой и восьмой ключи 3, б и 8, а первый 12 и второй 13 блоки памяти находятся в режиме хранения. Сигнал с информационного входа-выхода 20 через третий ключ 3 поступает на блок 9 логарифмирования. Первый операционный усилитель 10 обеспечивает точное суммирование с выходныг сигналом первого блока 12 памяти. Результирующий сигнал на информационном выходевходе 21 равен 1Г - 2fiUJ И1 7Т, logVl/C °К

где Ugjj- сигнал на входе-выходе 20.

В режиме антилогарифмирования первые два такта аналогичны описанным, В третьем такте замыкается четвертый ключ 4 и размыкается шестой ключ 6. Входной сигнал через замкнутый восьмой ключ 8 полается на информационный выход-вход 21 и суммируется на входе первого операционного усилителя 10 с выходным сигналом первого блока 12 памяти и на блок логарифмирования 9 пост:упает сигнал

:5)

KloggCUBX22+N

После антилогарифмирования в обратном блоке 9 логарифмирования на информационном входе-выходе 21 формируется сигнал ц

ir Eurfa C U си а ()

Из выражений (О и (6) следует, что результат как рямого, так и

V

Обратного преобразований не зависит от аддитивной и мультипликативной составляющих погрешности блока 9 логарифмирования. Ошибка за счет работы второго операционного усилителя 11 уменьшается во втором варианте логарифмического преобразователя,

В первом такте работы замкнут девятый ключ 28, когда происходит запись сигнала в первом блоке 12 памяти. При этом в третьем также происходит вычитание из напряжения смещения первого операционного усилителя 10 такой же величины,

хранящейся в первом блоке 12 памяти,

Таким образом, по сравнению с устройством-прототипом предложенные варианты логарифмического преобразователя характеризуются более высокой точностью работы и возможностью антилогарифмического преобразования входных сигналов.

фаг.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для логарифмированияОТНОшЕНия дВуХ СигНАлОВ | 1979 |

|

SU822210A1 |

| С, 06 G 7/24, 1979 (прототип). | |||

Авторы

Даты

1984-03-07—Публикация

1982-06-23—Подача