изобретение относится к аналоговой вычислительной технике и может быть использовано в различных узлах контроль-информационной аппаратуры.

Известны устройства, работа которых основана на логарифмических способах, позволяющих достичь хорошей точности в широком динамическом диапазоне. В данных устройствах предполагается последовательное соединение трех узлов, а именно логарифмического преобразователя, масштабного с коэффициентом 0,5 и экспоненциального преобразователей i .

Однако к масштабному узлу предъявляются жесткие требования в отношении таких параметров, как напряжение смещения, входные токи операционного усилителя и т.п. по той причине, что они существенно влияют на выходной сигнал экспоненциального преобразователя, а также подобные устройства предполагают использование только термонезависимых узлов.

Наиболее близким к предлагаемому является ансшоговое логарифмическое вычислительное устройство, на основе алгоритма En -ехр; реализующее функцию Р -Ч/-Ь I где X , у , - входные переменные, и содержит три логарифми ческих и один экспоненциальный преобразователя, каждый из которых включает биполярный транзистор и операционный усилитель Температурная завсимость выходного напряжения в данном устройстве исключается в случае идентичности параметров тр1анзисторов изготовленных в одном чипе. Если входы К и у соединить со входным сигналом, а выход соединить со входом t то данное устройство будет реализовать функцию извлечения квадратного корня 23.

Недостатки известного устройствавозрастание погрешности выходного сигнала при малых значениях знаменагеля, а также сужение динамического диапазона входных сигналов при ра(5оте его в качестве делителя.

Цель изобретения - повышение точности аналогового логарифмического вычислительного устройства.

Поставленная цель достигается тем, что в аналоговом логарифмическом вычислительном устройстве, содержггщем четыре операционных усилителя, три масштабных резистора,i два логарифмирующих транзистора, антилогарифмирующий и масштабирующий транзисторы, между инвертирующим входом и выходом первого и второго операционных усилителей включены соответственно коллектор и эмиттер соответствующего логарифмирующего транзистора, инвертирующие входы первого и второго операционных усилителей подключены к первым выходам первого и второго масштабных резисторов, база второго логарифмирующего транзистора подключена к эмиттеру первого логарифмирующего транзистора, база которого подключена к шине нулевого потенциала, соединенной с неинвертирующими входами первого и второго операционных усилителей, коллектор антилогарифмирующего транзистора соединен с инвертирующим входом третьего операционного усилителя который является выходом .устройства, выход второго операционного усилителя подключен к эмиттеру масштабирующего транзистора, база которого соединена с инвертирующим входом и выходом четвертого операционного усилителя, неинвертирующий вход которого соединен с коллектором масштабирующего транзистора и э,миттером антилогарифмирующего транзистора, ба.за которого соединена с неинв ртирующим входом третьего операционного усилителя и шиной нулевого потенциала.

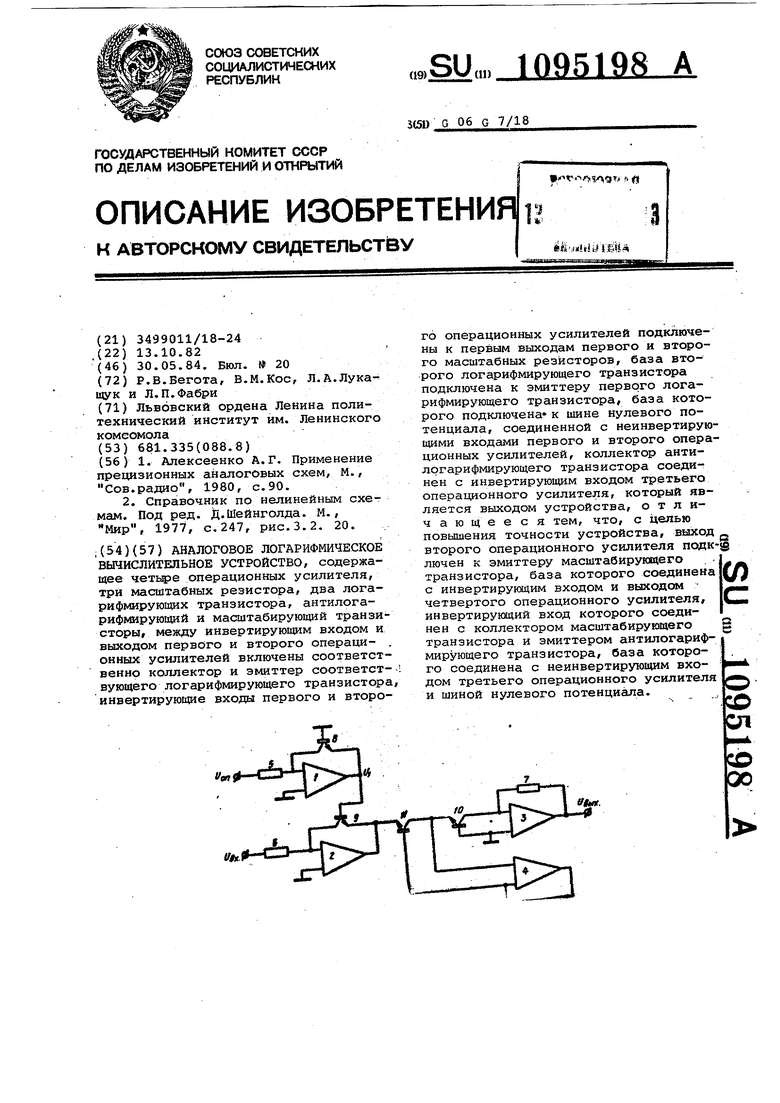

На чертеже представлена блок-схема устройства.

Аналоговое логарифмическое вычислительное устройство содержит четыре операционных усилителя 1-4, три масштабных резистора 5-7, два логарифмирующих транзистора 8 и 9, антилогарифмирующий 10 и масштабирующий 11 транзисторы.

Устройство работает следующим образом.

Входы первого и второго логарифмических преобразователей подключены к опорном} и к входному напряжению соответственно. Напряжение U, равно

-j

U,

где1{, ;-- температурный потенциал

°° первого логарифмирующего , . транзистора 8

51 ток насьицения первого логарифмирующего транзистора 9.

Напряжение U/j равно сумме эмиттер но-базовых потенциалов логарифмирующих те нзисггоров 8 и 9

,.c,,.eJJi.4,b(,en(V

4 a-sa Благодаря глубокой отрицательной обратной связи четвертого операционного усилителя 4 потенциал базы . масштабирующего транзистора 4 практически равен потенциалу его коллектора, поэтому напряжение iJg равно сумме падений напряжений на эмиттерных переходах масштабирующего и антилогарифмических 11 и 10 транзисторов, т.е.

К44

,.en

U

511

Для диапазона коллекторных токов,

для которого можно принять 3,(,(j у;,

f8 l-RI г«V ЧRfeV - « M

,о 1 1Гехр

Параметры транзисторов, изготовленные в одном чипе, мочно считать практически равными между собой,т.е.

Ч

Входное напряжение устройства. равно , иог,, «АО Таким образом, выходной сигнал устройства стзязан с входным сигналом

(2) и (3) получим вырас учетом жение

.- toЧ 1-Ч

S8 S4-sio SM- 5 3

тогда с учетом (,5) получим

Uon-Ue,

gRe35 2(f 20 25 требуемой математической зависимостью и вы к K-J UBX и ® зависит от параметров транзистора Cf и 1 В основу работы схемы предлагаемого устройства положен аЛгоритм Вп -ехр , а не метод неявного реше ния уравнения, что позволяет использовать всё преимущества логарифмических узлов, а именно: хорошую точность, широкий динамический диапазон входных сигналов, простоту и компактность устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое логарифмическое вычислительное устройство | 1983 |

|

SU1137486A2 |

| Множительно-делительное устройство | 1987 |

|

SU1543426A1 |

| Четырехквадратное множительно-делительное устройство | 1987 |

|

SU1474686A1 |

| Вычислительное устройство | 1987 |

|

SU1539798A1 |

| Логарифмическое вычислительное устройство | 1987 |

|

SU1543425A1 |

| Вычислительное устройство | 1985 |

|

SU1282163A1 |

| Вычислительное устройство | 1987 |

|

SU1462364A1 |

| Аналоговый экспоненциальный преобразователь | 1982 |

|

SU1101849A1 |

| Аналоговое множительное устройство | 1976 |

|

SU613333A1 |

| Логарифмический усилитель | 1979 |

|

SU840950A1 |

АНАЛОГОВОЕ ЛОГАРИФМИЧЕСКОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО, содержащее четьфе операционных усилителя, три масштабных резистора, два логарифмирующих транзистора, антилогарифмирующий и масштабирующий транзи сторы, между инвертирующим входом и выходом первого и второго операдионнЕ к усилителей включены соответст венно коллектор и эмиттер соответст вующего логарифмирующего транзистор инвертирующие входы первого и второ го операционных усилителей подключены к первым выходам первого и второго масштабных резисторов, база второго логарифмирующего транзистора подключена к эмиттеру первого логарифмирующего транзистора, база которого подключена к ишне нулевого потенциала, соединенной с неинвертирующими входами первого и второго операционных усилителей, коллектор антилргарифмирующего транзистора соединен с инвертирующим входом третьего операционного усилителя, который является выходом устройства, о т л и- чающееся тем, что, с целью повышения точности устройства, выход второго операционного усилителя псадк- лючен к эмиттеру масштабирующего транзистора, база которого соединена с инвертирующим входом и выходом четвертого операционного усилителя, инвертирукхций вход которого соединен с коллектором масштабирующего g транзистора и эмиттером антилогарифмирующего транзистора, база которого соединена с неинвертирующим входом третьего операционного усилителя и шиной нулевого потенциала.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Алексеенко А.Г | |||

| Применение прецизионных аналоговых схем, М., Сов.радио, 1980, с.90 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Справочник по нелинейным схемам | |||

| Под ред | |||

| Д.Шейнголда | |||

| М., Мир, 1977, с | |||

| Приспособление для картограмм | 1921 |

|

SU247A1 |

| Прибор для промывания газов | 1922 |

|

SU20A1 |

| ; | |||

Авторы

Даты

1984-05-30—Публикация

1982-10-13—Подача