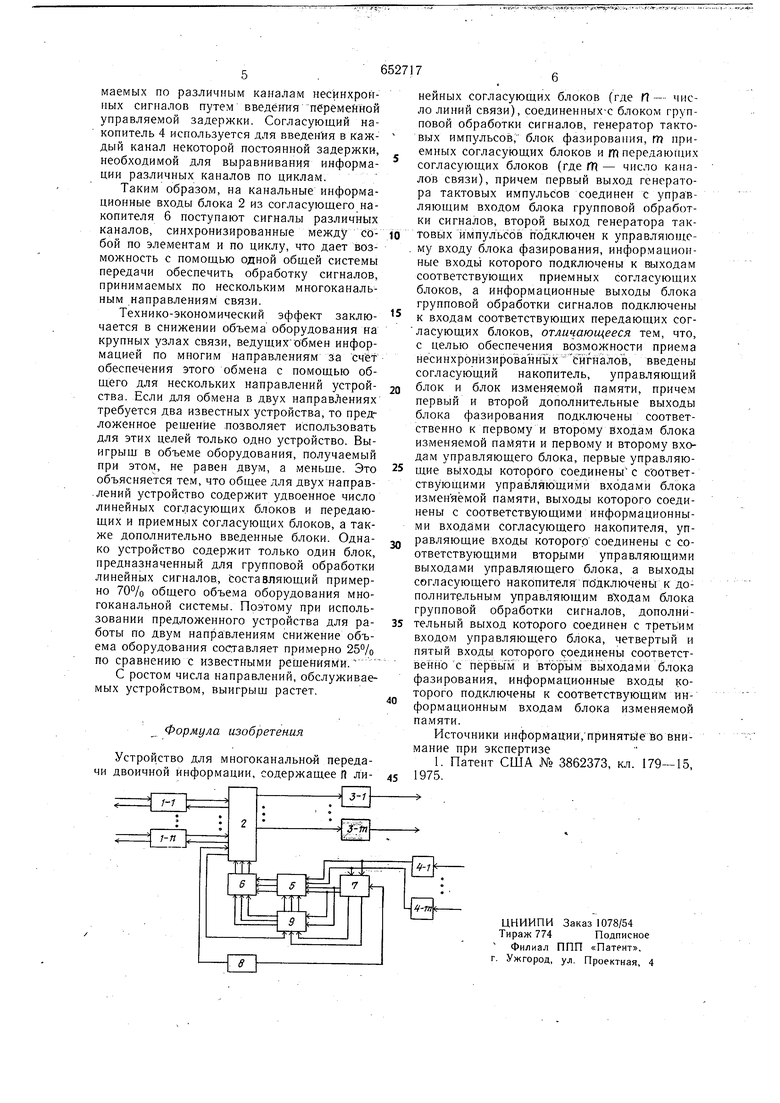

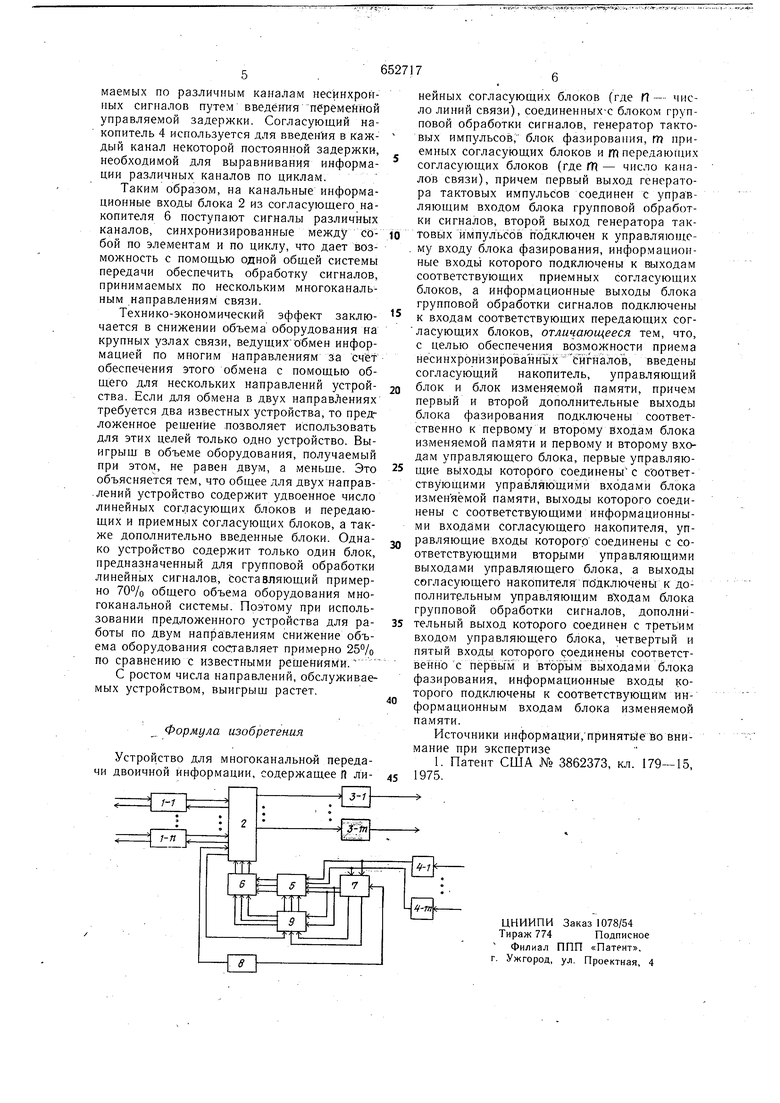

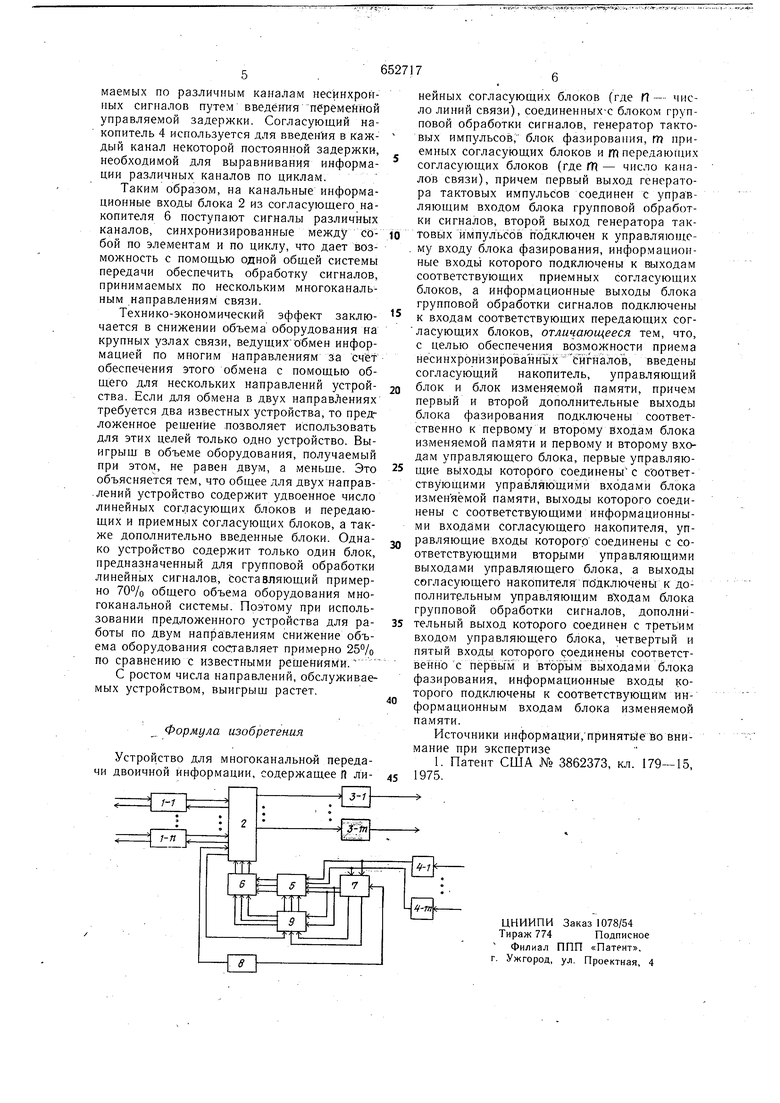

подключенык входам соответстВуюших передающих согласующих блоков, введены согласующий накопитель, управляющий блок и блок изменяемой памяти. Первый и второй дополнительно выходы блока фазирования подключены соответственно к первому и второму входам блока изменяемой памяти и первому и второму входам управляющего блока, первые управляющие выходы которого соединены с соответствующими управляющими входами блока изменяемой памяти, выходьг которого соединены с соответствующими информационными входами согласующего накопителя, управляющие входы которого соединены с соответствующими вторыми управляющими выходами управляющего блока. Выходы согласующего накопителя подключены к дополнительным управляющим входам блока групповой обработки сигналов, дополнительный выход которого соединен с третьим входом управляющего блока, четвертый и пятый входы которого соединены соответственно с первым и вторым выходами 6vTOKa фазирования, информационные входы которого подключены к соответствующим информационным входам блока изменяемой памяти. На чертеже приведена структурная электрическая с.хема устройства. Устройство для многоканальной передачи двоичной информации содержит П линейных согласующих блоков 1-1 - 1-П, входные и выходные линейные информационные цепи которых подключаются через П линейных согласующих блоков 1-1 - 1-П к линейным информационным входам и выходам блока 2, предназначенного для обработки сигналов. Канальные информационные выходы блока 2 соединены с передаточными цепями каналов связи через гт передающих согласующих блоков 3-1-З-ГП.Приемные цепи каналов связи подключены к канальным информационным входам блока 2 через ш приемных согласующих блоков 4- - -4-/Т} и последовательно соединенных блока 5 изменяемой памяти и согласующего накопителя 6, причем информационные входы блока 5 объединены с одноименными входами фазирующего блока 7. Генерйтор 8 тактовых импуЖсбв соединен первым выходом с блоком 2, а вторым выходом - с блоком 7. Первый и второй выходы последнего подключены к одноименным входам блока 5 и управляющего блока 9, а третий и четвертый выходы - к четверто.му и пятому входам управляющего блока 9. Дополнительный выход блока 2 соединен с третьим входом блока 9. Управляющие выходы блока 9 подключены к одноимен-. ным входам согласующего накопителя 6 и блока 5 соответственно. Устройство работает следующим образом. Линейные согласующие блоки 1-1 -1-/7 служат для согласования входных и выходных линейнЕ гх сигналов по уровню соответственно с линейными информационными выходами и входами блока 2. Этот блок на передающей стороне осуществ аяет поочередное обращение к входным цепям линий, поочередную обработку линейных сигналов по заданному алгоритму и, разделение обработанных сигналов таким образом, чтобы определенные линейные сигналы были направлены в заданный канал связи. При этом каждый канал связи соединен с блоком групповой обработки сигналов через свой передающий согласующий блок 3-1-3-т, задачей которого является согласование параметров канала связи с вь1ходом блока 2. На приемной стороне блок 2 выполняет операции, обратные тем, которые были произведены на передающей- стороне. Для этого на соответствующие его канальные информационные входы должны быть поданы синхронизированные между собой сигналы, принимаемые по подключенным к устройству канала.м связи разных направлений, причем на выходах цепей приемка каналов связи указанные сигналы между собой не синхронизированы. Эти сигналы поступают на входы соответствующих приемных согласующих блоков 4-1-4-(Т1, осуществляющих стыковку параметров цепей приема канала связи с информационными входа.ми блока 7 и блока изменяемой памяти 5. Блок 7 обеспечивает фазирование принимаемых сигналов каждого канала по элементам и по циклу, осуществляет синхронизацию блока 5 по тактам каждого канала, и управляющий блок 9 как по тактам, так и по циклам. Управляющий блок 9 осуществляет непрерывное слежение за фазой тактовых импульсов каждого канала относительно эталона, в качестве которого может быть принята тактовая серия одного из принимаемых сигналов, или такты передачи. В случае расхождения (опаздывания или опережения) фазы тактовой серии канала относительно эталонной на величину, превыщающую длительность бита, блок 9 вырабаты- вает соответствующий управляющий сигНал, меняющий адрес ячейки блока 5, из которой производится считывание информации в согласующий накопитель 6. Одновре.менно блок 9 соответствующим образом меняет адрес ячейки, в которую осуществляется запись информации в согласующем накопителе 6. Синхронизация работы блока 9 с тактами работы блока 2 обеспечивается синхронизирующими импульсами, поступающими из последнего на третий вход управляющего блока 9. Таким образом блок 5 совместно с блоком 9 осуществляют синхронизацию прини

| название | год | авторы | номер документа |

|---|---|---|---|

| Дуплексная многоканальная система передачи двоичной информации с временным уплотнением | 1976 |

|

SU593626A1 |

| Устройство для передачи ипРиЕМА диСКРЕТНОй иНфОРМАциипО пАРАллЕльНыМ КАНАлАМ СВязипЕРЕМЕННОй длиНы | 1978 |

|

SU794753A1 |

| Устройство передачи и приема сигналов телеинформации | 1978 |

|

SU698032A1 |

| Многоканальное устройство с временным делением каналов | 1977 |

|

SU617853A1 |

| Устройство для передачи дискретных сигналов | 1984 |

|

SU1277419A1 |

| Устройство цифрового транзита каналов в узлах сети связи | 1985 |

|

SU1320905A1 |

| Многоканальная система для передачи двоичной информации с временным уплотнением | 1976 |

|

SU690639A1 |

| Устройство для передачи и приема дискретной информации по параллельным каналам связи переменной длины | 1989 |

|

SU1658407A1 |

| Многоканальное устройство для передачи и приема дискретной информации | 1985 |

|

SU1279079A1 |

| Устройство цикловой синхронизации | 1985 |

|

SU1358104A1 |

Авторы

Даты

1979-03-15—Публикация

1977-04-04—Подача